Early Verdict

Silicon Motion is on pace to take over the entry-level and mainstream markets again. Very few companies are this far along in controller development for 3D flash, but the SM2258 is nearly ready in the form we tested today. We suspect it will lead the market and increase the number of design wins for the company in late 2016 and early 2017.

Pros

- +

Low cost 4-channel design

- +

Excellent reliability

- +

Solid performance for the number of NAND die

Cons

- -

Not 100% optimized at this time

Why you can trust Tom's Hardware

Specifications And Features

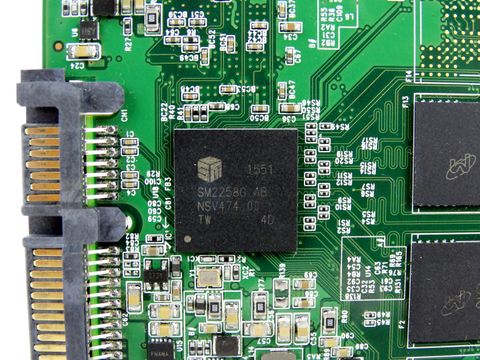

The Silicon Motion SM2258 controller is already shipping with 2D NAND in Intel's 540s (consumer) and 5400s (professional) SSDs. Intel leveraged the SM2258's powerful low-density parity check for one last gasp with 2D NAND, but we expect to see the SM2258 ship in several new products as IMFT 3D flash becomes widely available.

At Computex 2016, we spoke with several Tier 3 SSD manufacturers, which are companies without NAND flash manufacturing or SSD controller intellectual property, that were evaluating the SM2258 for future SSD designs with the new IMFT (Intel/Micron Flash Technology) 3D NAND. Silicon Motion, Inc. (SMI) built a good working relationship with both Intel and Micron by supplying them with controllers for existing and upcoming SSDs, so it doesn't just have a front row seat for the 3D NAND show; it is actually in the ring with IMFT's new 3D flash.

SMI has already committed to building the SM2260 NVMe controller for Micron's new Ballistix gaming brand, which features the company's new 3D multi-level cell (MLC) flash. The relationship helped the company gain working knowledge of the new flash, while some other controller manufacturers are still waiting to get a sample so they can build a prototype controller.

Let's take a first look at the entry-level SM2258, which now supports IMFT's 3D TLC flash.

Technical Features

To build the controller, SMI had to master two disciplines that are often at odds with each other. The first hurdle was to develop a new custom controller for the entry-level SSD market, which is the segment where the model with the lowest price often dominates sales. The second challenge was to develop and incorporate new technologies that allow low-cost, low-endurance 3-bit per cell flash to thrive under consumer SSD conditions through the warrantied period. The trick is to blend low cost and high technology into one design.

Architecture

- 32-bit RISC CPU

- High-efficiency 64-bit system bus

- Automatic sleep and wake-up mechanism to save power

- Built-in voltage detectors for power failure protection

- Built-in power-on reset and voltage regulators

- Built-in temperature sensor for SSD temperature detection

- Supports JTAG interface, UART (RS-232) interface, and I2C interface for on-system debug

Host Interface

- SATA Revision 3.1 Compliant

- ATA/ATAPI-8 And ACS-3 Command Compliant

- SATA interface rate of 6Gb/s (backward compatible to 1.5Gb/s and 3Gb/s)

- Native Command Queuing up to 32 commands

- Supports SATA device sleep (DevSleep)

- Data Set Management command (TRIM)

- Self-Monitoring, Analysis, and Reporting Technology (S.M.A.R.T.)

- Supports PHY Sleep mode (CFast PHYSLP)

- Supports 28-bit and 48-bit LBA (Logical Block Addressing) mode commands

Data Protection And Reliability

- Supports ATA8 security feature set

- Supports data security erase and quick erase

- Proprietary NANDXtend error-correcting and data protection technology triples the P/E cycles for 3D TLC SSD devices

- Internal data shaping technique increases data endurance

- Software/Hardware write protect option

- StaticDataRefresh technology ensures data integrity

- Early weak block retirement option

- Global wear leveling algorithm evens program/erase count and extends SSD lifespan

NAND Flash Support

- Supports 1z nm TLC and 3D MLC / TLC NAND

- Supports ONFI 3.0, Toggle 2.0, and Asynchronous interface

- Supports 1.8V/3.3V Flash I/O

- Supports 8KB and 16KB page size

- Supports 1-plane, 2-plane, and 4-plane operation

- 4-channel flash interface supports up to 32 NAND flash devices

DRAM Interface

- 16-bit wide DRAM interface

- Supports DDR3/DDR3L

SMI used its proprietary NANDXtend low-density parity check (LDPC) error correction codes with the SM2258. Error correction is the core technology that allows SSD manufacturers to build new low-cost SSDs with lower quality NAND. The dirty secret is that NAND endurance has decreased with each new lithography shrink, and LDPC provides both soft and hard decode options to boost endurance beyond the raw error rate.

In theory, IMFT's 3D flash was supposed to reset the clock on NAND endurance, but some SSD manufacturers are still preparing for 1,000 to 3,000 program/erase cycles without sophisticated error correction techniques.

NANDXtend is not a new technology. SMI used it on the SM2256 controller that it designed for planar TLC flash. Silicon Motion continues to improve on the LDPC code to deliver even more endurance and efficiency while reducing power consumption.

StaticDataRefresh is another proprietary technology from SMI, but other companies have similar features. The technique keeps your data from suffering from voltage drift, which occurs when the eight cell charge levels (with TLC) move around. The "drift" forces the controller to use robust ECC techniques to read the data properly when the voltages get close to the next charge level, but the extra steps increase latency and slow down read performance. StaticDataRefresh technology monitors the voltages and gives a quick refresh as needed to keep read performance high over time.

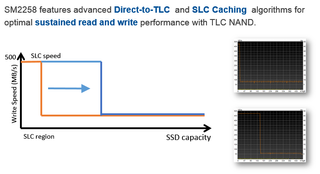

The SM2258 brings other improvements over the year-old SM2256 controller. We first talked about new direct-to-die writing schemes with the competing Phison's S10 controller, but SMI has a similar "direct-to-TLC" technology. Both work the same. When the SLC-programmed buffer gets full, the SSD starts to write the incoming data directly to the TLC flash. In previous SSDs, all of the incoming data passed through the SLC buffer before the SSD wrote it to the TLC layer. This technique decreased wear on the flash, but the 'fold' method forced the SSD to slow down the incoming data once the fast SLC buffer was full. The fold method allowed the SSD to make space available for more incoming data, but it occurred while the SDD was pushing data to the slower TLC area.

The SM2258 controller reports a large number of SMART readings. Our sample may have a link to the next-generation BX300. The BX series is Crucial's entry-level offering that also uses Micron flash. In the past, Crucial used SMI controllers for the BX series. At this time, there is not a guarantee the BX300 will ship with Silicon Motion's SM2258 controller, and neither company has released a public comment about a BX300 design win.

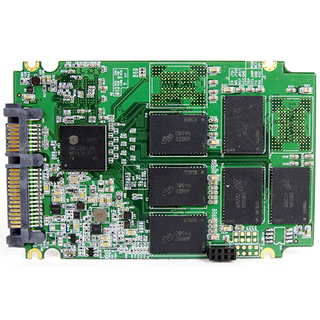

A Closer Look

IMFT 3D TLC flash is the world's first 384Gbit die, which equates to 48GB per die. The NAND provides 1.5x the capacity of 256Gbit MLC flash, which was simply the next evolution of the older 128Gbit die. The odd density means that SSDs with the flash will have very strange configurations. Most 256GB SSDs on the market use four or eight packages, but the SM2258 reference design we have on hand features six packages. Each package contains a single 48GB NAND die for a total of 288GB of raw capacity.

Companies can slice the 288GB pool into 256GB of addressable capacity with 32GB reserved for background activity, or 240GB of capacity with 48GB reserved. The Crucial MX300 ships with 275GB of capacity, but we suspect other SSD manufacturers will choose higher spare area because of the performance benefits.

This should mark the end of 128GB SSDs for most markets, but it shifts low parallelization (AKA slower) SSDs into the 256GB capacity class. 256GB SSDs will soon become obsolete for most of our readers, and 512GB SSDs will take the helm for mainstream use. Even exotic 2TB models are becoming more common.

The SMI SM2258 controller supports 4-channels with 8 CE, which means it supports up to 1536GB of NAND with 384Gbit die. Micron already disclosed some details of its next generation 3D TLC, which is expected sometime in 2017. The new stack doubles from 32-layers to 64-layers, and the die density increases from 48GB to a whopping 96GB.

The extra flash capacity means the controller needs to address more DRAM to cache the flash translation layer data. Our SM2258 prototype sample has pads for two DDR3/DDR3L packages.

Micron's 3D TLC flash holds three times more data than the company's densest planar TLC. To get mainstream performance, SSD manufacturers will need to focus on 512GB-class products as the starting point. Anything under that capacity will suffer from higher latency and lower sequential performance during nearly all workloads.

To drive the point home, the SMI SM2258 prototype we are testing has the same parallelization as many current 64GB SSDs. When was the last time we talked about a fast 64GB SSD, or even any SSD at that capacity? That is the difference that IMFT's leap to 384Gbit made with TLC NAND.

MORE: Best SSDs

MORE: Latest Storage News

MORE: Storage in the Forums

-

Badelhas What does this mean, in reallity? It will outperform the high-end samsung 850 pro drives?Reply -

stairmand It's pretty cool, but I really don't see the point. S-ATA SSDs are a dead end, the future belongs to M.2 and U.2.Reply -

Reply18409763 said:Low endurance 3-bit per cell?!? That is 32 bit right?!

tlc have 3-bit cells. there are 8 levels of states (not sure if these are volts or amps), each level give a binary number between 000 and 111, so can represent 3 independent bits. To have 2 independent bits, you only need to reliably distinguish 4 states, which is obviously easier, but the 66% less memory per density.