Intel Patents Forming MP Chips Using Dual Processors

Intel has received a patent covering its technology to create multi-core processor packages from individual dual-core processors.

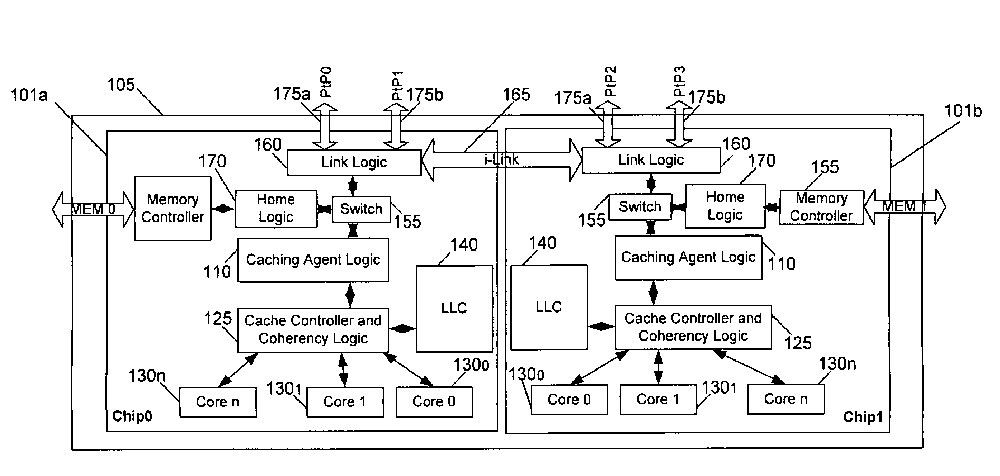

Filed in April 2007, the patent describes a replication of entire processors by creating point-to-point link logic between the multi-core processors. Specifically, the patent describes a design approach that delivers a much faster time to market and less complexity as this patent does not rely on modified processing protocols or significant hardware design changes.

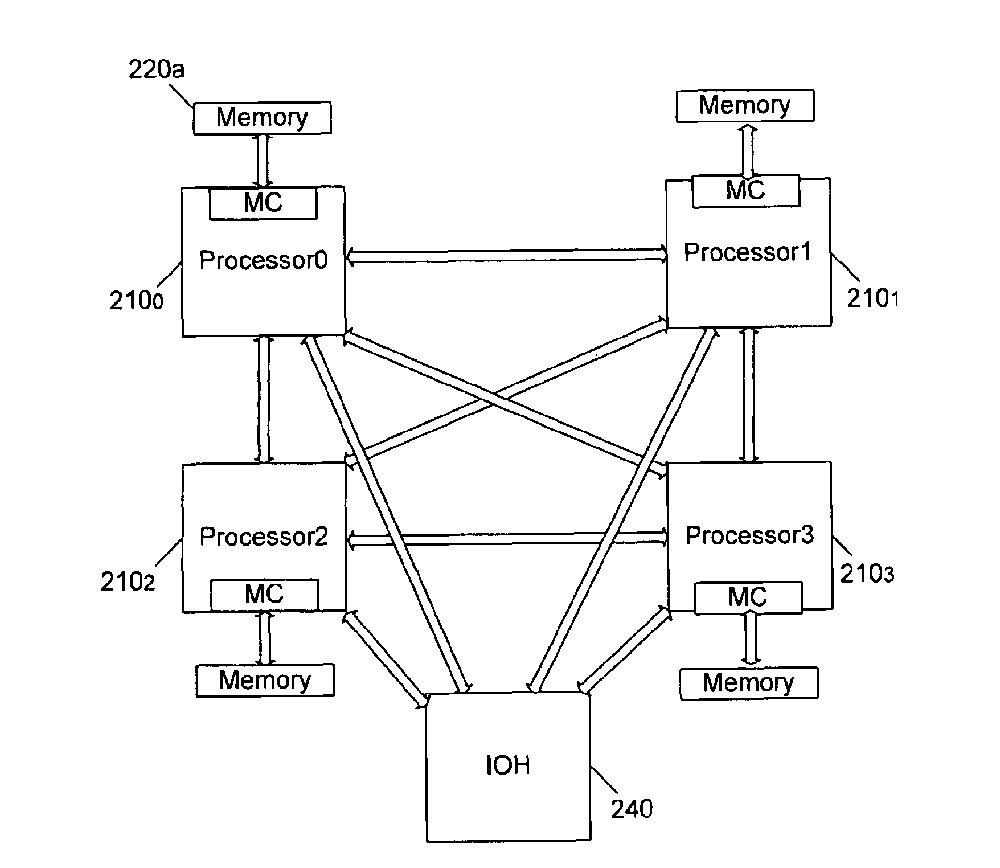

Illustrations included in the patent reveal that Intel's multi-chip package can be created simply by using an intra-package interconnect as point-to-point link with short trace length that allows for a shorter and wider bus as well as higher clock speeds to achieve substantial bandwidth between the two processors. According to Intel, that link can be established via interconnects that are already available on the substrate.

Additionally, Intel is using a "protocol joining method" to figure out the number of necessary caching agents and home agents in the system. Additional caching agents are treated as independent caching domains and the burden of managing coherence between the two caches relies on the point-to-point cache coherency domain.

Article continues belowGet Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Douglas Perry was a freelance writer for Tom's Hardware covering semiconductors, storage technology, quantum computing, and processor power delivery. He has authored several books and is currently an editor for The Oregonian/OregonLive.

-

husker It does appear to simplify the architecture, but this type of simplification usually comes at a cost of speed and efficiency. I'm wondering if it will scale well with a large number of processors since it requires a point to point link between all processors this could get out of hand in a hurry.Reply -

ojas Parsianisnt this the method they used to make the Core 2 Quads?Probably been using it already, just that the patent was granted now.Reply -

eddieroolz huskerIt does appear to simplify the architecture, but this type of simplification usually comes at a cost of speed and efficiency. I'm wondering if it will scale well with a large number of processors since it requires a point to point link between all processors this could get out of hand in a hurry.Reply

That may have been true for the days of FSB that were bottlenecking single processors, let alone dual. However, with the days of QPI buses this might not be such a big issue.

-

bigdog44 The first diagram looks like a pentagram on homebase... is SIntel patenting its' business model?Reply

-

willard DjEaZy... it's like hypertransport in a sense...Yeah, in the same way that a car is like a road.Reply

Hypertransport is a method of interconnecting chips. This patent is for what you can do with interconnected chips. -

madooo12 bigdog44The first diagram looks like a pentagram on homebase... is SIntel patenting its' business model?can you patent to be evil, a big monopoly and an anti-competitive company? don't answer thatReply -

husker eddieroolzThat may have been true for the days of FSB that were bottlenecking single processors, let alone dual. However, with the days of QPI buses this might not be such a big issue.Good point.Reply