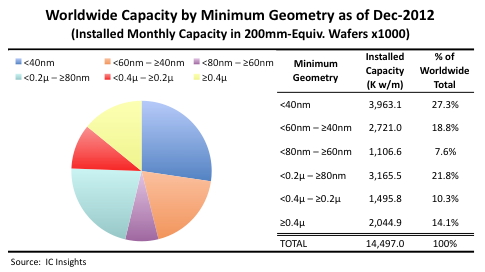

Report: Sub-40 nm Processes Account for 27% of Global Wafer Capacity

According to IC Insights, at the end of 2012, 27 percent of capacity was used for devices with geometries smaller than 40 nm.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

At the end of 2012, sub-40 nm processes accounted for 27 percent of global wafer capacity, followed by 2.18 percent for 80 nm to 0.2µ “mature process nodes” and 18.8 percent for 40 nm to 60 nm geometries.

The increased prevalence of 40 nm or smaller geometries has been attributed to its use in high-density DRAM, which are typically built using 30 nm-class to 20 nm-class process technologies; high-density flash memory devices that are based on 20 nm-class to 10 nm-class processes; and high-performance microprocessors and advanced ASIC/ASSP/FPGA devices based on 32 nm, 28 nm or 22 nm technologies.

IC Insights further noted that Samsung Electronics was the largest supplier of ICs built using sub-40 nm geometries at the end of 2012 followed closely by Intel, Toshiba / SanDisk, SK Hynix and Micron Technology. Additionally, they noted that process technologies with geometries greater than 0.4-micron maintain "a fairly large share" of the global installed capacity due to large quantities of commodity-type devices such as standard analog and general-purpose logic ICs.

Article continues belowGet Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Tarun Iyer was a contributor for Tom's Hardware who wrote news covering a wide range of technology topics, including processors, graphics cards, cooling systems, and computer peripherals. He also covered tech trends such as the development of adaptive all-in-one PCs.

-

utroz You gotta love how the use the "30 nm-class to 20 nm-class process technologies" wording that really means they are using muiltipattering and etching with a much larger base process to make their chips. Granted GF has made a crap ton of real 32nm chips but they are late as heck with 28nm and should of had 22/20nm out in retail this spring. They claim they will have a 14nm XM for 2014. (source http://www.globalfoundries.com/technology/pdf/GF-14XM-Press-FINAL.pdf page 7) I hope they will, but they claimed 20nm for 2h2012 and if they really did AMD would have at least had APU's on GF's 28nm if not 20nm by now. GF talks the talk but they seem to have 2years of lag time till they actually go from super-risky-test silicon to production-ish silicon. 32nm was a disaster because of gate first and has cost AMD crap loads. Just think what BD or PD could be with gate last HKMG-PD-SOI. I hope they use the new FD-SOI-28nm process that got the arm chips running at 3Ghz for the new AMD cpu's. I am doubtful GF will have their ducks lined up in time for 20nm or 14nm-XM. Funny that even 45nm-SOI-HKMG was better than 32nm-SOI-HKMG-Gate First in everything but in the size of electronics on the die. Leakage might be the major killing factor between the them. I have heard from my people that GF's 32nm-SOI is not a very stable process and that it varies greatly from batch to batch of IC's. I just think they need to go Gate Last with FD-SOI, HKMG, and Finfets. Also 2.5d and 3d interconnects,CSV's, and silicon on interposers would be a good boost for them as well if they can actually manufacture it in high volume (making a couple test chips is easy you have 1000's of test chips packaged to test and eventually you will find one that works as long as your design rules and validation are not total crap. Well this is the end of my rant.. Hope the rest of you know that I am not hating on AMD of GF, I just want them to do what they say they can, when they say they can... It is like a 12year old saying he can bench 250lb's but in reality he can't do it till he is 14-15years old.. I just wanna know the truth GF and I bet AMD does too. (Hence the canceled Krishna and Wichita APU's that were due last summer on GF 28nm- HKMG-Gate First)Reply

-

neblogai Capacity in wafers is one thing, and capacity in transistors is another. It is a bit like counting as equal 1 dollar bill and a 100 dollar bill just because they are both of the same size.Reply -

Wisecracker Reply10695954 said:... I am not hating on AMD of GF ...

Yeah. You are. And, you're not even doing it well.

Ontario/Zacate (Bobcat) ---> Krishna/Wichita is/was TSMC.

(as will be Kabini/Temash (Jaguar) APUs)

-

utroz Reply10696830 said:10695954 said:... I am not hating on AMD of GF ...

Yeah. You are. And, you're not even doing it well.

Ontario/Zacate (Bobcat) ---> Krishna/Wichita is/was TSMC.

(as will be Kabini/Temash (Jaguar) APUs)

I actually like AMD quite a bit. It just sucks that GF is way way behind on 28nm. Krishna/Wichita was GF here is proof http://www.extremetech.com/computing/106217-manufacturing-bombshell-amd-cancels-28nm-apus-starts-from-scratch-at-tsmc The whole reason that we have been stuck with TSMC 40nm Ontario/Zacate for so long after AMD has had large 28nm GPU's from TSMC 28nm is because Krishna/Wichita were designed for GF's gate-first 28nm process and TSMC's 28nm is gate-last (well there are a bunch of other reasons like design rules and such). So the new Kabini/Tesmash have better cpu cores than Krishna/Wichita and they have upgraded to a GCN gpu as well. So AMD did not simply just port what they had from GF to TSMC they just skipped a whole generaton and went on to the next. GF does claim that they are catching up with the 20nm and 14nm-XM and it would be nice for AMD if GF actually can stick to there roadmap this time. Here is a good article on how semidconductor manufactorers take a larger process and make smaller nm class devices with it http://en.wikipedia.org/wiki/Multiple_patterning -

catfishtx When I started in the semiconductor industry, my company was transitioning from .6 to .35 microns. Hard to believe that there are still companies using that process.Reply