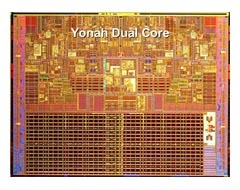

Intel's Yonah dual-core processor to get 'Smart Cache'

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Santa Clara (CA) - Intel provided several updates about its first mobile dual-core processor "Yonah". The chip, scheduled to enter production late in 2005, will be equipped with 2 MByte shared L2 cache, as well as a shared bus architecture.

With the desktop dual-core Pentium D out the door, Intel now is preparing for the final development phase of Yonah. Yonah will be not only the first mobile dual-core processor, but also the first processor to be manufactured in 65 nm.

According to Mooly Eden, vice president and general manager of Intel's mobile platforms group, Yonah will carry 151.6 million transistors, integrate a 667 MHz front side bus and wll be built into a PGA478 or BGA479 package. The chip will use a revamped architecture that combines two execution cores on one piece of silicon. Both cores share one bus and 2 MByte L2 cache.

Power consumption of the dual-core chip will remain in the power envelope of today's single-core Pentium M processor (about 25 watts). Intel explained this achievement with enhancements in "deeper sleep" and Speed Step technologies as well as improved leakage current behavior in its 65 nm structures.

While smaller structures typically increase leakage current, Intel said in a recent conversation with Tom's Hardware Guide that the company was able to actually improve the relationship between transistor performance and leakage with 65 nm chips, if compared to the previous 90 nm generation. Yonah is the first processor to take advantage of this effect. Apparently, the progress in the scaling field was much larger than Intel originally expected and prompted the company to change its power consumption roadmap: Last year, the company said notebooks with battery running times of about 8 hours could be available by 2010. Today Eden said such devices could hit the market already by 2008.

Considering the amount of innovation in Yonah, it is almost surprising that Intel's first Yonah processor will not be able to run 64-bit applications. We also remember former chief technology officer Pat Gelsinger urging software developers to work on 64-bit applications "now" not too long ago. At this time, it is not clear why Yonah will be a 32-bit only chip. Eden said the technology is available today, but the 64-bit market has yet to mature. However, we also heard in the past that the integration of 64-bit capability would have increased the size and power consumption of the chip.

Mass-production of Yonah is scheduled to begin late this year with commercial products expected to become available in the first quarter of 2006.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Related stories:

Intel sees 65 nm transition on track, 450 mm wafers appear on horizon