Hot Chips 2017: We'll See PCIe 4.0 This Year, PCIe 5.0 In 2019

We caught up with PCI-SIG, the organization that defines the PCI Express bus and form factor specifications, at the yearly Hot Chips conference. PCIe is the ubiquitous engine that pulls a big part of the computing locomotive down the track—it touches nearly every device in your computer. As such, it is the linchpin for the development of many other technologies, such as storage, networking, GPUs, chipsets, and many other devices.

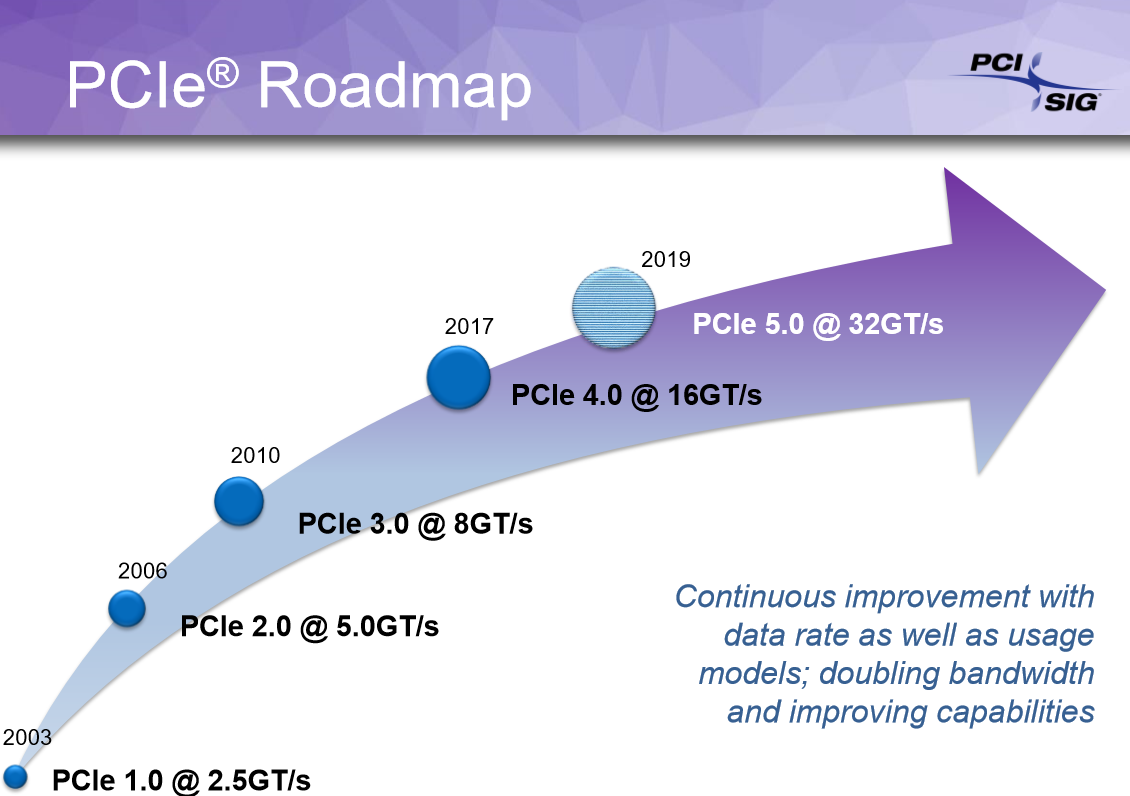

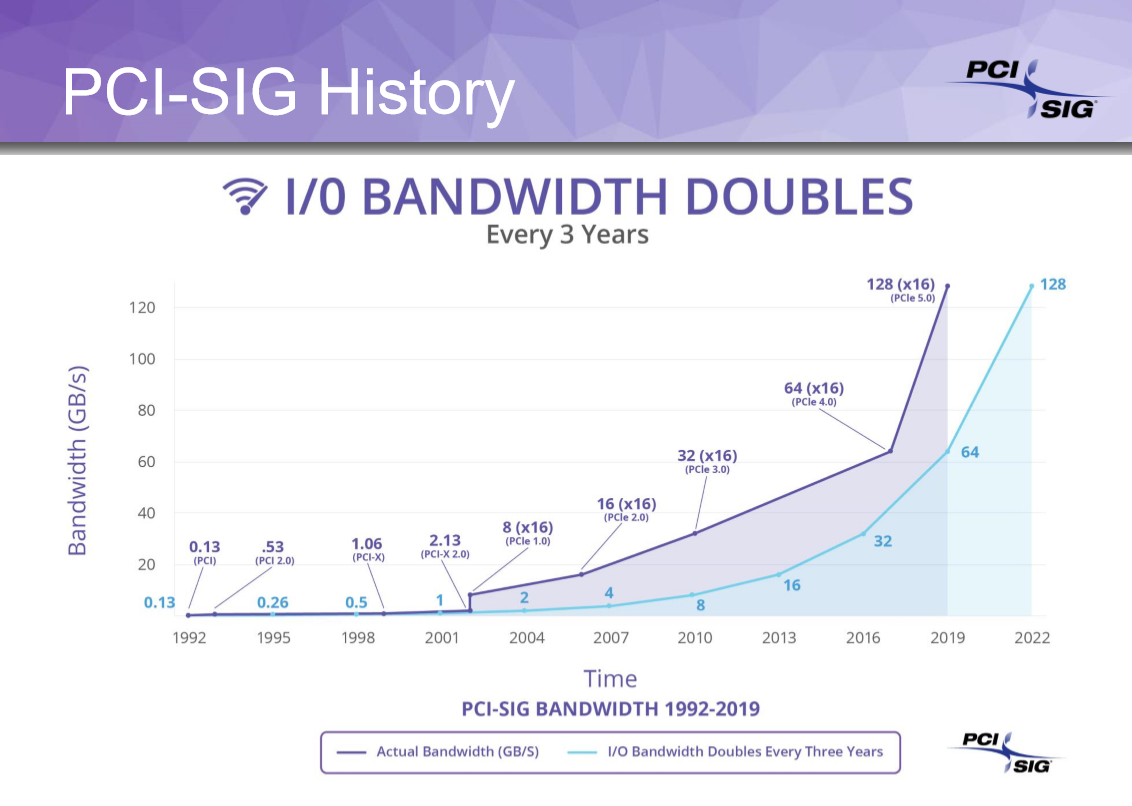

Considering its importance, it isn't surprising to find the PCI-SIG with 750 members worldwide. Unfortunately, large organizations tend to move slowly, and PCIe 4.0 is undoubtedly late to market. PCIe 3.0 debuted in 2010 within the normal four-year cadence, but PCIe 4.0 isn't projected to land in significant quantities until the end of 2017—a seven-year gap.

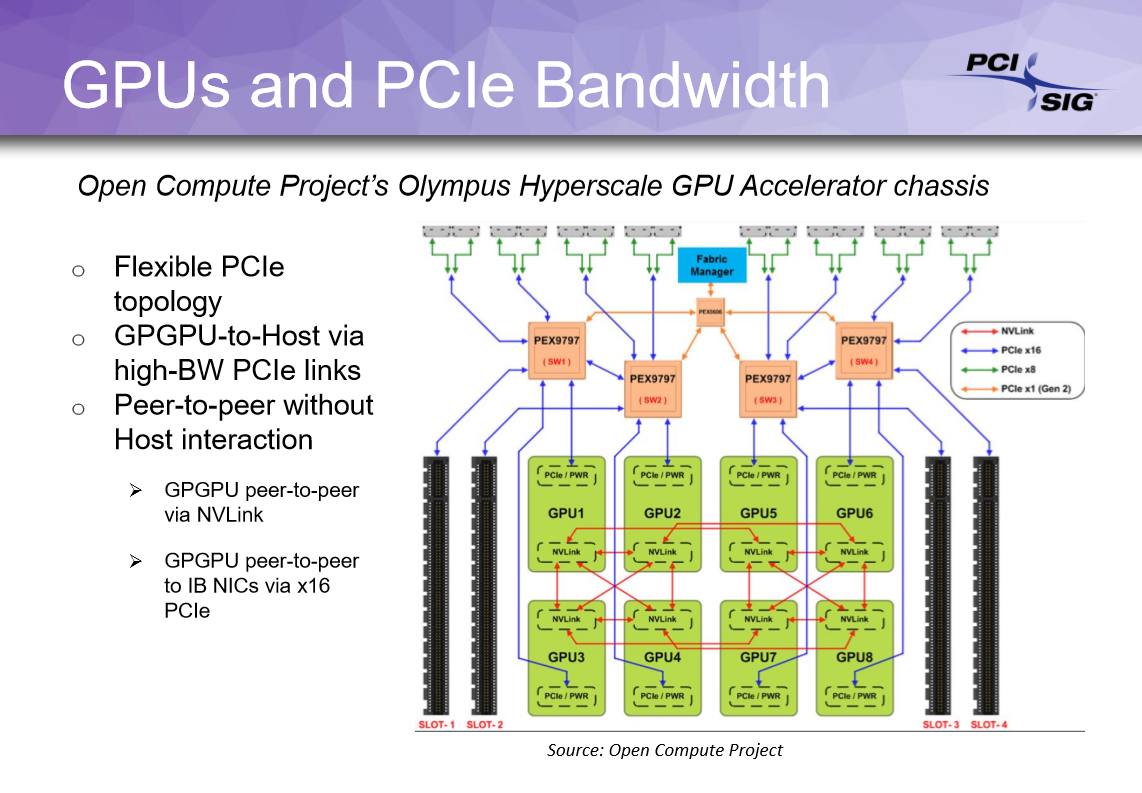

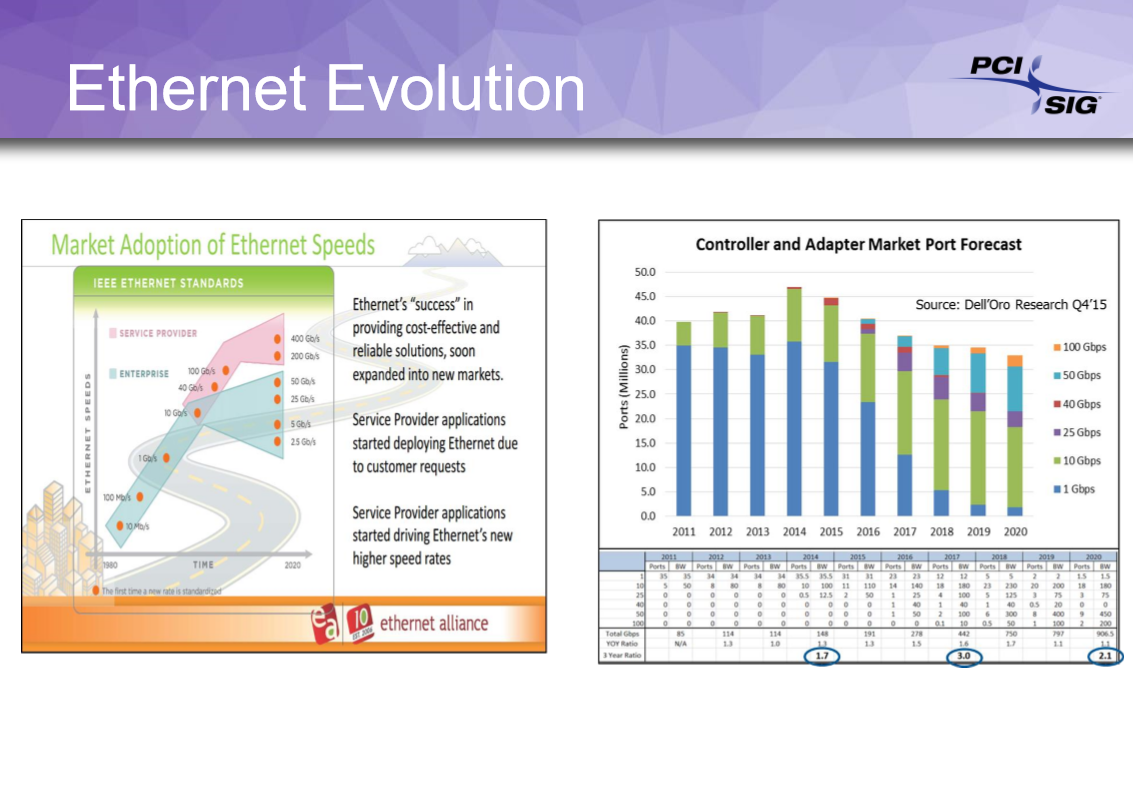

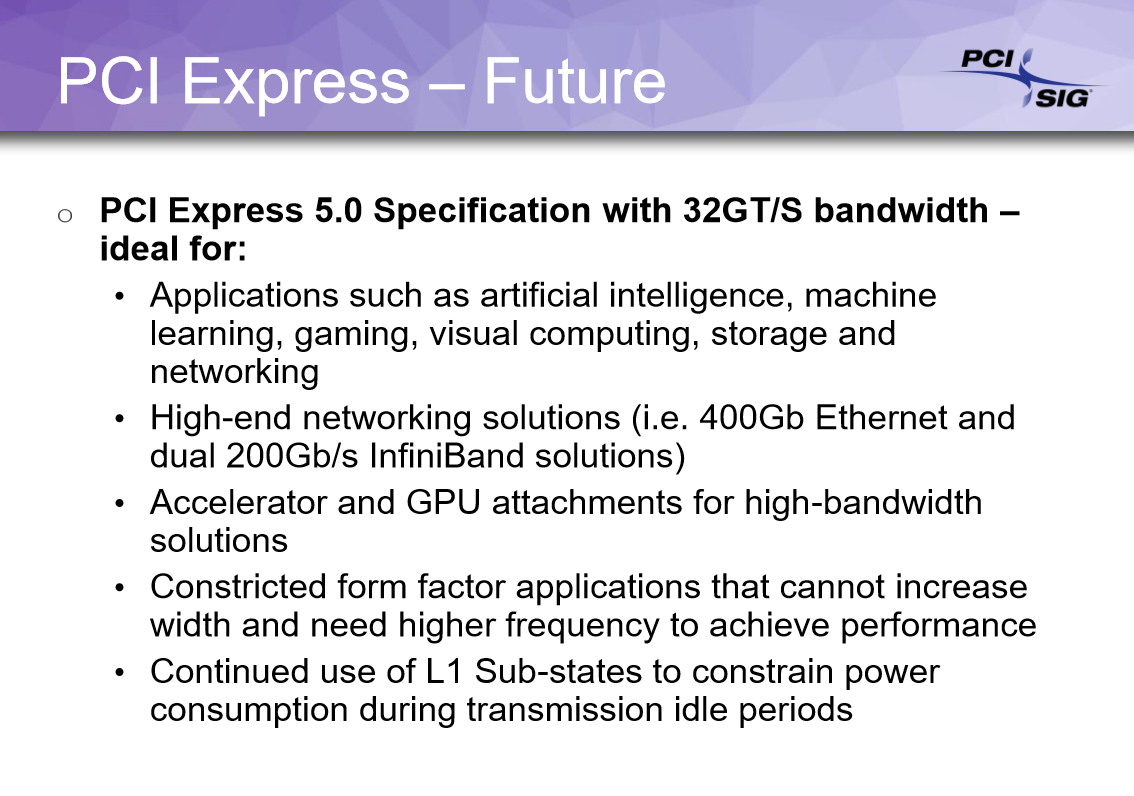

PCI-SIG representatives attributed part of the delay to industry stagnation. The PCIe 3.0 interface was sufficient for storage, networking, graphics cards, and other devices, for the first several years after its introduction. Over the last two years, a sudden wellspring of innovation exposed PCIe 3.0's throughput deficiencies. Artificial intelligence craves increased GPU throughput, storage devices are migrating to the PCIe bus with the NVMe protocol, and as a result, networking suddenly has an insatiable appetite for more bandwidth.

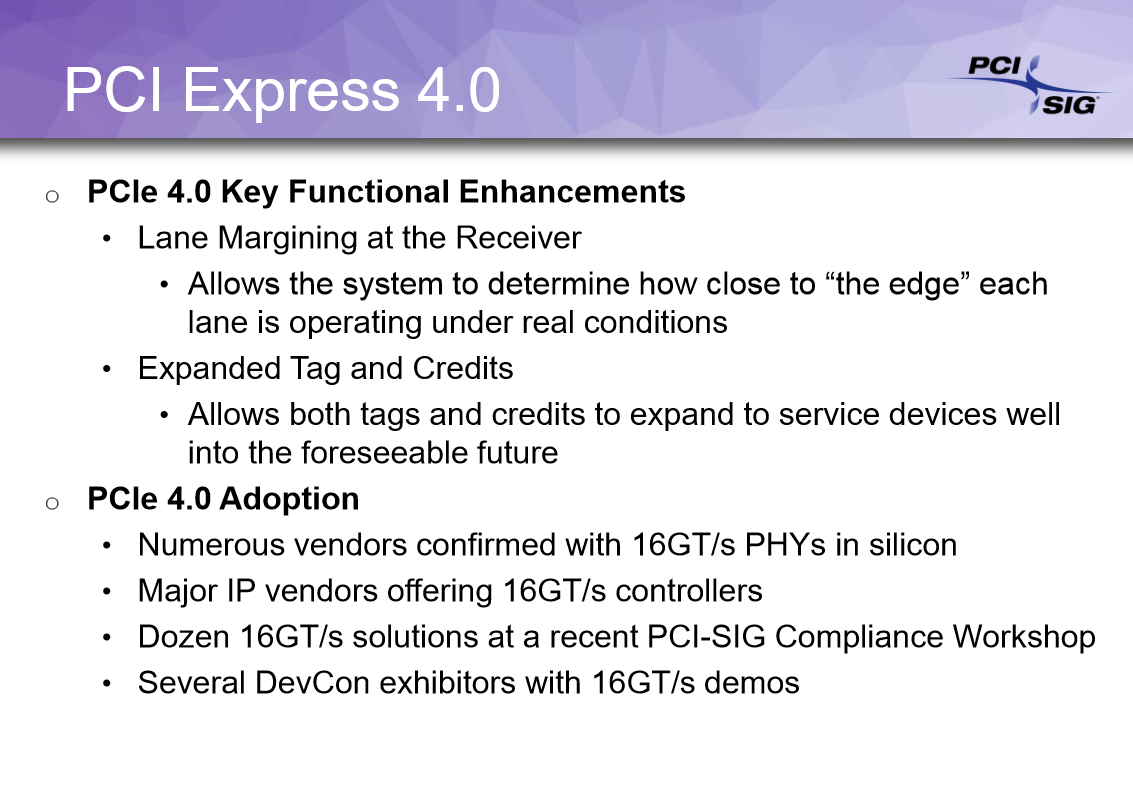

Article continues belowThe industry needs PCIe 4.0 to land soon, and PCI-SIG assures us it will ratify the new specification by the end of 2017. The sluggish ratification process hasn't hampered adoption entirely, though. Several IP vendors already offer 16GT/s controllers, and many vendors have already implemented PCIe 4.0 PHYs into their next-generation products. These companies are plowing ahead with the 0.9 revision of the specification, whereas the final ratified spec debuts at 1.0.

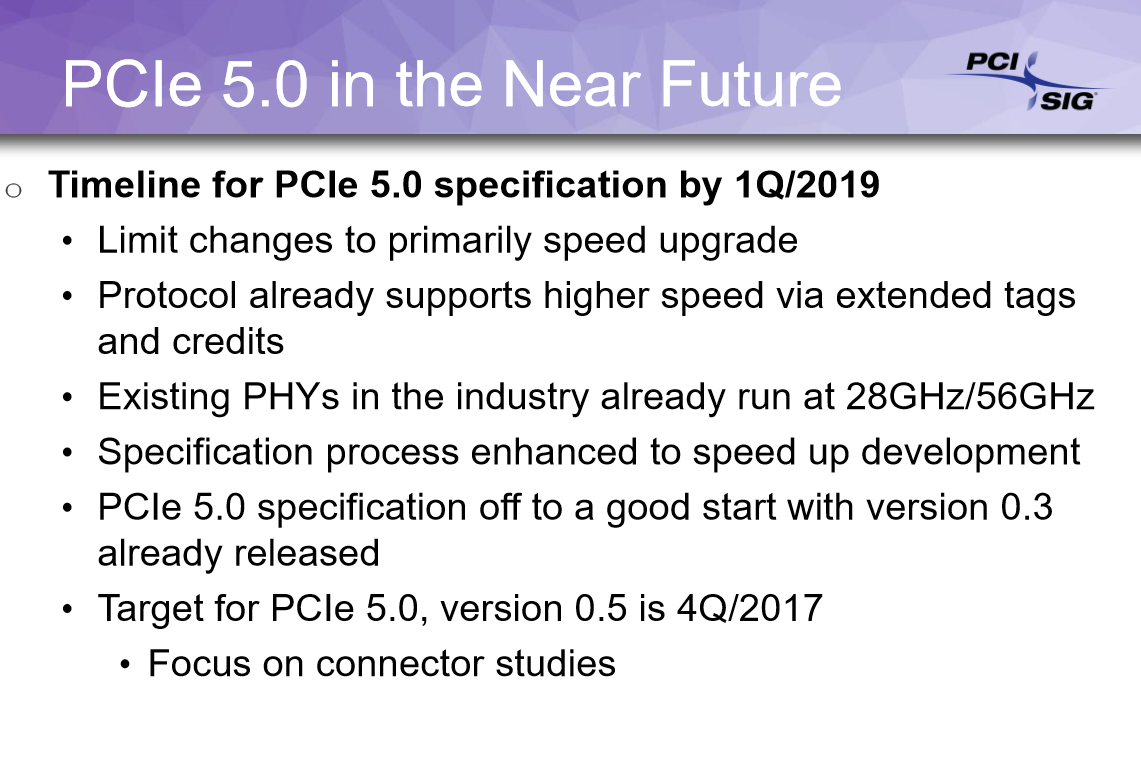

PCI-SIG says it is accelerating the development and feedback processes, along with simplifying early specification revisions, in a bid to reduce time to market for future specifications.

PCI-SIG indicates that PCIe 4.0 will be a short-lived specification because the organization has fast-tracked PCIe 5.0 for final release in 2019.

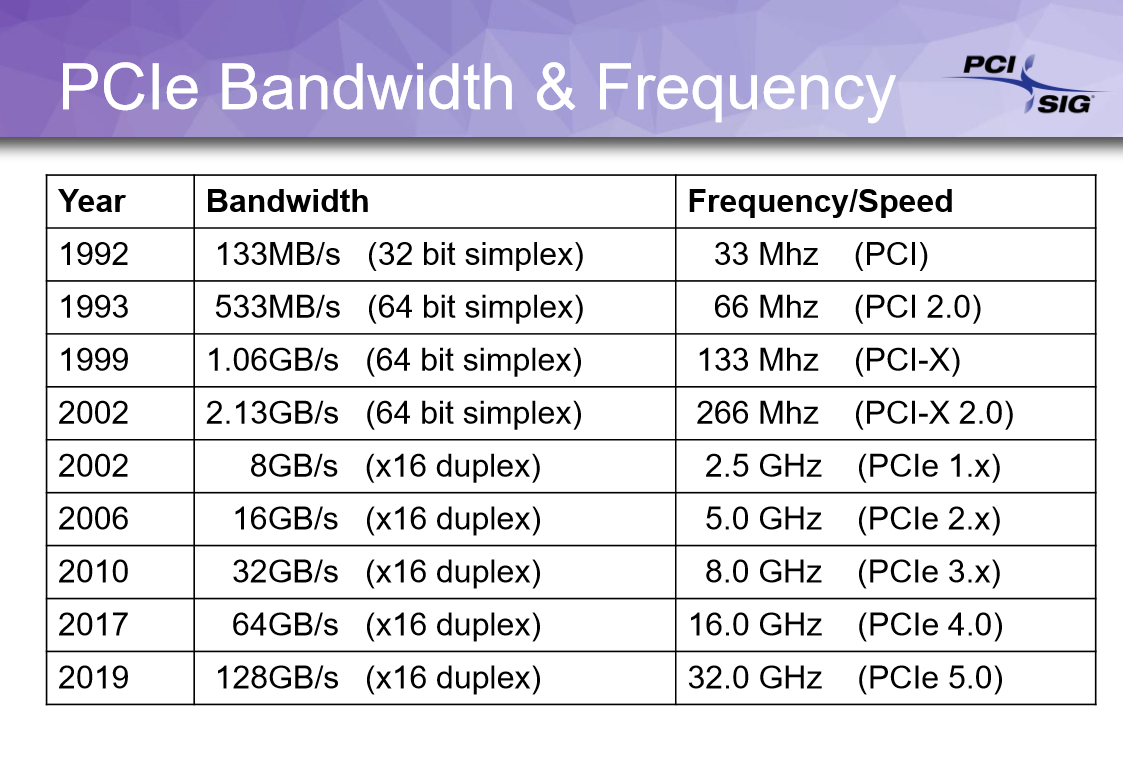

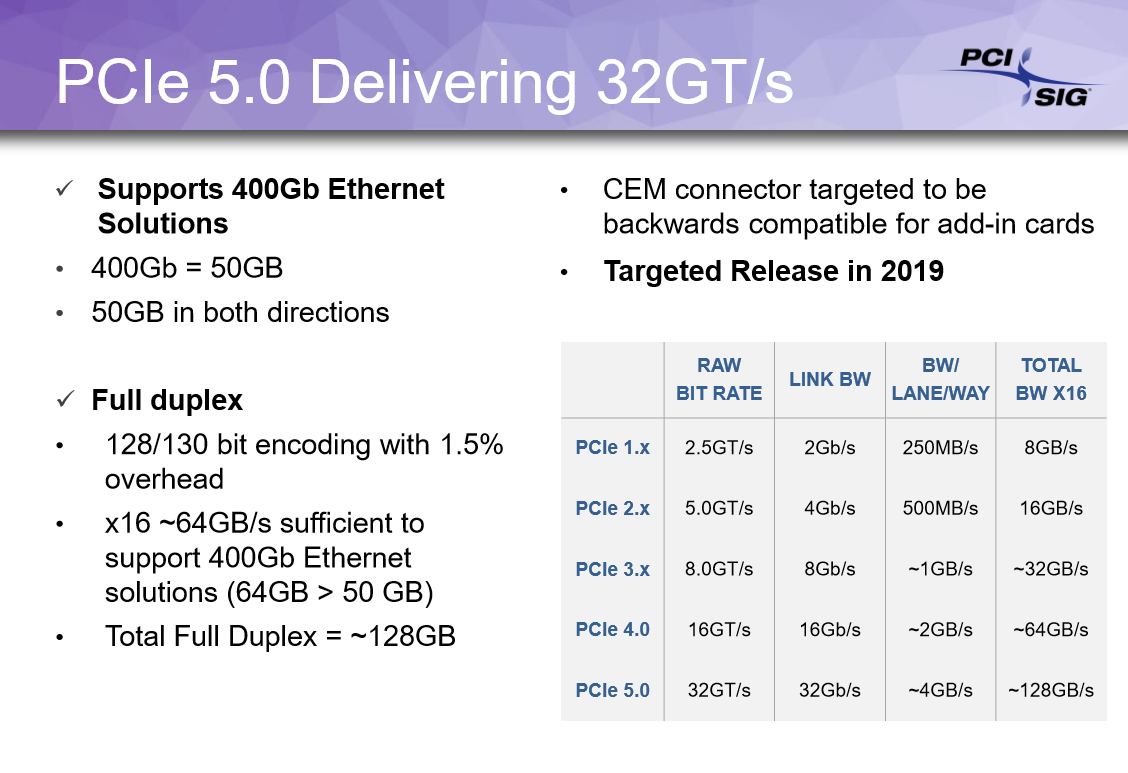

PCIe 4.0 will bring us 64GBps of throughput, while PCIe 5.0 will double that to 128GBps. Both revisions still leverage the standard 128b/130b encoding scheme that debuted with PCIe 3.0. PCI-SIG representatives said they are satisfied with the 20% reduction in overhead facilitated by the 128b/130b encoding, and further encoding refinements to reduce the current 1.5% overhead are subject to a diminishing point of returns.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Although we have yet to see PCIe 4.0 on the market, the fast-tracked PCIe 5.0 is already on revision 0.3, and the group predicts 0.5 will be available by the 4Q17.

The PCI-SIG defines the specification, but it has no control over when the end devices make it to market. Intel and AMD are the key enablers for the broad desktop market; we certainly won't see PCIe 4.0 GPUs and SSDs without a slot to plug them into. AMD has slated PCIe 4.0 for 2020. We imagine Intel is also chomping at the bit to deploy PCIe 4.0 3D XPoint and NVMe SSDs, but the company remains silent on its timeline.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

Martell1977 Looking at what AMD has been doing, I wouldn't be surprised if AMD skipped 4.0 and jump right to 5.0. Similar to how they are jumping from 14nm to 7 and ignoring 10nm altogether. But, we will know for sure when we see what Navi and Ryzen 2 (possibly Ryzen 3) come with.Reply

On a side note, I'm hoping AMD updates their roadmap, I haven't seen anything about what's after Navi. -

Rob1C I don't know and Search Engines provide no Source that AMD (or Intel) is "waiting", they simply don't have PCIe 4.0 now; a reasonable speculation is that they will wait for it to be ratified to 1.0, and after that, then they will decide. So no announced decision yet.Reply

IBM POWER9 has it already, along with NVLink 2.0 (for Volta), there's no way Intel wants 'pants down' again.

With AMD's huge number of PCIe Lanes, and a limited number of Slots on most MBs, they have to go somewhere.

The IP is available: https://www.synopsys.com/designware-ip/interface-ip/pci-express.html .

The HotChip's Conference even had a Demo of 5.0:

It's possible for 5.0 to be available by year's end, just buy the IP and send it to your Fab. - It's not like 5.0 is a big leap from 4.0, because it's designed not to be a leap.

The SoC or Bridge has to provide it so others will make 4.0 Cards to plug into it, it's not like Mfgs are going to start making 5.0 SSDs and Graphics Cards with nothing to plug them into.

AMD and Intel will likely be onboard by early next year. With AMD's 7nm Epyc scheduled for early next year does it make sense to have Lanes and Fabric but nothing to blow their nose on.

It's coming, naysayers! -

It took 7 years to go from 32GB/s to 64GB/s, and two years later we are going to have 128GB/s? I'm skeptical.Reply

-

bit_user Reply

NVMe only happened in the last year or so. Plus, the cloud wants multi-GPU deep learning and > 100 Gbit networking.20117210 said:It took 7 years to go from 32GB/s to 64GB/s, and two years later we are going to have 128GB/s? I'm skeptical.

If this is what it takes to head off more proprietary alternatives like NVLink, it definitely has my support.

-

Rob1C Andy Chow said:ReplyIt took 7 years to go from 32GB/s to 64GB/s, and two years later we are going to have 128GB/s? I'm skeptical

Here is a Motherboard with one PCIe x32 Slot: http://www.supermicro.com/products/motherboard/Xeon/C600/X9DRW-CTF31.cfm .

If we had PCIe 4.0 that x32 Slot could be x16 instead, and have the same bandwidth.

The Samsung 960 PRO uses x4, and it would be easy to stick 8 of those on a PCIe Card. You'd need that x32 Slot for a Card like that.

A dual Volta would benefit from the bandwidth.

Latency is going to drop on a PCIe 5.0 Slot even if the Data were only coming out at 3.0 rates, seek times could be more than 3x faster.

Five PCIe 5.0 Slots at x8 would only be 40 Lanes, leaving some spares on some CPUs.

There's not of use cases to offer you, this being a "chicken and the egg" problem (for which we know the answer).

-

velocityg4 Looking at the timeline. It appears as though I'll be skipping PCIe 4.0 and going to 5.0. Unless my computer dies. My i5-3570K should be good until then.Reply -

bit_user Reply

Keep in mind there might be some additional lag, before it shows up in desktops & consumer-oriented GPUs.20120503 said:Looking at the timeline. It appears as though I'll be skipping PCIe 4.0 and going to 5.0. Unless my computer dies. My i5-3570K should be good until then.

-

Wisecracker While it's nice to dream about this massive new increase on bandwidth/operations on an 'individual' basis, the most practical applications are in the AMD 'UMI' and Intel 'DMI' (or, whatever they call the platform 'interlinks' these days ...) on the desktop.Reply

It seems to me (and I can always swing and miss) that there has only been a significant performance gain using PCI Express 3.0 instead of PCI Express 2.0 "lanes" in limited areas over the last 12 months or so (as B-U pointed out with NVMe and NVLink), and I would tend to be skeptical overall that any system performance hurdles or bottlenecks would simply move somewhere else in the 'big picture' ... especially on the consumer side of things.

BUT, as we all know, Gen 5.0 is always GREATER than Gen 4.0, or 3.0 or 2.0, or 1.0 ... They're obsolete!

:lol: