PCIe 7.0 spec finalized with up to 512GB/s speeds — PCI-SIG targets 1TB/s for 8.0 as 'exploration' phase begins

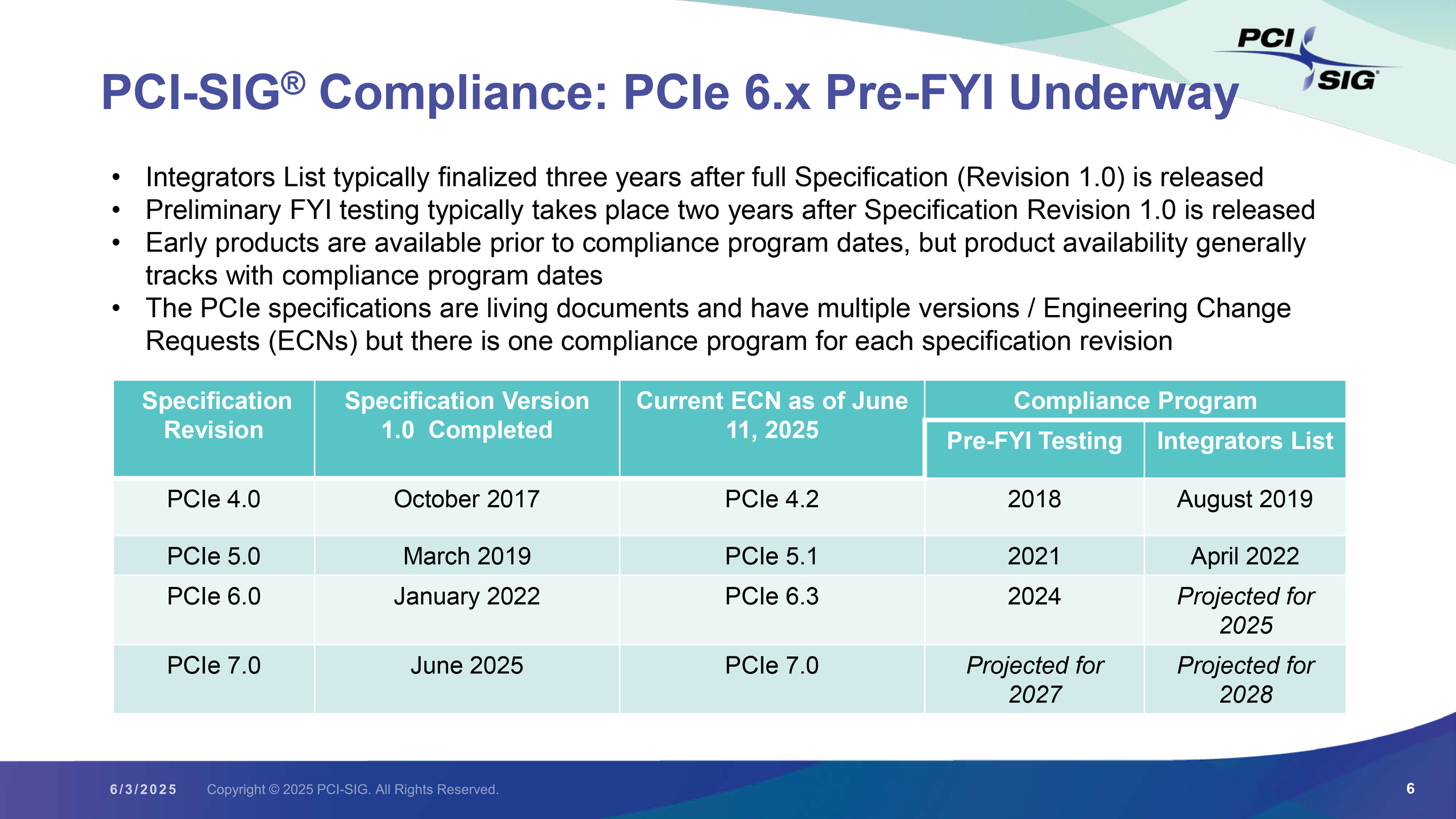

PCIe 6.0 interoperability tests are planned for later this year.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

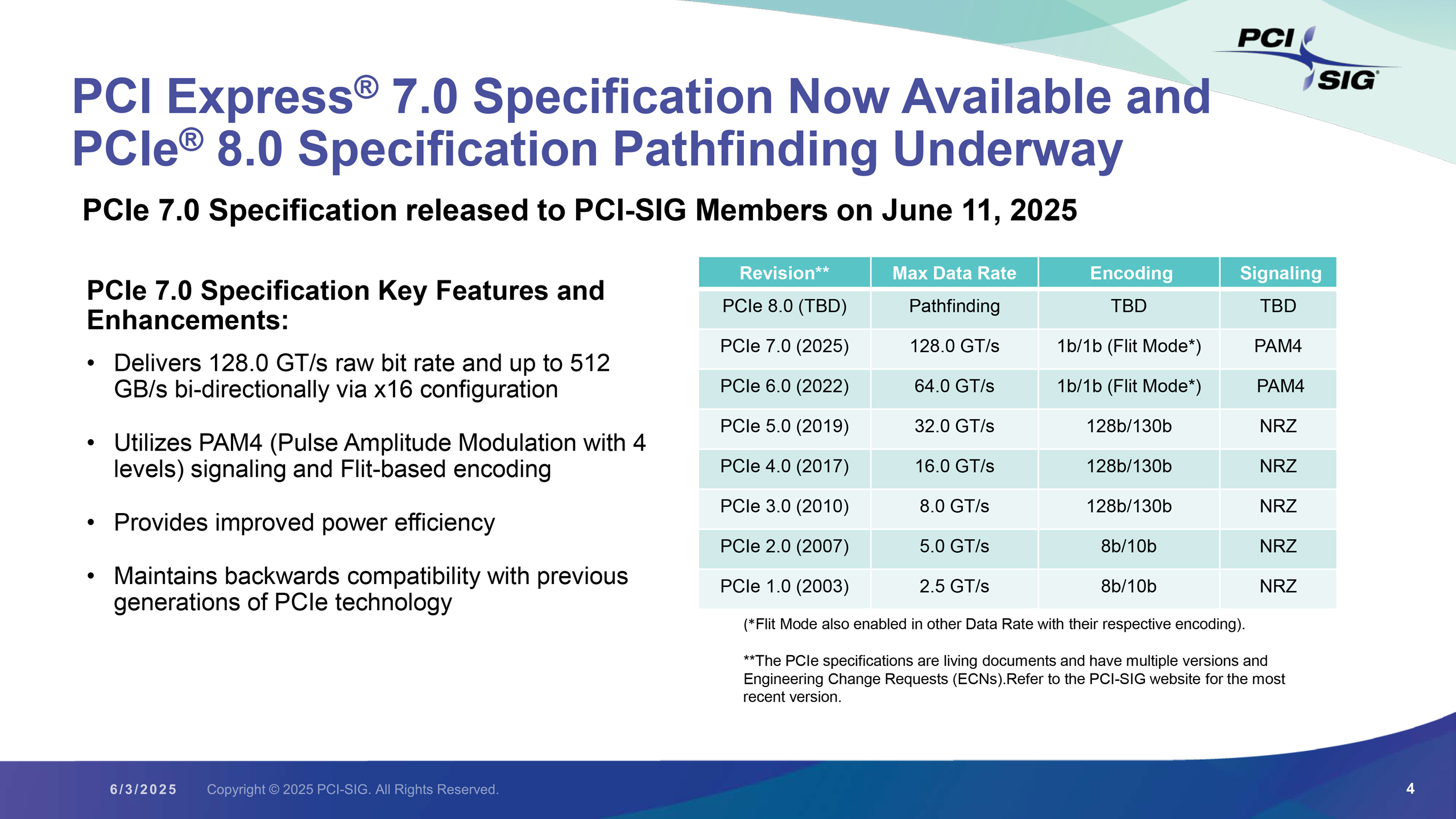

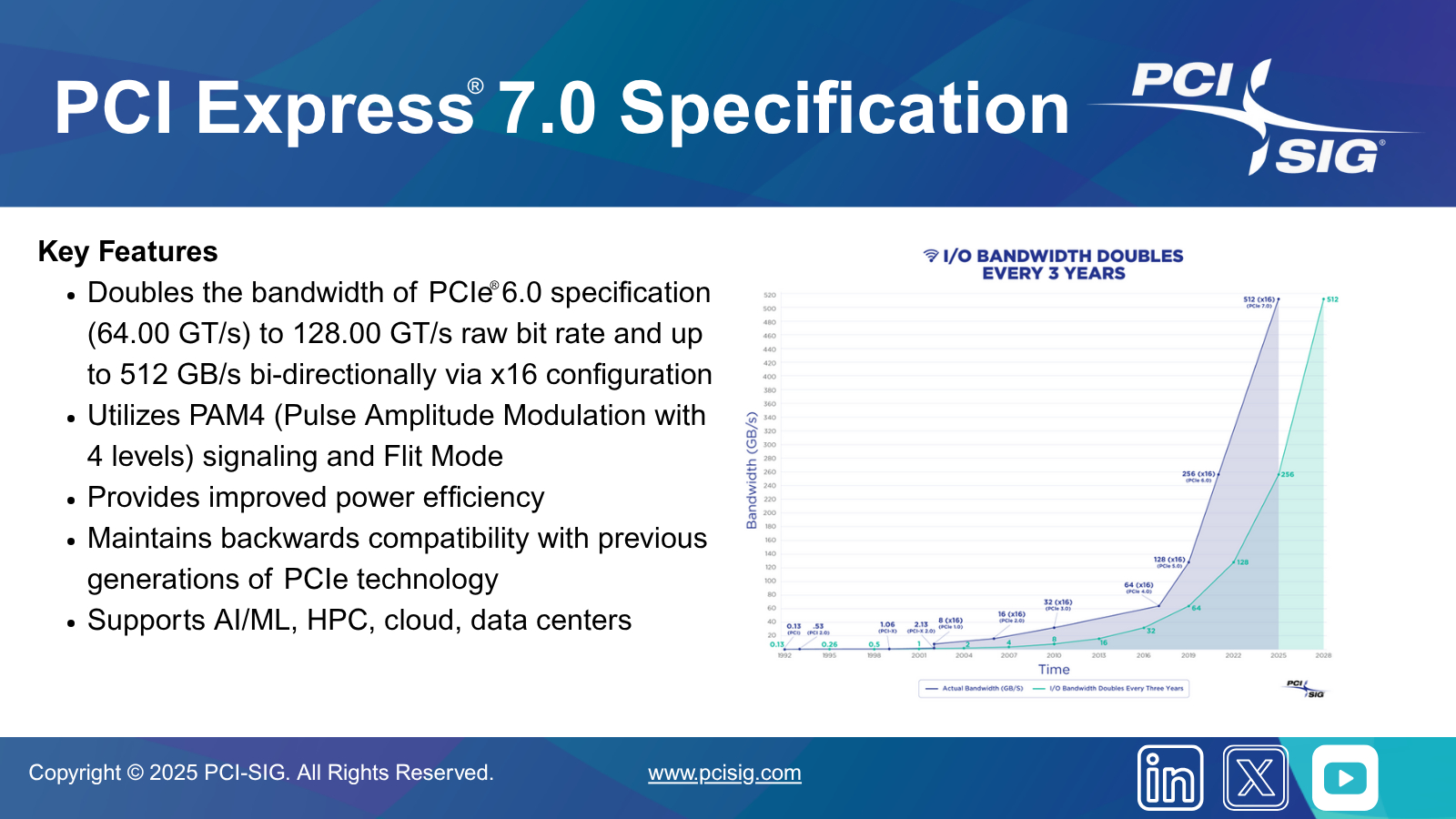

PCI-SIG, which oversees the development of the PCIe specification, announced on Wednesday that it had finalized the PCIe 7.0 spec and passed it to members of the organization, marking a significant milestone in the technology's development. Separately, the company said that it had begun pathfinding for PCIe 8.0, a specification for interconnections that will be used sometime in 2030 or beyond, which may double the performance of PCIe 7.0 and deliver bandwidth of 1 TB/s over 16 lanes in two directions. In addition, the company reiterated plans to start interoperability tests for PCIe 6.0 hardware later this year.

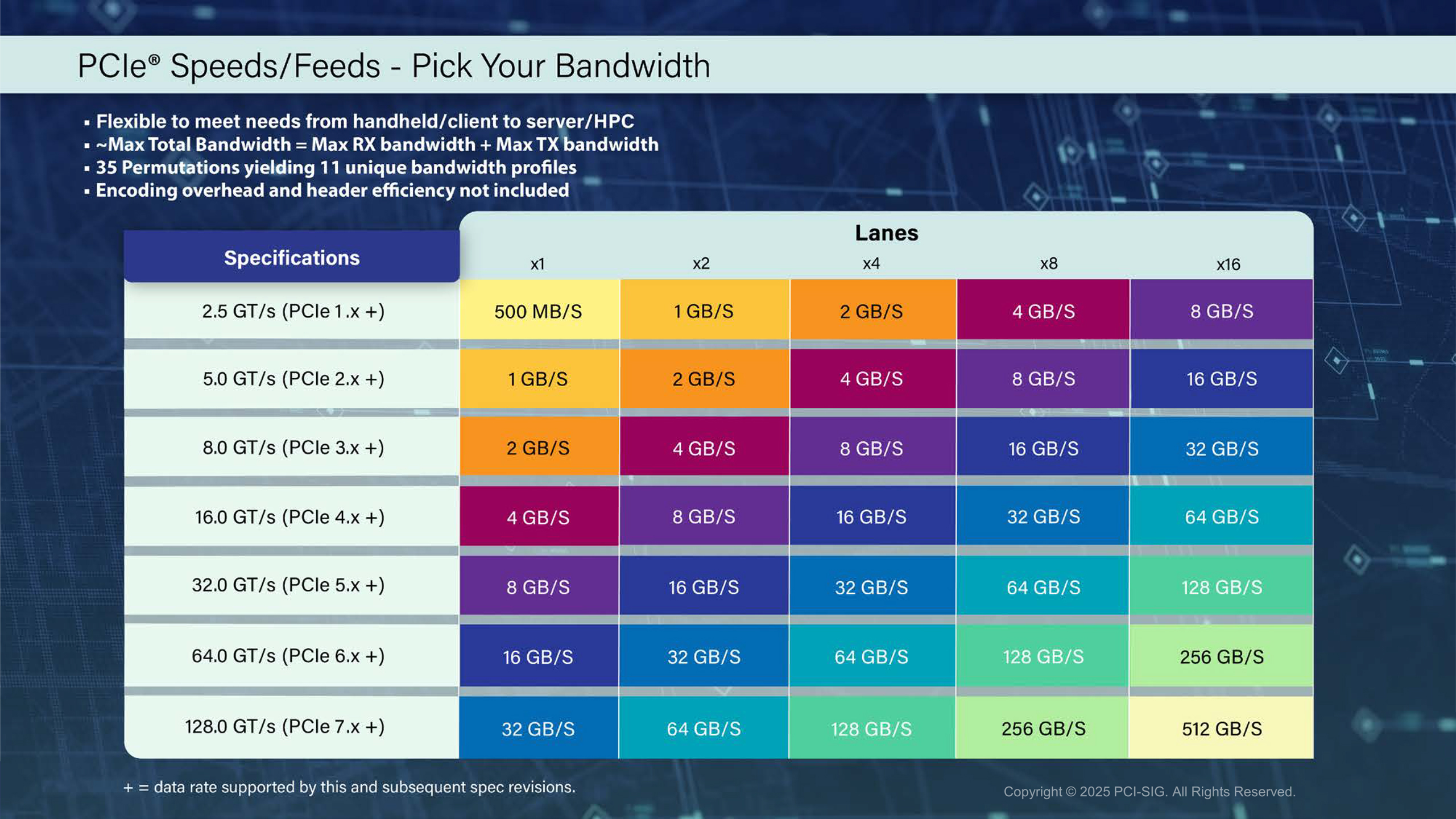

While PCIe 8.0 is still years away, PCIe 7.0 is a lot closer. The PCIe 7.0 specification increases the per-lane data transfer rate to 128 GT/s in each direction, which is twice as fast as PCIe 6.0 supports and four times faster than PCIe 5.0. Such a significant performance increase enables devices with 16 PCIe 7.0 lanes to transfer up to 256 GB/s in each direction, not accounting for protocol overhead. The new version of the interface continues to use PAM4 signaling while maintaining the 1b/1b FLIT encoding method first introduced in PCIe 6.0.

To achieve PCIe 7.0's 128 GT/s record data transfer rate, developers of PCIe 7.0 had to increase the physical signaling rate to 32 GHz or beyond. Keep in mind that both PCIe 5.0 and 6.0 use a physical signaling rate of 16 GHz to enable 32 GT/s using NRZ signaling and 64 GT/s using PAM4 signaling (which allows transfers of two bits per symbol). With PCIe 7.0, developers had to boost the physical frequency for the first time since 2017, which required tremendous work at various levels, as maintaining signal integrity at 32 GHz over long distances using copper wires is extremely challenging.

Article continues belowBeyond raw throughput, the update also offers improved power efficiency and stronger support for longer or more complex electrical channels, particularly when using a cabling solution, to cater to the needs of next-generation data center-grade bandwidth-hungry applications, such as 800G Ethernet, Ultra Ethernet, and quantum computing, among others.

Arguably, the most interesting announcement made today by PCI-SIG is a statement that pathfinding for PCIe 8.0 is underway, and members of the organization are actively exploring possibilities and defining capabilities of a standard that they are going to use in 2030 and beyond. Interestingly, when asked whether PCIe 8.0 would double data transfer rate to 256 GT/s in each direction (and therefore enable bandwidth of 1 TB/s in both directions using 16 lanes), Al Yanes, president of PCI-SIG, said that while this is an intention, he would not like to make any definitive claims. Additionally, he stated that PCI-SIG is looking forward to enabling PCIe 8.0, which will offer higher performance over copper wires in addition to optical interconnects.

" We are hoping [to double performance], but I do not want to make any definitive claims at the moment, but that is our, that is our hope," said Yanes at a press conference. "We do not think optical is going to be the only way. So we are hoping and thinking that we can do electrical, but we do not have a clear answer there. The pathfinding has just started. So, give us a little bit of time to resolve that. But we believe we can do electrical. We do not think it is just going to be optical."

With the PCIe 7.0 standard officially released, members of the PCI-SIG, including AMD, Intel, and Nvidia, can begin finalizing the development of their platforms that support the PCIe specifications. PCI-SIG plans to start preliminary compliance tests in 2027, with official interoperability tests scheduled for 2028. Therefore, expect actual PCIe 7.0 devices and platforms on the market sometime in 2028 – 2029, if everything goes as planned.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

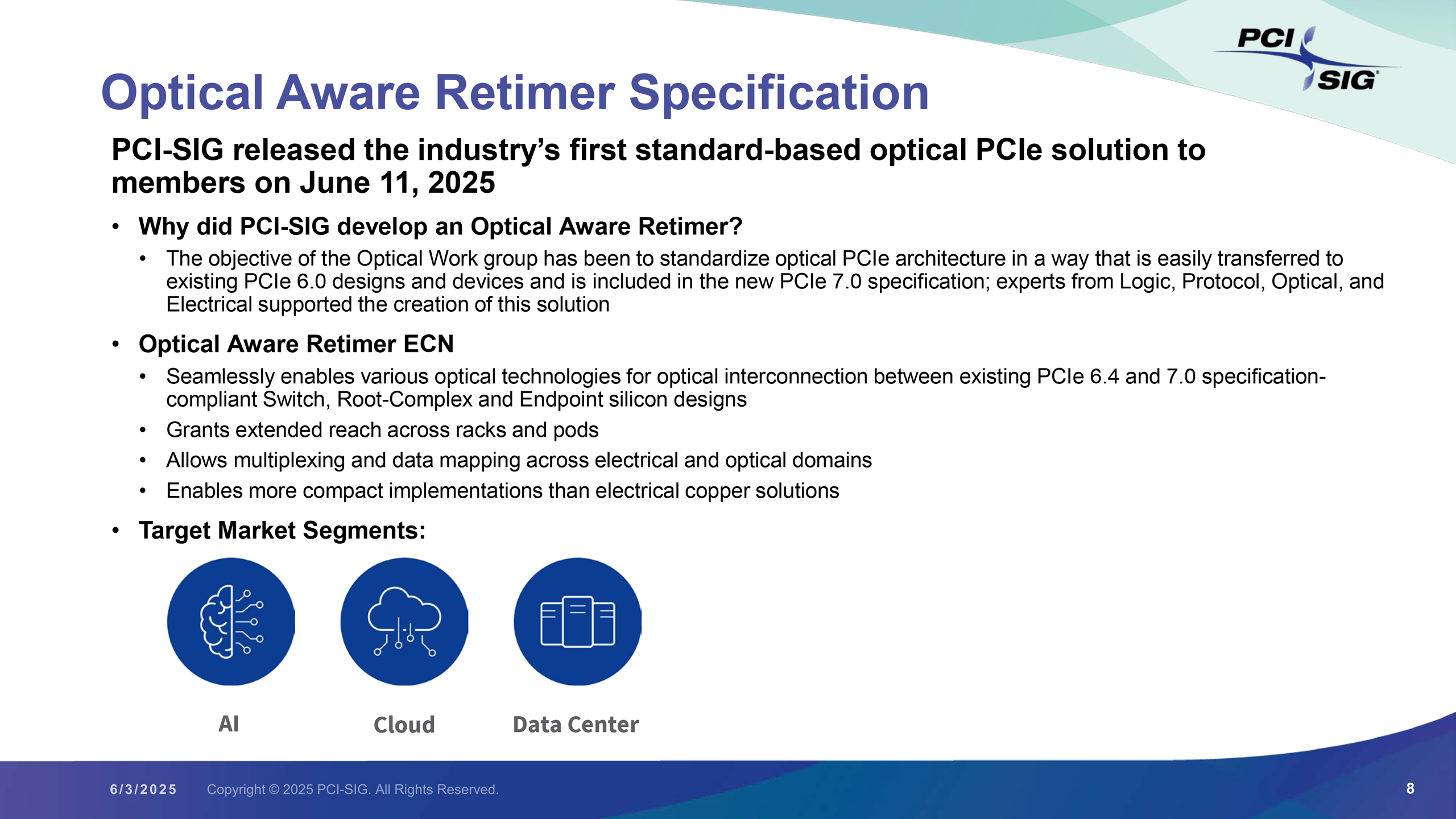

In addition to disclosing milestones for PCIe 7.0, PCI-SIG also re-emphasized plans to officially start Integrators List compliance testing of PCIe 6.0 hardware in 2025, about a year later than expected. Speaking of PCIe Gen6 at large, it is necessary to note that the PCIe 6.4 specification now defines industry-standard ways to use optical technologies between PCIe 6.4 and PCIe 7.0-compliant devices. However, interoperability tests for optical PCIe interconnections are set to start later.

Follow Tom's Hardware on Google News to get our up-to-date news, analysis, and reviews in your feeds. Make sure to click the Follow button.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

bit_user Reply

Uh, you mean 2019. Since PCIe 3.0, 6.0 is the only one that didn't double frequency. 5.0 was completed in 2019.The article said:With PCIe 7.0, developers had to boost the physical frequency for the first time since 2017 -

Pemalite That's more bandwidth than some GPU's. DRAMless GPU's incoming? (Unlikely, bottlenecked by System Memory.)Reply

For the average consumer it's pretty useless at this stage outside of low-PCI-E lane devices like SSD's. -

bit_user Reply

Yeah, that's been tried. Back in the late 1990's, there was an idea that AGP was fast enough to let GPUs use system memory. I think the GPU still had DRAM for the frame buffer, but not much more than that. It didn't work terribly well, IIRC.Pemalite said:That's more bandwidth than some GPU's. DRAMless GPU's incoming? (Unlikely, bottlenecked by System Memory.)

What would kill you is latency. DRAM latency on GPUs is like 200 - 300 ns, but for them to access memory connected to the host CPU would probably almost double that, and could be even worse under high load.

Another bad thing about hitting PCIe that hard is that it'd use more power than accessing memory local to the GPU.

Lastly, it'd be competing with the CPU for memory bandwidth, and thus bogging down any parts of a game engine that are CPU-limited. We already see this with iGPUs, but it'd be even worse with a dGPU.

Yeah, the SMI CEO just said:Pemalite said:For the average consumer it's pretty useless at this stage outside of low-PCI-E lane devices like SSD's.

Wallace C. Kou: For consumer? You will not see any PCIe Gen6 until 2030. PC OEMs have very little interest in PCIe 6.0 right now — they do not even want to talk about it. AMD and Intel do not want to talk about it.

Source: https://www.tomshardware.com/pc-components/ssds/smi-ceo-says-no-pcie-6-0-ssds-for-pc-until-2030-as-nvidia-demands-100m-iops-wallace-c-kou-on-the-future-of-ssds

Just to be clear, he's talking about PCIe 6.0 and you're already thinking about PCIe 7.0. I do appreciate your little thought experiment. But, by the time it's even a relevant question, the bandwidth needs of GPUs will probably have increased to the point where it would make no more sense than it does with PCIe 5.0, today.