Intel's EMIB packaging tech is now supported by industry-standard design and test tools

New set of tools, methodologies, and reusable IP blocks from leading designers coming to Intel Foundry clients.

Intel's embedded multi-die interconnect bridge (EMIB) advanced packaging technology is already used for multiple products designed by the company itself, but its widespread adoption by Intel Foundry customers requires it to be supported by third-party electronic design automation (EDA) tools and reference flows. On Monday, Intel said that software from Ansys, Cadence, Siemens, and Synopsys now supports its EMIB chiplet-to-chiplet interconnections, which is useful for various AI and HPC processors.

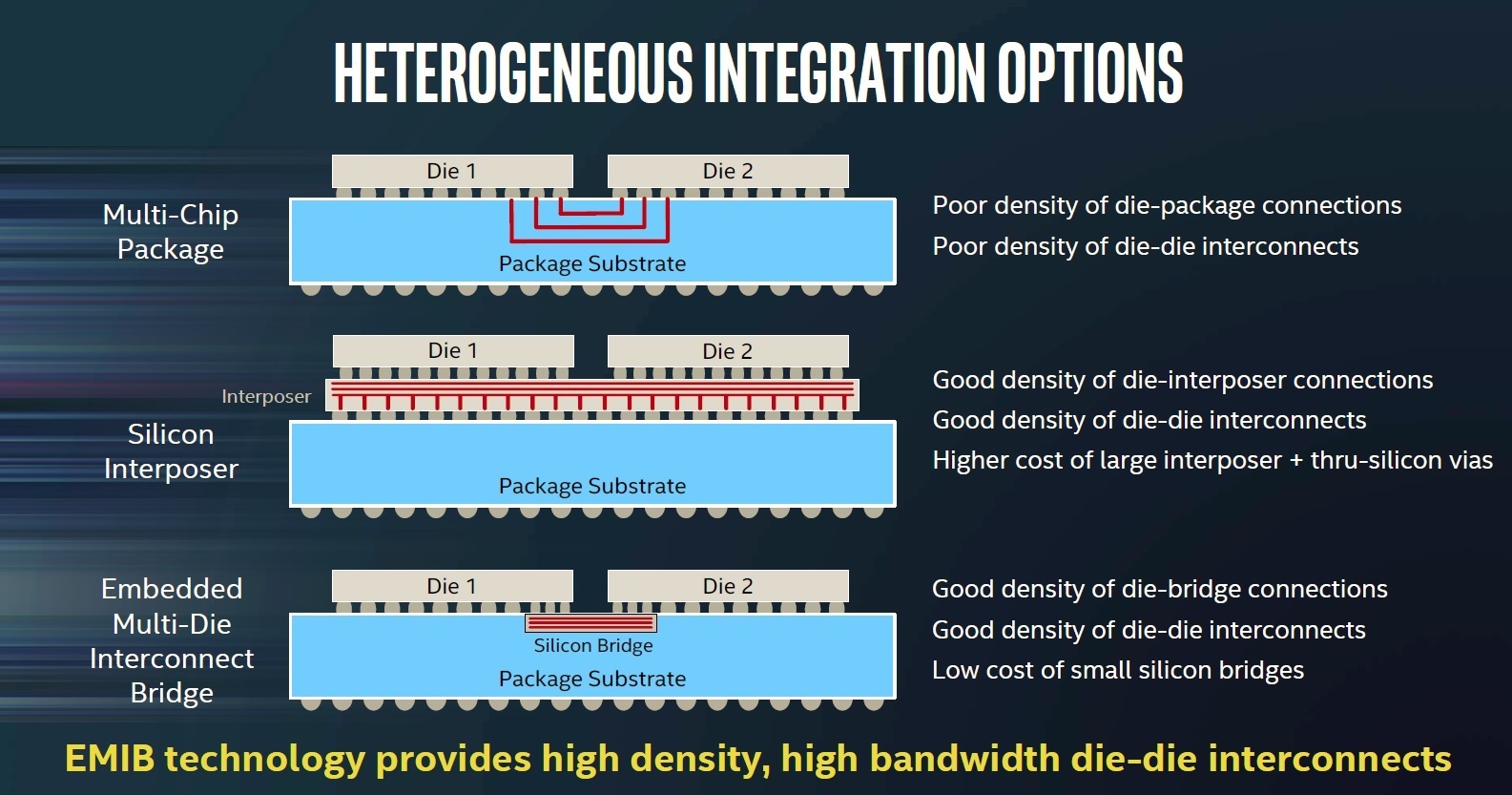

Intel's EMIB technology is designed to connect and integrate multi-chiplet designs in a single package in a relatively simple and cost-effective manner through the use of an embedded silicon bridge that connects chiplets. Intel says that diverse design tools, methodologies, and reusable IP blocks from companies like Ansys, Cadence, Siemens, and Synopsys are now fully enabled and qualified to support customers using Intel EMIB packaging technology for their projects.

Ansys, which mostly specializes in simulation software, has collaborated with Intel Foundry for signoff verification, thermal and power integrity, and mechanical reliability of EMIB technology across Intel 18A process nodes and heterogeneous packaging platforms.

Article continues belowCadence has developed a comprehensive EMIB 2.5D packaging flow and provided digital and custom/analog flows for Intel's 18A node. The company has also made available essential design IP for 18A, which will simplify the development of 1.8nm-class chiplets and perhaps multi-die system-in-packages.

Siemens has introduced an EMIB reference flow for Intel Foundry's customers and achieved certification for its Solido Simulation Suite for custom IC verification on Intel's 16, 3, and 18A nodes. This enhances the range of design and verification tools available to customers.

Synopsys has made an AI-driven multi-chiplet reference flow specifically for EMIB technology available. The optimized reference flow offers a comprehensive co-design and analysis solution using Synopsys 3DIC Compiler to speed up the exploration and development of multi-die designs from silicon to systems. Additionally, Synopsys 3DSO.ai is seamlessly integrated with Synopsys 3DIC Compiler, enabling optimization for signal, power, and thermal integrity, which means significant productivity gains and enhanced system performance for multi-chiplet designs.

"Today's news shows how Intel Foundry continues to combine the best of Intel with the best of our ecosystem to help our customers realize their AI systems ambitions," said Suk Lee, vice president for Ecosystem Development at Intel Foundry.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

By leveraging a comprehensive ecosystem of design tools, flows, and IPs from third parties, Intel Foundry aims to help its customers innovate at every layer of the technology stack. This will ensure that its clients have a comprehensive set of tools to produce designs that rely on IF's manufacturing technologies and EMIB that are set to be made at Intel Foundry.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.