PCIe for Mobile Launched; PCIe 3.1, 4.0 Specs Revealed

The PCI-SIG has launched M-PCIe for mobile devices, and introduced several other specs including M.2, a natural transition from the Mini Card and Half Mini Card.

On Monday PCI-SIG, the consortium you probably know best for the PCI and PCI Express interfaces, outlined its new Mobile PCIe (or M-PCIe) specification for emerging thin laptop, tablet, and smartphone platforms. It also introduced its M.2 specification, a next-generation form factor for thin and ultra-light platforms, and detailed PCIe 3.1, PCIe 4.0, and a Thunderbolt competitor called PCIe OCuLink.

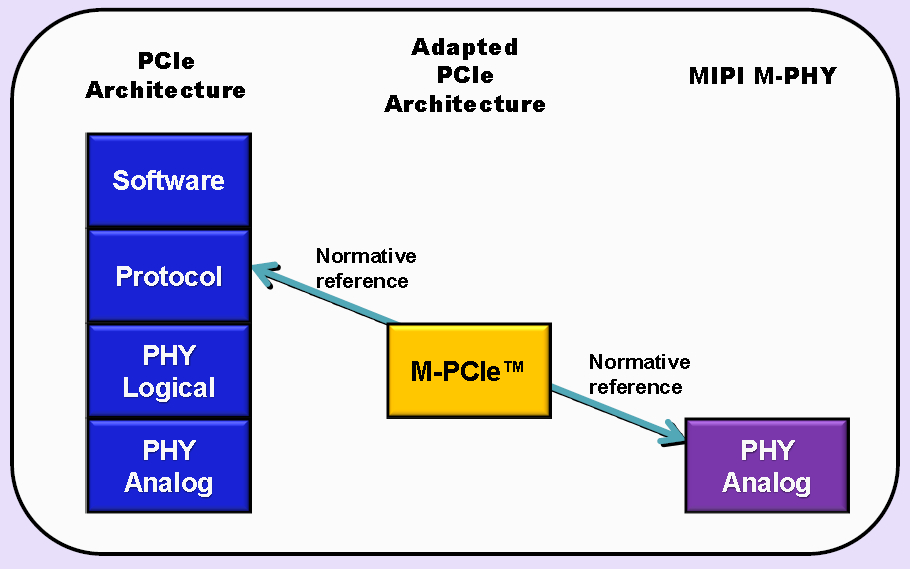

According to the PCI-SIG, the new M-PCIe spec enables PCIe architecture to operate over the MIPI Alliance M-PHY physical layer technology. That means decades of PC-oriented innovations will carry over to upcoming tablets, smartphones, and thin laptops. It also means interoperability and a consistent user experience across multiple platforms.

The M-PCIe spec provides power optimization for short channel mobile platform usage, and scalable performance using MIPI M-PHY high-speed gears 1 (1.25 to 1.45 Gb/s), 2 (2.5 to 2.9 Gb/s) and 3 (5.0 to 5.8 Gb/s). The group said that the M-PHY spec, adopted by the mobile industry, is a proven tech that meets low-power needs of handheld systems. One physical layer for multiple uses preserves investments and expedites time to market.

Article continues below"Our collaboration with the PCI-SIG on the new M-PCIe specification will provide users the best of all worlds, drastically reduced product development and validation cycles, and access to a truly mobile focused physical layer interface technology," said Joel Huloux, chairman of the MIPI Alliance.

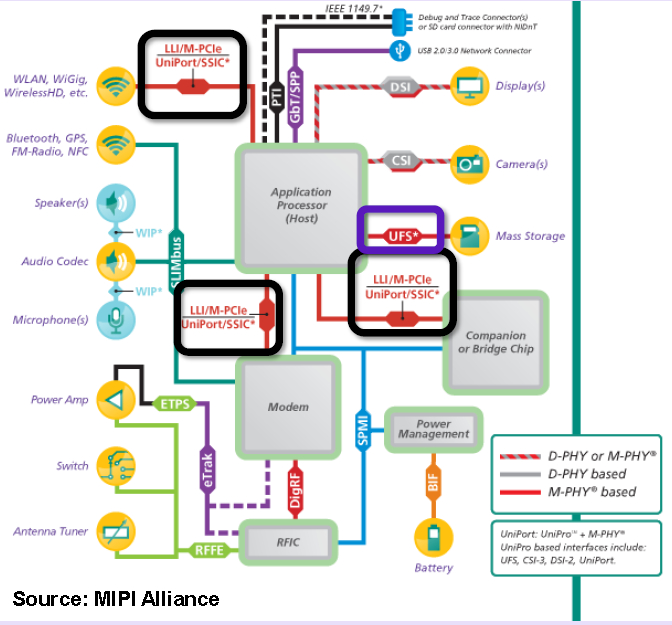

In a diagram provided on Monday (shown below), the M-PCIe/M-PHY combo is used between the SoC and the WLAN/WiGig/WirelessHD component, between the SoC and the modem, and between the SoC and companion or bridge chip. Connections using M-PHY-only reside between the SoC and camera, the SoC and display, the SoC and mass storage, and the modem and RFIC.

As for the M.2 spec, it will serve as a natural transition from the MiniCard and Half MiniCard to a smaller form factor in both size and volume. It will have the flexibility to support high-end performance and provide scalable speed to power-constrained platforms. The spec is also designed as a turnable I/O technology for developers to create a better balance between power and performance. It will support multiple technologies, including Wi-Fi, Bluetooth, SSD, and WWAN.

The M.2 specification is currently at revision 0.7a and is anticipated to be released in Q4 2013. The M-PCIe specification is now available on the PCI-SIG website. ODMs wanting to take advantage of M-PCIe technology need to be members of both PCI-SIG and MIPI Alliance to access licensing rights, membership benefits, and specification evolutions.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

The PCIe OCuLink cable spec was also introduced on Monday, a small cable form factor optimized for internal (PCIe-attached storage) applications and external enclosures. Undoubtedly a Thunderbolt competitor, the spec will include a data rate starting at 8 Gb/s with headroom to scale higher, an independent reference clock with SSC technology, and one external and one internal connector support for up to four PCIe lanes.

The group said that both copper and optical cables are in development, and all cables will support 8 GT/s, providing up to 32 Gb/s in each direction within a four lane configuration. PCIe OCuLink is currently at revision 0.7, and product adoption is targeted for the first half of 2014.

Also revealed was the PCIe 3.1 spec, which consolidates numerous protocol extensions and functionality into three "buckets" including power, performance, and functionality. In the power bucket, the group combines M-PCIe and L1 power management substrates with a CLKREQ# signal. For performance, enhanced downstream port containment and lightweight notification protocol extensions are grouped together. And for functionality, the spec groups together precision time measurement, a separate refclk with independent SSC architecture, and the process address space ID. This spec will be launched later this year, the PCI-SIG said.

Finally, the group revealed the PCIe 4.0 spec, anticipated to offer a transfer rate of 16 GT/s, and address big data applications pushing for increased bandwidth at a low cost. It will be ideal for servers, workstations, and high-performance computing markets, most notably. The spec preserves backward compatibility with previous PCIe versions, and also provides an increase in clock rates thus enabling narrower link width implementations and reduced costs through pin production.

PCIe 4.0 revision 0.5 is targeted for Q1 2014 and revision 0.9 in Q1 2015.

Kevin Parrish has over a decade of experience as a writer, editor, and product tester. His work focused on computer hardware, networking equipment, smartphones, tablets, gaming consoles, and other internet-connected devices. His work has appeared in Tom's Hardware, Tom's Guide, Maximum PC, Digital Trends, Android Authority, How-To Geek, Lifewire, and others.

-

BringMeAnother I'm interested in the OCuLink. Perhaps it will finally give us mass market external video card enclosures if Thunderbolt or USB doesn't get there first.Reply -

vmem hmm, PCIe 4.0... maybe intel can put it on their Haswell-E chipset along with the DDR4 memory? a man can dream lolReply -

SteelCity1981 as of right now unless you are running 3 highend gpus in a crossfire type of setup you will be extremely hard pressed for anything else to saturate pci-e 2.0 bandwidth. now they are talking pci-e 4.0?????Reply -

phatboe When will PCI-Sig release that external PCE cable that they talked about year ago to compete with Thunderbolt?Reply -

alextheblue Finally, an industry standard competitor to Thunderbolt. Too bad it won't hit devices until 2014, more than likely.Reply -

egowhip69 BigMack, while you are probably correct in the desktop / consumer market, for enterprise, more speed is always better, and there will always be cards ready to take advantage.Reply

I just spent several hours in a meeting explaining why a 4 port fiber card wouldn't be any benefit in several of our servers due to their PCIe 2.0 spec. There just wasn't any more speed coming out of the PCIe links. Moving to PCIe 3.0 would have removed that bottleneck, but that means buying a new server. With a 4.0 slot, I could run quad 16Gb links without a bottleneck.

(assuming the cards at 8x electrical... which seems to be a pretty accepted standard for both the server cards and motherboards.) -

__-_-_-__ the external pci-e cables specs have been around since 2009. yet no one implement it. that what's will happen with oculink.Reply

unfortunately thunderbolt is the way to go.