AMD Piledriver Cores to Use Energy Recovery Tech

AMD confirmed that its next-generation Opteron processors and desktop APUs with the Piledriver core will include Cyclos Semiconductor's resonant clock mesh technology.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

In a speech at ISSCC 2012, AMD and Cyclos provided first details about the IP that will be embedded in the Piledriver core to assist in achieving a clock speed that exceeds 4 GHz.

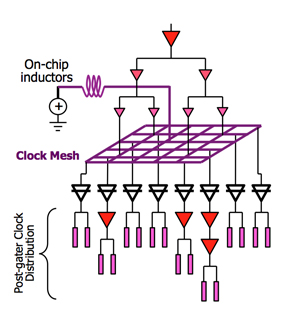

According to Cyclos, its resonant clock mesh (RCM) technology is similar to the technique some hybrid cars use via KERS, short for kinetic energy recovery system. Inductive-capacitive oscillators are leveraged in mesh-based high-performance clock distribution networks to deliver "high-precision timing while dissipating almost no power." In effect, RCM promises to recycle clock power to enable lower power consumption or higher clock speeds. AMD said that the technology result isa 24 percent drop in clock distribution power. The total IC power reduction is, depending on the chip design, estimated between 5 and 30 percent, but will be at the lower end (5 to 10 percent) in Piledriver.

AMD's Piledriver is the first high-volume processor core to use the RCM IP.

Article continues belowGet Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Douglas Perry was a freelance writer for Tom's Hardware covering semiconductors, storage technology, quantum computing, and processor power delivery. He has authored several books and is currently an editor for The Oregonian/OregonLive.

-

Now if only AMD could get Drag Reduction System (DRS) going and up their instructions-per-cycle we could have a great race!Reply

-

de5_Roy amd is making bold claims about power efficiency again.Reply

hopefully they'll do it right this time and not blame on everything else like they did with bulldozer. -

-Fran- chumlyBut will it best a 2500k?Reply

Will the HD4K best the iGPU inside Trinity?

Trade offs mate, trade offs. Trinity is not aimed to the mid/high segments... At least, they should not be :P

Cheers! -

rex86 YukaWill the HD4K best the iGPU inside Trinity?Trade offs mate, trade offs. Trinity is not aimed to the mid/high segments... At least, they should not be Cheers!Reply

I'm not sure they need trade offs. Bulldozer is fine as it is for the most of us. They just need to lower TDP and stuck it in Trinity.