PCIe 6.0 Chip Design Kits Available for Early Adopters

Cadence implements PCIe 6.0 test chip using TSMC's N5 node.

Just weeks after PCI SIG released the final draft of PCIe 6.0 specifications, Cadence introduced one of the industry's first silicon-proven IP packages that enable chip developers to implement PCIe 6.0 support into their designs and test it. The IP is available now and will enable early adopters to add support for PCIe 6.0 to chips due in 2022 - 2023.

"Early adopters have already started exploring with the new PCIe6 specification, and we are looking forward to seeing them achieve positive results with TSMC and Cadence technologies," said Sanjive Agarwala, corporate vice president and general manager of the IP Group at Cadence in a statement.

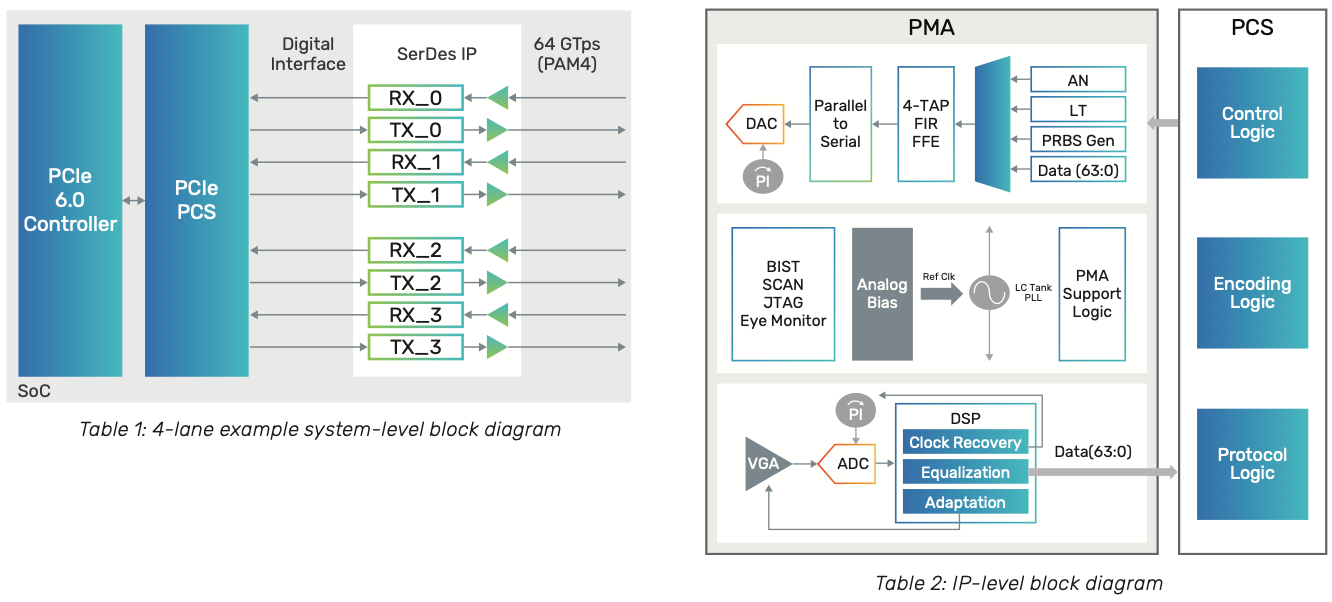

Cadence's PCIe 6.0 IP comprises of a controller and a DSP-based PHY (physical interface). The controller features a multi-packet processing architecture that supports up to 1024-bit wide data path in x16 configuration as well as supports all the key features of PCIe 6.0, such as an up to 64 GT/s data transfer rate (in both directions), pulse amplitude modulation with four levels (PAM4) signaling, low-latency forward error correction (FEC), FLIT mode, and L0p power state.

The IP is designed for TSMC's N5 node and is available to developers of various AI/ML/HPC accelerators, graphics processors, SSD controllers, and other bandwidth-hungry ASICs that need to add support for PCIe 6.0 as soon as possible.

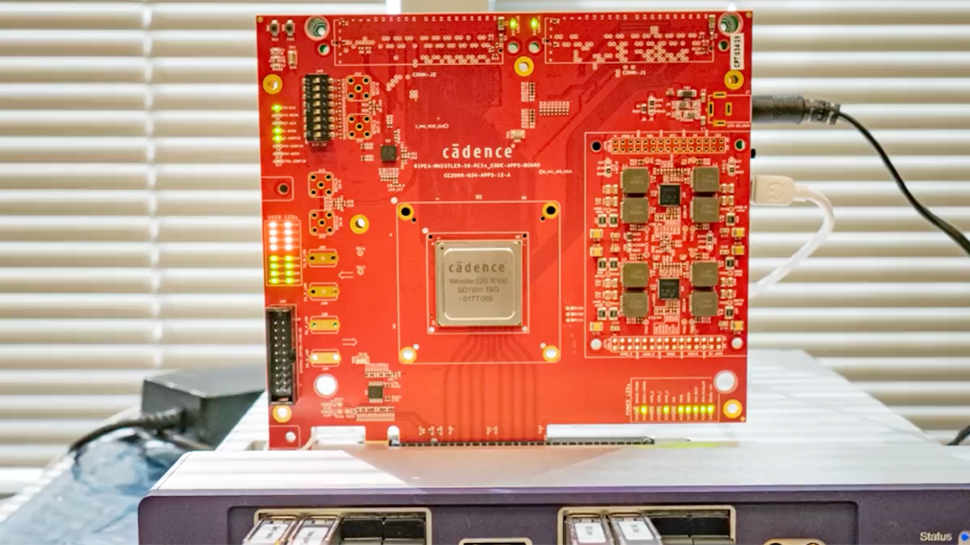

Along with the IP package, Cadence also offers a PCIe 6.0 test chip implemented using N5 and meant to test signal integrity and performance of PCIe 6.0 implementations at all data rates.

The chip contains a PAM4/NRZ dual-mode transmitter that is guaranteed to provide optimal signal integrity, symmetry and linearity with low jitter as well as a receiver that can withstand harsh signal impairments and channel loss in excess of 35dB at 64GT/s to provide sophisticated data recovery capabilities. Since with PCIe 6.0 chip developers will be dealing with data transfers at up to 64 GT/s over relatively long traces (for comparison, DDR5 memory currently has a transfer rate of 4.8 GT/s – 7.0 GT/s), ensuring signal integrity and supporting sophisticated data recovery mechanisms becomes a must.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

"We have been deploying PAM4-based IP since 2019 when we introduced our first-generation 112G-LR SerDes IP, and our vast expertise in PAM4 technology plus our strong collaboration with TSMC provides a robust foundation for success with our PCIe6 products," said Agarwala.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.