Intel Dives Further Into IoT, Announces Cyclone 10 FPGAs

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

The high-volume IoT market encompasses many diverse applications and multiple solutions vie to power the next generation of products. Intel expanded its field programmable array (FPGA) family with the new Cyclone 10, which comes as yet another advantage of its Altera acquisition in late 2015.

Brain drain and R&D stagnation typically impact newly acquired companies, but the (former) Altera team continues to execute well on its roadmap--the new product family comes on the heels of the Stratix 10 FPGA release in October. Low-power FPGAs serve as a key strategic piece for Intel as it restructures and dives deeper into new market segments.

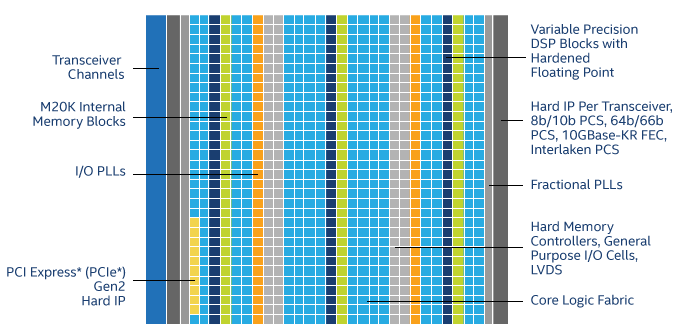

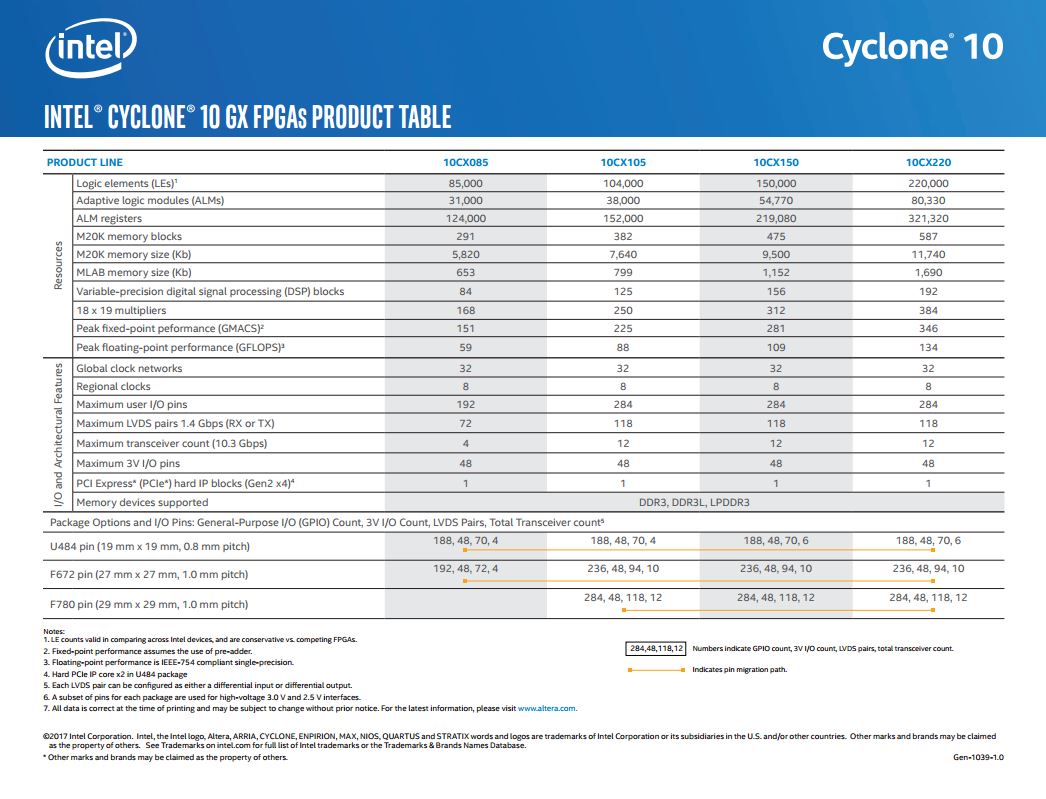

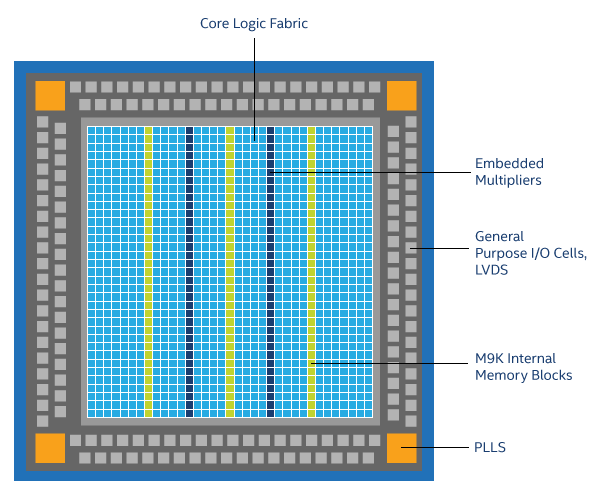

Intel split the Cyclone 10 into the performance-oriented GX and low-power optimized LP series. The GX series uses TSMC's 20nm process and is geared for a number of uses in the industrial, automotive, and broadcast markets. These include machine vision, robotics, infotainment, Advanced Driver Assistance Systems, and audiovisual applications.

Article continues belowThe automotive segment is rapidly growing due to autonomous technologies, which many view as a "future" technology. Autonomous capabilities are actually separated into several levels. Level 5 offers full autonomous driving capabilities, while levels 1 and 2 provide features that are already on the market, such as adaptive lane cruise control, collision avoidance, and automatic parking. Vehicle infotainment applications are also growing rapidly.

Several players are angling for a piece of this sizable market. At Micron's analyst day, it predicted that Level 1 and 2 autonomous features would see a tremendous uptake in 2018 as the technology spreads to lower-priced vehicles. Micron currently has 40% market share of autonomous vehicle memory/storage solutions, but Intel's Cyclone 10 series aims to grab share on the compute side as the company fans out to capture more of the IoT market.

FPGAs offer power to performance advantages compared to some solutions, but they also require more specialized programming for each application. Specialized programming can be a downside, but it fits well into the target markets because the ability to rapidly reprogram an FPGA offers an additional level of flexibility.

The GX series offers twice the core performance of its predecessor and scores an "industry first" for low-cost FPGAs with 10.3 Gbps transceiver I/O support and IEEE 745-compliant hard floating-point DSP blocks. The single-precision floating-point DSP processes at up to 134 GFLOPs. Other highlights include DDR3/L EMIF support and OpenCL support.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

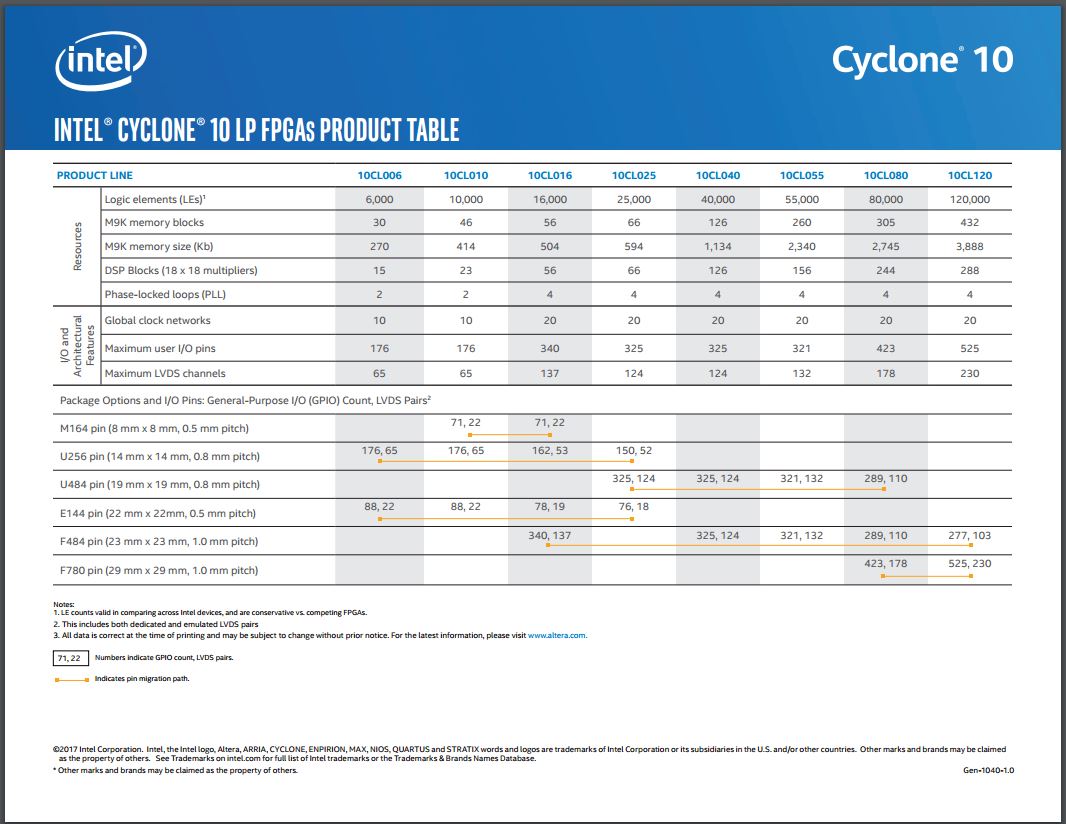

The Cyclone LP slots in for low-cost and low static power applications, such as industrial motor control, interfacing, sensor fusion, and I/O expansion, among many others. It's available in several different temperature grades to support differing commercial, automotive, and industrial applications. Intel claims it consumes up to 50% less static power than its predecessor. The low-power design employs a high-density fabric, memory, and I/O architecture.

Intel's releasing the latest version of Quartus, its FPGA programming software, along with the Cyclone 10 FPGA products in the second half of 2017.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

bit_user Any word on what manufacturing node these use? Can we assume 14nm? Did they release any peak GFLOPS/W or GMACS/W figures?Reply

Thanks for reporting this.

BTW, is there any way to zoom in on the images? I can barely read the charts, and it'd be nice not to have to search for them on Intel.com. -

aldaia ReplyAny word on what manufacturing node these use? Can we assume 14nm?

Acording to public altera info:

Cyclone 10 GX FPGAs are built on a high-performance 20 nm processCyclone 10 LP FPGAs are built on a power-optimized 60 nm process -

Paul Alcorn Sorry about the tables, our image galleries are great to increase the number of images we can show in a small space, but are murderous to text at times. Intel's documentation doesn't share the GFLOPS/W or GMACS/W figures. They are using 20nm TSMC for the GX, and an unspecified 60nm for LP.Reply

I also pulled the images out of the images so they are easier to read, and clickable for larger versions.