Intel Slurps Up Altera Stratix 10 FPGA, HBM, ARM, SoC Alphabet Soup

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Intel's $16.7 billion Altera purchase in late 2015 signaled a shift in the company's strategy to increase its capabilities in several core areas. The acquisition has now borne fruit in the form of the new Stratix 10 FPGA, which surprisingly wields a quad-core ARM Cortex-A53 processor and a dollop of HBM2 memory that offers up to 1TBps of memory bandwidth.

CPUs and FPGAs have slugged it out in several categories as the go-to solutions for high-performance applications, and each has its own advantages. CPUs can perform a wide range of operations and fit into just about any mold, whereas FPGAs have evolved into highly specialized chips that offer power versus performance advantages in targeted applications. CPUs hold the simplicity advantage, as FPGAs require specialized programming to unlock their true potential.

For Intel, bringing Altera into the fold will allow it to grab a slice of the broader FPGA pie while simultaneously infusing FPGAs on-package with its own Xeon products, such as the forthcoming Purley platform. Of course, the broader initiative is to bring FPGAs on-die with the CPU, but the road map for that achievement is cloudy. Intel also has its Xeon Phi line, which provides the company with a diverse stable of products.

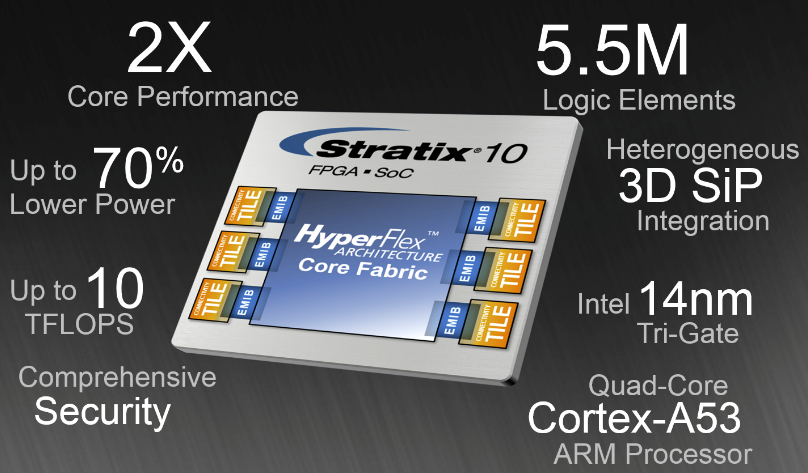

Article continues belowThe Stratix 10 steps into the ranks with up to 10TFLOPS of single-precision floating DSP performance. Four on-package HBM2 components feed the beast with up to 1TBps of memory bandwidth. Intel claims the Stratix 10 offers up to 70% lower power consumption than Altera's previous-generation Stratix V when normalized for performance. At the end of the day, the goal of all compute solutions is to provide the most performance in as dense a package as possible, and Intel claims to have that wrapped up with 5x the density and 2x the core performance of the previous-generation products.

Much of the performance enhancement is borne on the back of the increase to 5.5 million logic elements, which is a significant advantage over the competing Xilinx XCVU13P, which features 3.78 million logic elements. Intel and Altera also noted that the Stratix 10 could be reprogrammed in milliseconds, which is a key requirement for on-the-fly repurposing.

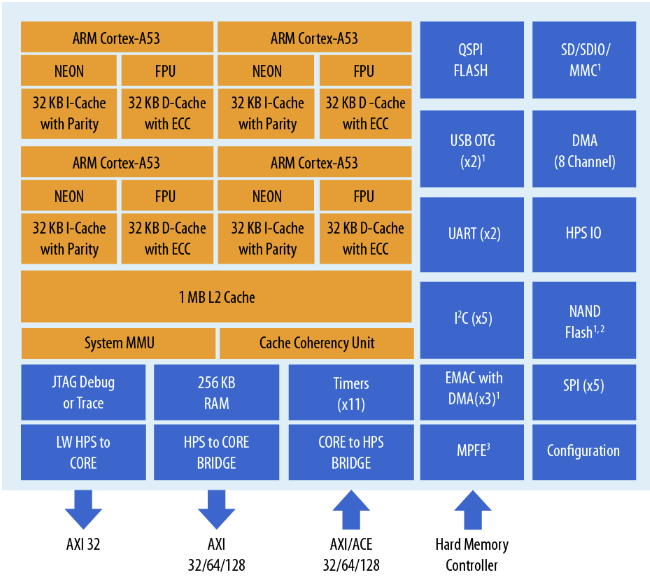

Surprisingly, the Stratix 10 SoC also features an embedded quad-core 64-bit ARM Cortex-A53 processor (up to 1.5 GHz); one would have imagined that Intel would bring its own Atom processors into the mix. Much ink has been spilled on the ARM and Intel wars, so the Cortex-A53's presence on the Stratix 10 SoC is an interesting development. Business makes for strange bedfellows; it's likely that the Stratix 10 was already well under development when Intel purchased Altera, which means we might see the switch to x86 processors in future Altera FPGAs.

Most acquisitions (well, at least the good ones) provide both companies with tangible assets that promote their existing technologies. Altera made its quasi-debut as an Intel company when it presented at IDF 2016 in August. During the session, company representatives hailed the access to Intel's semiconductor prowess and processes as a key win that will allow Altera to accelerate its own developmental process. The new Stratix 10 serves as a good example of that collaboration, as Intel built it on its own second-generation 14nm 3D tri-gate process (this likely denotes the 14nm+ process). Intel also brings a wealth of engineering talent to the table. The new Stratix 10 features a "revolutionary" new HyperFlex architecture, which provides additional performance and power efficiency by streamlining the registers (Hyper-Register), enhanced core clocking (localized clock trees that reduce skewing), and Hyper-Aware design flow (a "Fast Forward Compile tool").

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Microsoft recently announced that it's using FPGAs as the bedrock of several facets of its cloud and Bing infrastructure. The move is largely due to FPGA reprogrammability, which allows data centers to alter their use case on the fly, and there are several large data center operators that will serve as tasty targets for Intel's latest FPGAs. The fusion of on-die FPGAs with Xeon CPUs will bring forth perhaps the greatest advantages in terms of flexibility, which means that Intel could also use the Altera FPGA architecture as a stepping stone into new segments, like the burgeoning machine learning market.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

Paul Alcorn Reply18721939 said:quad-core ARM Cortex-A3 processor

It's clear from the diagram, but should be A53.

Good eye, I had it listed correctly later on, but missed one, Thanks, fixed! -

wifiburger oh... altera, reminds me of VHDL in college, programming for that thing, most interesting was a pong clone,Reply -

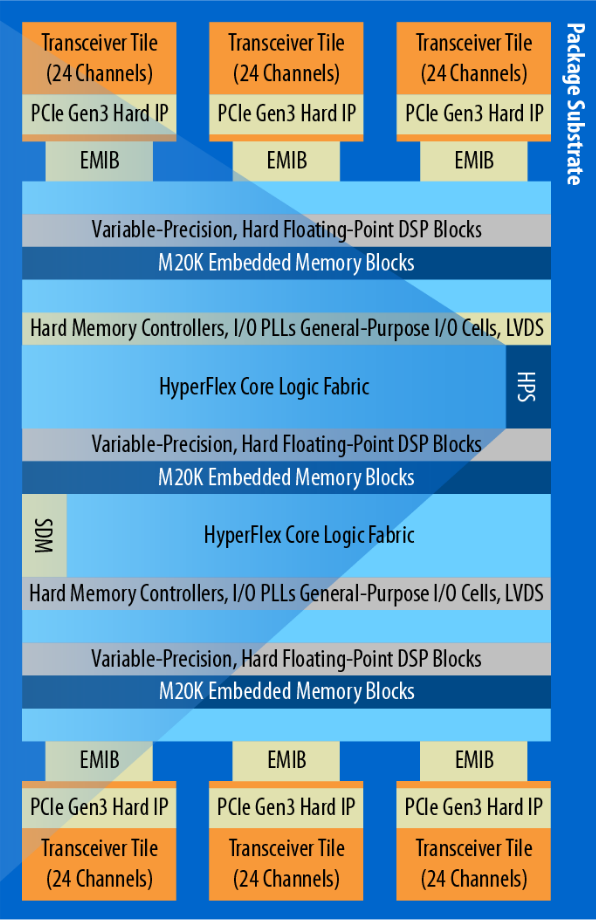

bit_user In the first diagram, EMIB is Embedded Multi-die Interconnect Bridge. SDM is their Secure Device Manager block. HPS stands for Hard Processor System, which refers to the quad-core ARM block shown in the second diagram. I still don't know how the HBM is connected, but maybe it's just attached to the fabric, so you can decide how you want to use it.Reply

Also, they claim 80 GFLOPS per Watt! Compare that to Nvidia's Pascal P100, which gets only 35 GFLOPS per Watt. That's close to an apples-to-apples comparison, as both have HBM2. But even the GP102 (the new Titan X GPU), only gets about 44 GFLOPS per Watts. Until I saw that, I wasn't particularly impressed.

You can read more, here:

https://www.altera.com/products/fpga/stratix-series/stratix-10/overview.html -

bit_user Reply

I think you're trying to be poetic, but it fails to impress if your comments are incoherent.18722569 said:im still romantically involved with zilog z8000 the shear power of it awesome

to bad zilog poof vaporized instantly

but this new chip is worthless without a instruction set to make the sparks fly -

Jason_V The ARM core shouldn't be surprising as that's been the embedded FPGA processor of choice for a long time and it was in-plan prior to the Intel acquisition.Reply

Intel is expanding their moat. It'll be interesting to see if it's FPGA's time in the sun and how Intel will use them or make them available to their customers. Also, what will these devices cost? A 5.5 million element FPGA is not a cheap piece of silicon. -

computerguy72 PATLMMM - Could you possibly add some more spelling and grammatical errors to your posts? Your posts come across very trollish and are so badly written it really diminishes you and whatever your agenda is. Considering these chips are multiple orders of magnitude faster and more efficient over the last 10 years I think describing the industry as needing to mature dramatically (and comparing their efforts to a 'fungus') is not supported by the facts. Reading your posts making me embarrassed for you.Reply -

bit_user Reply

Don't be. I think he's not a troll, but also not serious. Every time one of his posts starts to make sense, there's something stuck in there to completely derail it.18725330 said:Reading your posts making me embarrassed for you.

I think he could find a better community, elsewhere. I'm sure there are others who'd appreciate his posts more than we do.