Micron 64 Layer NAND Coming To Market; GDDR6, Next-Gen 3D XPoint, QLC NAND In Development

Micron laid out plans for its 64-layer NAND and GDDR6 at its 2017 Analyst Conference. It also announced that it's already developing the next two generations of 3D XPoint and a new, faster memory that will be more competitive with DRAM. Speedy memory aside, Micron also briefly mentioned that it is in the process of developing QLC NAND for the other end of the performance spectrum.

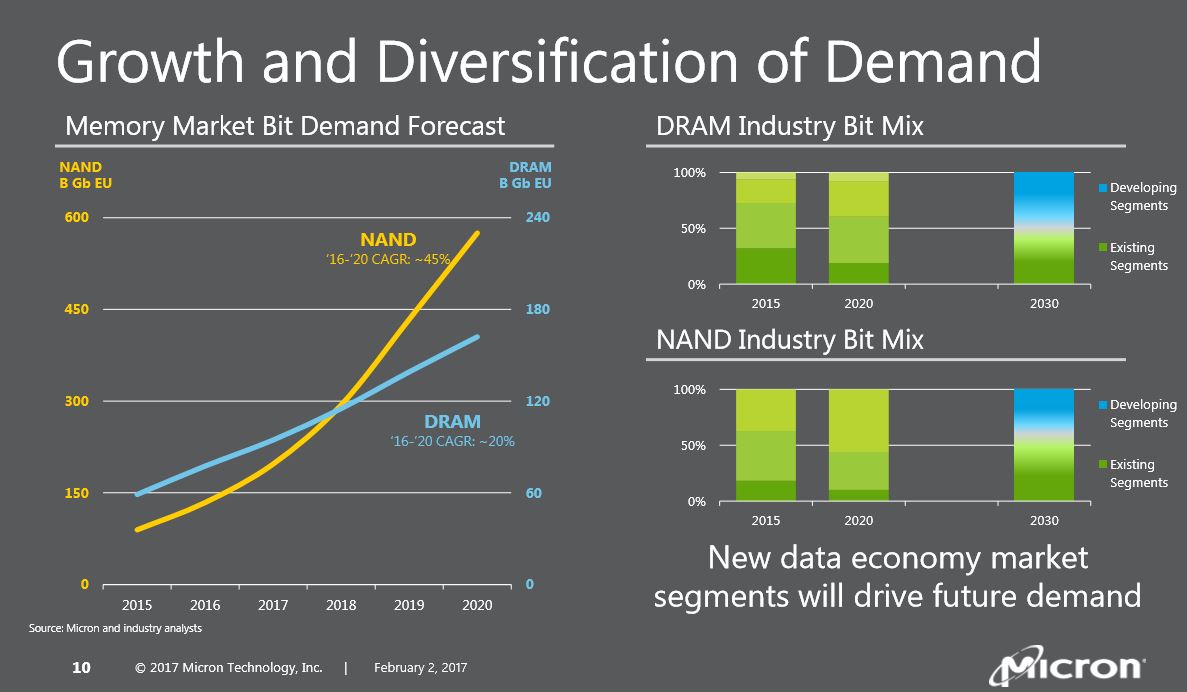

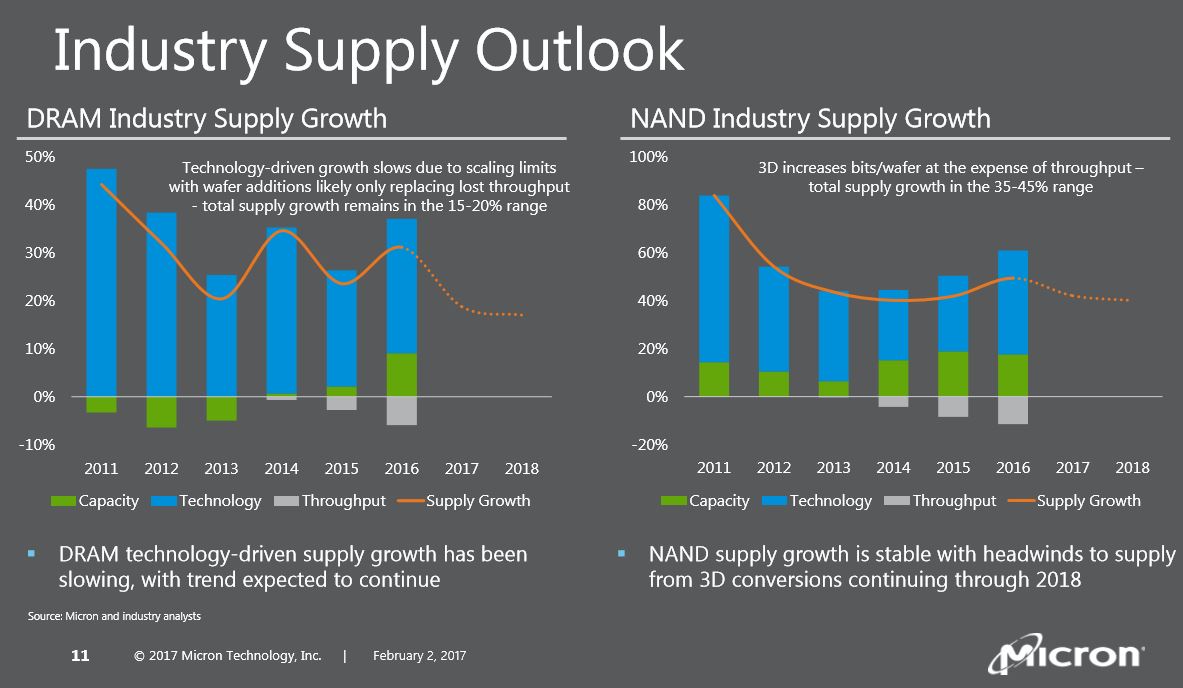

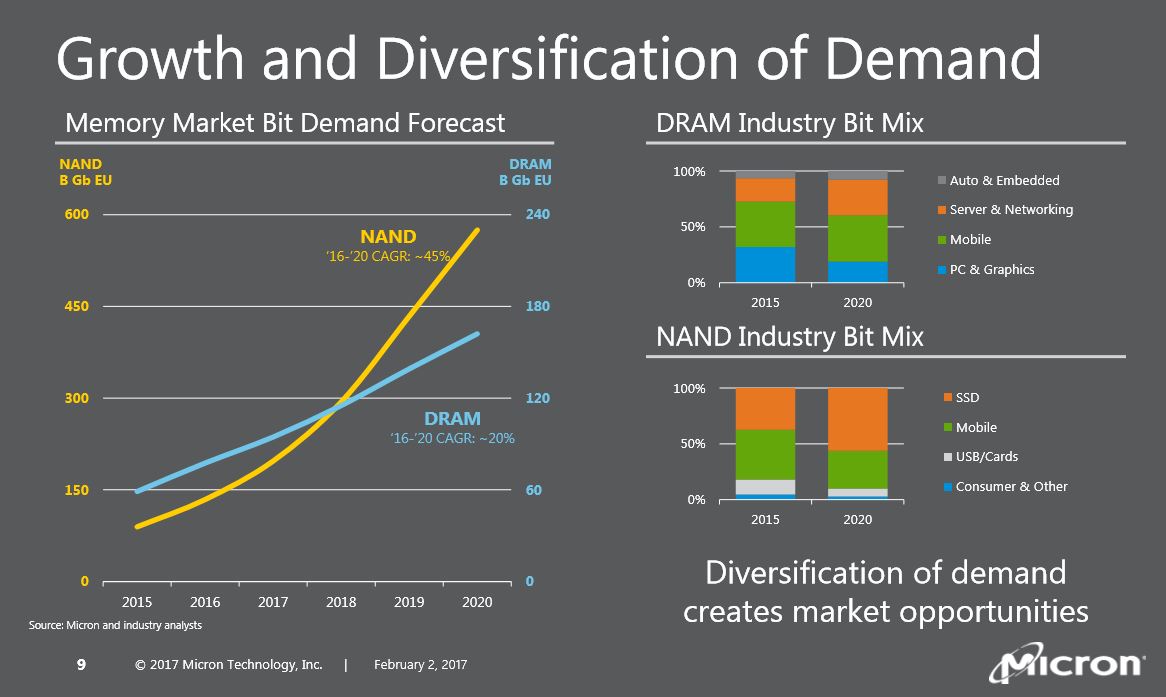

The NAND industry is already in the midst of a shortage, and a DRAM shortage is developing that will extend into Q2, as well. Shortages tend to punish smaller third-party vendors but reward fab-enabled companies with higher margins. The industry's supply challenges are actually good news for Micron, which has a lineup of new NAND and DRAM solutions. The company is also working to identify and address new emerging market segments while laying the groundwork for its other initiatives.

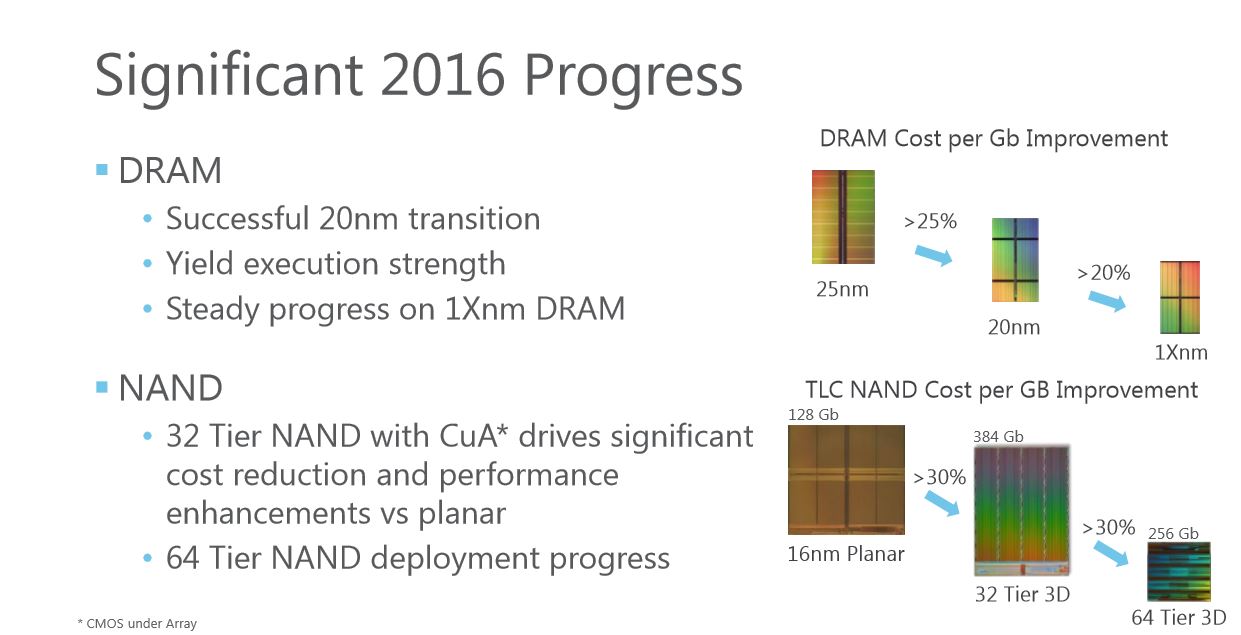

Micron's Year In Review

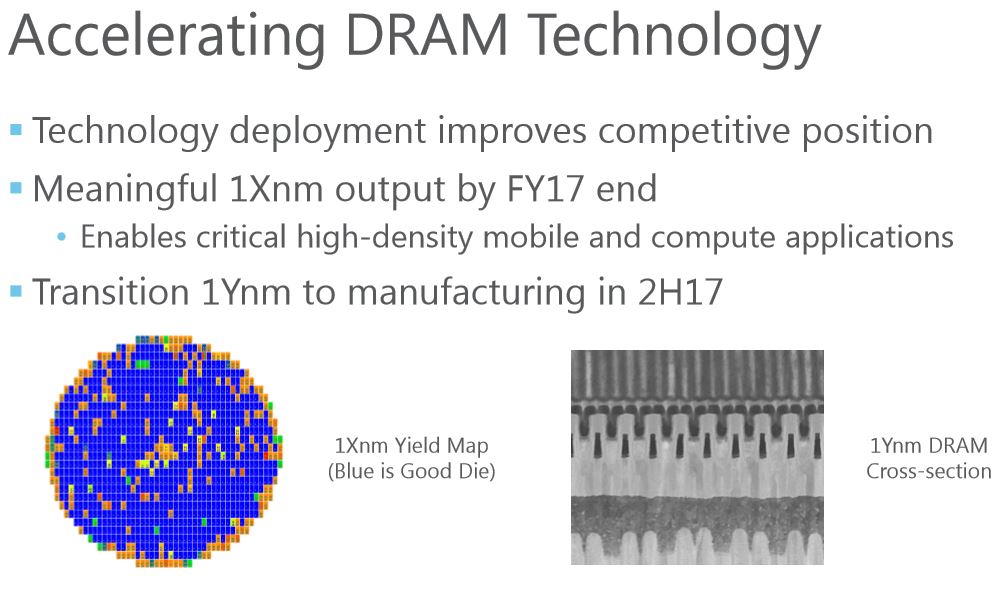

Micron outlined its progress over the year, which includes the transition to 20nm DRAM and its continuing work on its 1Xnm DRAM. Each successive drop in lithography pays dividends with reduced fabrication costs, such as the 25% savings from 25nm to 20nm and the projected drop of an additional 20% as the company ramps 1Xnm DRAM production. Lithography shrinks make manufacturing more economical, but with DRAM tightness already taking hold, some of those cost reductions likely won't make it to the consumer.

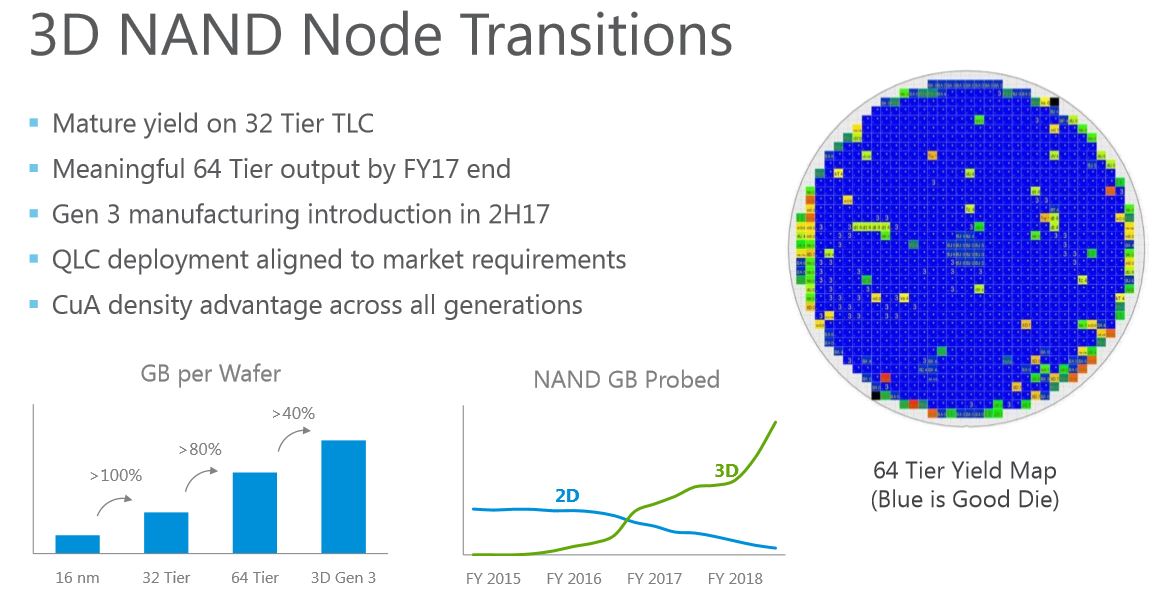

IMFT's 32-layer 3D NAND rollout has been successful, and Micron achieved bit crossover with its 2D NAND products, which means that it's now shipping more 3D NAND bits than 2D NAND. Keeping things in perspective, it's relatively easier to produce more 3D bits than 2D, which has a smaller 128Gb die. Micron's 3D TLC NAND has an odd (but large) 384Gb die capacity, so each wafer yields more capacity than a 2D NAND wafer. The difference in density means that Micron likely isn't producing more wafers of 3D NAND than 2D, but it's surely only a matter of time.

Micron realized a surprising 30% cost reduction when it transitioned from 16nm TLC to the complex 32-layer NAND. The savings exceeded Micron's 25% projections, and the company is experiencing the same yields as MLC with TLC. Micron also stated that it isn't having the production issues that other vendors are with competing 48-layer products, which may be a thinly-veiled swipe at Samsung and WD/Toshiba's somewhat slow 48-layer ramp.

Mark Durcan, Micron's CEO, also announced his retirement at the event. Durcan worked his way up at Micron over a 30-year span and had planned to retire five years ago. Durcan was pressed into service when the previous CEO, Steve Appleton, died in a plane accident. Durcan helped reshape the company over the last several years and had overseen the development of several critical technologies. Durcan will stay with the company until the board selects his successor.

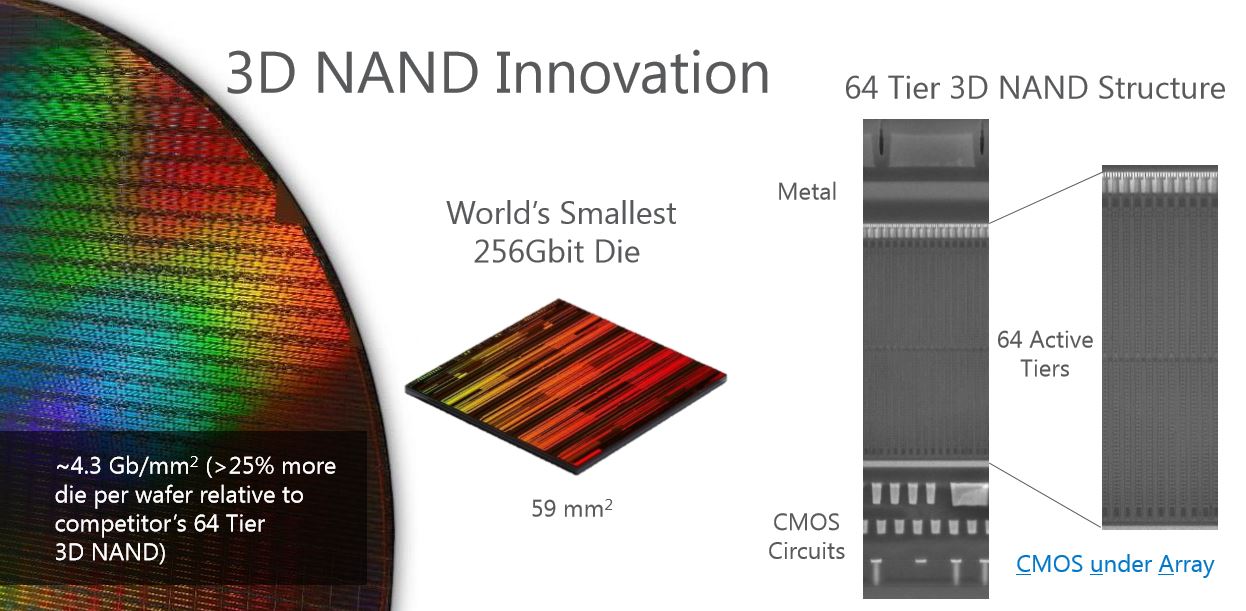

The New NAND Bits

Micron's CuA (CMOS under Array) technology places the control circuitry underneath the die, but competing 3D NAND products still place the circuitry on the periphery. As a result, Micron claims its 64-layer will be the densest with a 59mm2 die and thus provide 25% more die per wafer than competing 64-layer products. Micron produces two different die for its current 32-layer 3D NAND. Its smaller 32-layer die measures 60.217mm2, which is already the smallest 3D NAND die on the market. The differing die sizes allow Micron to address both space-constrained and mainstream markets. Micron will also have a 512Gb 64-layer TLC NAND die, but it's unclear if it will produce other capacities. It's notable that many of Micron's competitors haven't publicly stated their die size.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Micron's 64-layer NAND will produce 80% more GB per wafer than its predecessor, and it also denotes a return to a "standard" 256Gb die capacity. The company expects to realize another 30% cost reduction as it transitions to 64-layer. The yield map paints a pretty convincing picture for 64-layer NAND, which Micron noted has comparable yields to its 2D NAND products. The company is plowing forward with initial 64-layer production in the second half and plans for meaningful output by the end of the year.

Micron included its Gen 3 NAND on the roadmap but remains mum on its layer count and schedule. We do know that fabs will take longer to develop new 3D NAND revisions than the frantic pace seen with 2D lithography shrinks, so it might be a late 2019 product. Micron repeated its earlier announcement that it's also developing QLC (Quad Level Cell) NAND but tossed out the tidbit that it will employ CuA technology. QLC NAND will store four bits per cell, and physics dictates that it will have less endurance and performance than its MLC and TLC counterparts. Unfortunately, Micron didn't provide further details, but we expect QLC to make its debut next year from either Micron or Toshiba.

The Memory Bits

Micron plans to have meaningful 1Xnm DRAM output by the end of the year, but the 1Ynm transition will start in the second half. Micron also provided a yield map for its 1Xnm DRAM that isn't nearly as impressive as its NAND yield map, which highlights the challenges associated with DRAM production.

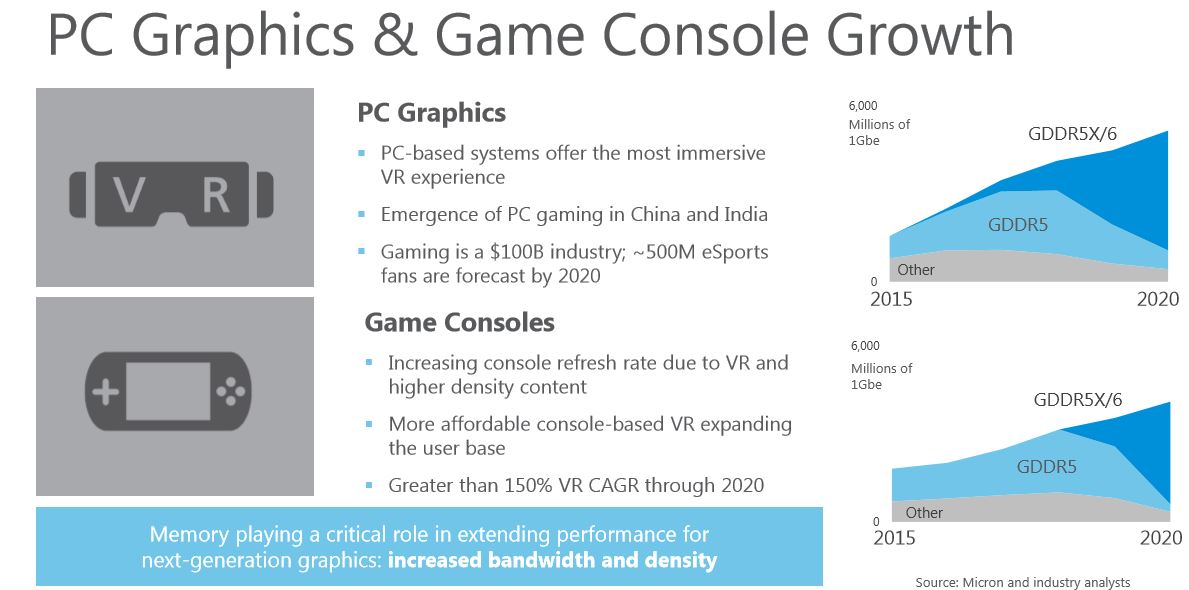

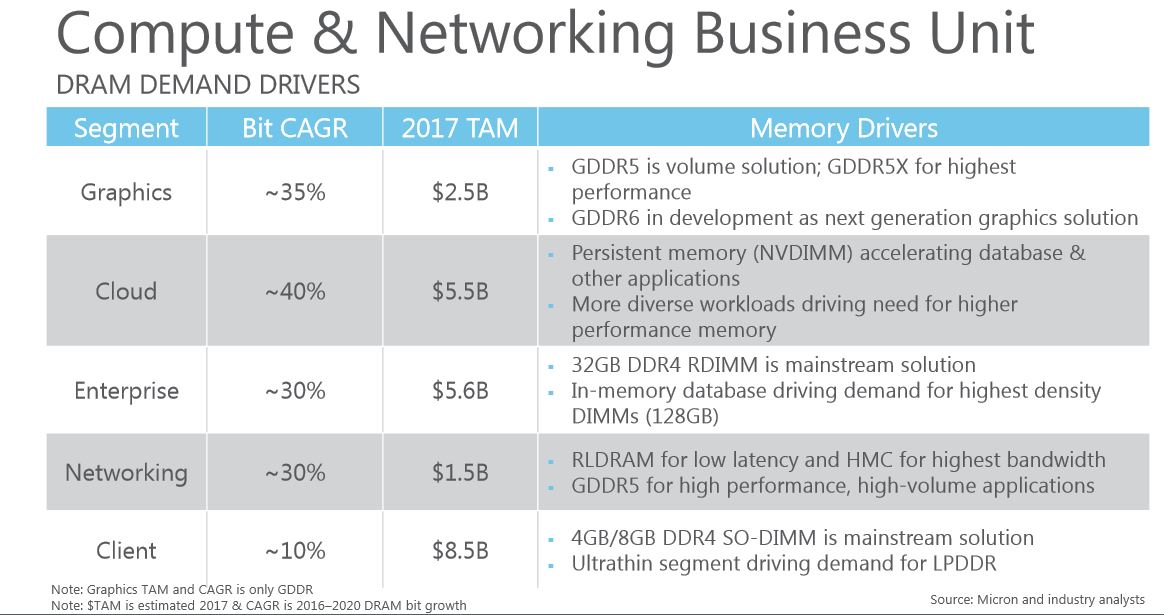

The consumer PC market is suffering a well-publicized downturn, but it still accounts for over $8.5 billion in sales per year, making it Micron's leading DRAM segment by far. Other segments, such as the cloud and enterprise, are experiencing much faster growth but are comparatively small markets. While the mainstream PC market declines, the PC graphics segment is fueled by a $100 billion per year gaming explosion. In the past, users updated their game consoles every seven years on average. New capabilities like VR/AR/MR have reduced the "refresh rate" to three years, so game consoles are also growing.

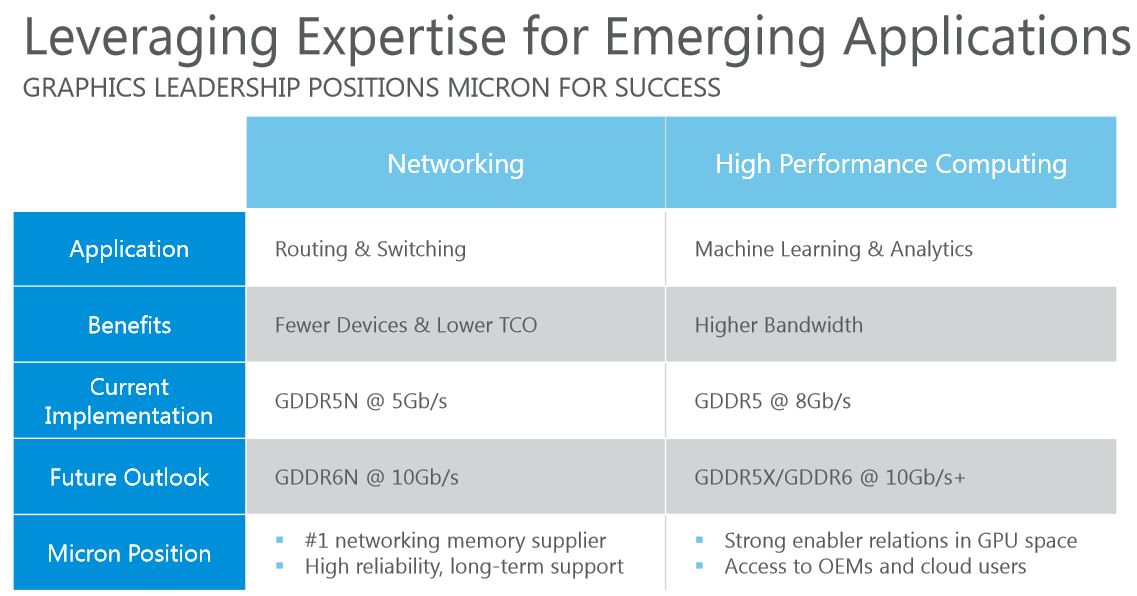

Micron's GDDR provides a strategic advantage not only because it allows the company to find a home in GPUs and consoles, but also because of networking solutions use the "N" variants heavily. Networking is obviously growing due to the rise of mobile and cloud. GPUs are also redefining data center architectures as machine learning grips the industry, so uptake is accelerating rapidly. Autonomous vehicles already use GPUs as well, adding more guaranteed growth to the GDDR market.

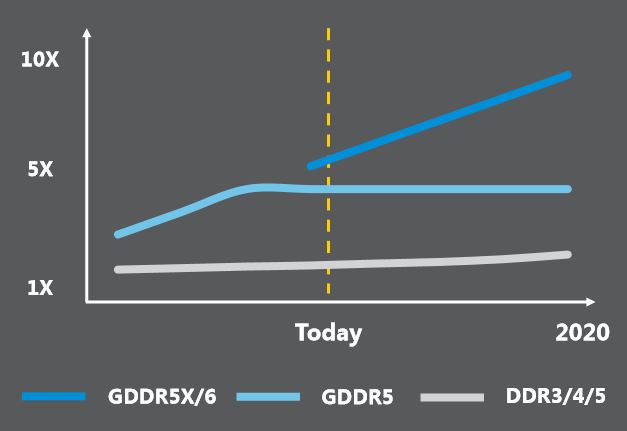

Micron's initial GDDR5 products provided 4Gb/s per pin, which is 2.5X more bandwidth than DDR3. Micron's continued refinement has increased GDDR5 throughput to 8Gb/s per pin, which is ~5X the throughput of DDR4. GDDR5X increased speeds to 10Gb/s per pin, and Micron is already moving it to the 1Xnm lithography.

GDDR6 comes with a big jump to 16Gb/s per pin, or ~10X faster than mainstream memory. Micron hasn't given a firm GDDR6 release date, but we expect it to hit the market by the end of the year. Micron also stated that TSV DRAM is generating a lot of interest, and the company is ramping products for later this year.

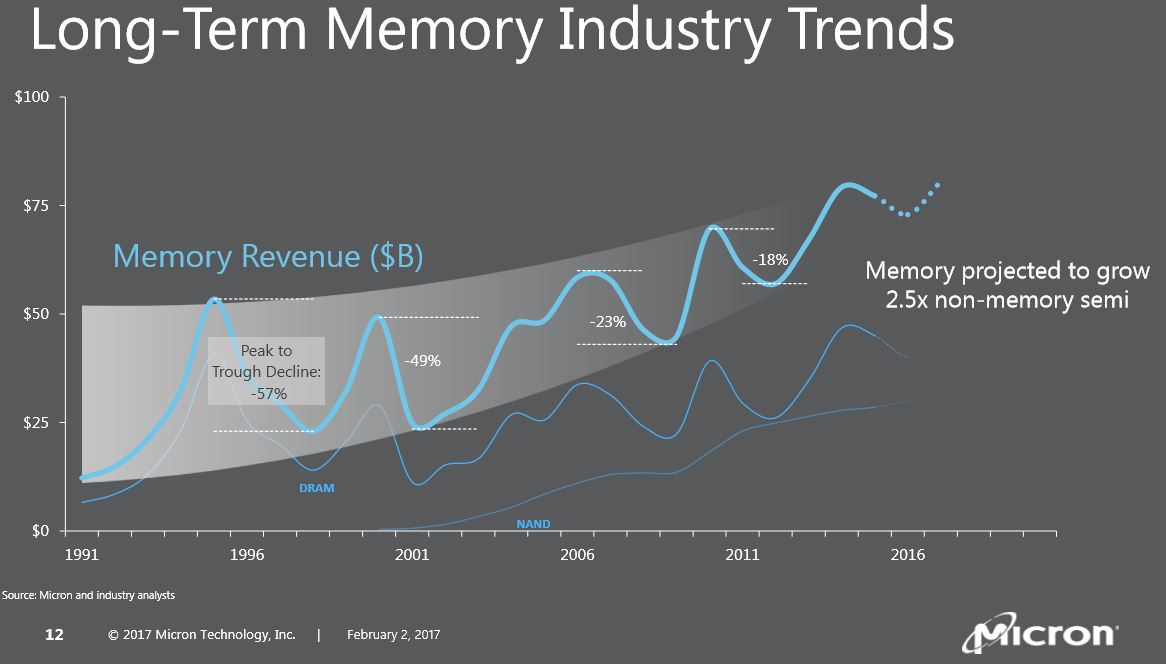

Overall, the market is becoming less volatile due to consolidation in the memory industry, which now has a group of "rational actors" that don't build unneeded production capacity. The overall memory market has suffered smaller swings as the years progressed, and a glance at the DRAM trendline shows that it tends to suffer the most volatility. NAND is much more stable, but Micron expects both DRAM and NAND demand to continue to outstrip supply.

The rise of Tsinghua has a new and potentially irrational actor with deep pockets entering the NAND market. That might upset the orderly memory oligarchy. During the Q&A session, Mark Durcan stated that barring a licensing deal from an established vendor, he doesn't feel that Tsinghua will become competitive with the incumbent NAND fabs for 3-5 years.

All Quiet On The New Memory Front, Kinda

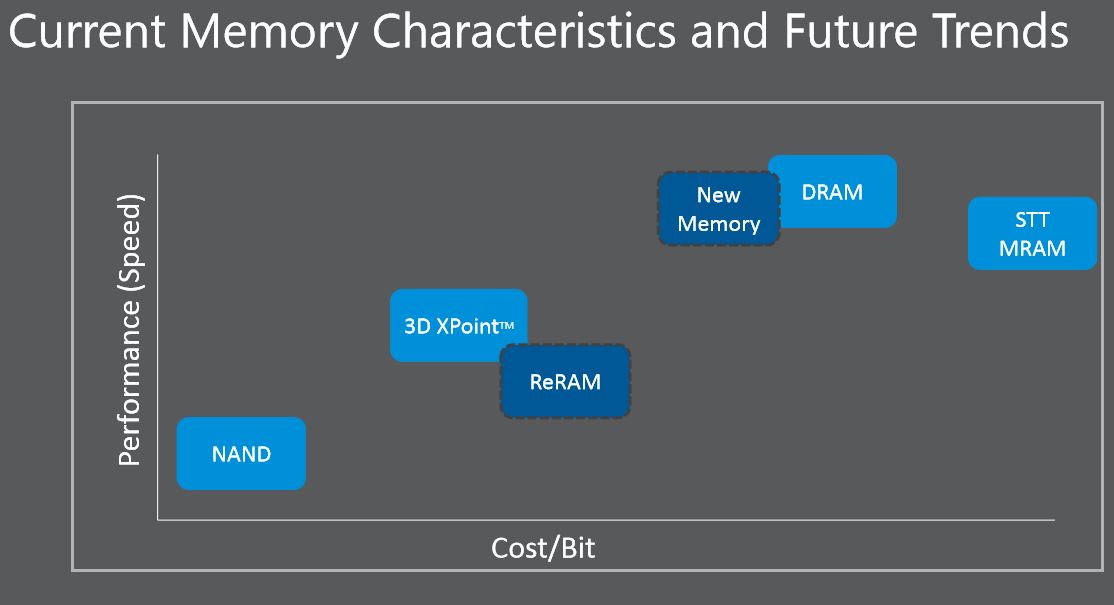

Micron was silent on the 3D Point front, though it revealed that it's making progress and is already developing the next two generations. Both new generations will be denser and faster than the first generation, which has yet to come to market. The leading 3D XPoint products will feature two "decks," and it’s logical to expect the next generations to employ more decks to increase density.

DRAM advances are coming slower and yielding fewer cost reductions with each new generation. As such, Micron feels that the slowing pace of innovation opens the door for a new type of memory to compete with DRAM, and as the company has previously revealed, it has a new high-performance memory under development. Micron hasn't revealed any of the particulars of its new memory, though it has been on the roadmap for quite some time. Intel and Micron are partnering up for 3D XPoint production, but it’s unclear if Intel is involved in Micron's new high-performance memory.

The Future Awaits

All told, Micron feels it is competitively positioned from a technology and operational standpoint, but it will continue to optimize its operations over the coming year. The company recently finished its Inotera acquisition and is in the process of eliminating redundant operations as it searches for a new CEO.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

AgentLozen The article makes Micron's future seem pretty optimistic for the next year.Reply

I'm really excited about the effect of GDDR6. Do you suppose it will be cheaper to implement than HBM2? Is GDDR6 the future of video card memory technology? Stay tuned for the next exciting episode of Dragon Ball Z! -

derekullo I vaguely remember that Doom video when I opened Toms on a friend's computer.Reply

Poor friend having to look at all those ads.

Not sure if it is my host file or noscript blocking it.

lol -

dstarr3 Reply19261701 said:I vaguely remember that Doom video when I opened Toms on a friend's computer.

Poor friend having to look at all those ads.

Not sure if it is my host file or noscript blocking it.

lol

Well, the video originated in the Carmack/Zenimax article, where it was supposed to be. So I don't think it's something that should be blocked that isn't. It's just, for some reason, on every single article now. -

bit_user ReplyMicron's 3D TLC NAND has an odd (but large) 384Gb die capacity

Why is this odd? TLC = triple-level cell, so the expected size should be a multiple of 3 (assuming # of cells is a power of 2). It would be 1.5 * the number of cells. -

bit_user What's meant by "throughput", on the Industry Supply Outlook slide? I somehow doubt it's related to production speed, since it's always negative and mentioned as meaning something other than wafer additions.Reply

BTW, there are some really interesting slides. It's a little surprising the would publish such analysis, but I guess maybe enough of their customers and investors demand to know such things. A few of them require a bit of a think to really understand what they're saying.

-

Lucky_SLS @PaulyAlcorn I think u meant "successor" in "Durcan will stay with the company until the board selects his predecessor." ;)Reply -

JohnMD1022 "Durcan will stay with the company until the board selects his predecessor."Reply

Successor.

His predecessor preceded him. -

aries1470 Yes, I was wondering the same thing, if there is a proof reader anymore :(Reply

"Durcan will stay with the company until the board selects his predecessor." Maybe he wanted to say selects the sucessor to his predecessor?