Thunderbolt 5 Could Reach 80 Gbps, Leaked Picture Shows

Thunderbolt 5 doubles existing speeds

On a recent trip to Intel's labs in Israel, Gregory M Bryant, the executive vice president & GM of Intel's Client Computing Group, took some photos and later shared them on Twitter. According to Anandtech, one of the tweets (which was later deleted) appears to show a poster on the office wall with information about the as-yet-unannounced Thunderbolt 5 protocol.

The poster says that Intel is targeted "80G PHY Technology," which implies that it is going for an 80 Gbps connection, which would be double the bandwidth of today's Thunderbolt 4 and USB 4 connections. This also falls in line with what Intel told us during The Tom's Hardware Show in March.

The poster also says "USB 80G is targeted to support the existing USB-C ecosystem," which strongly implies that Thunderbolt 5, like its predecessors, will use a USB-C connector. In March, Intel told us it was "pretty confident" this would be the case.

Article continues belowFirst released in 2011, Thunderbolt is Intel's high-speed connection standard. The standard is currently on Thunderbolt 4, though it was offering the same 40 Gbps of bandwidth and feature set in Thunderbolt 3. By doubling the bandwidth to 80 Gbps, Thunderbolt 5 could potentially offer higher refresh rates for 4K and 8K monitors, which it now supports at up to 120 and 60 Hz respectively.

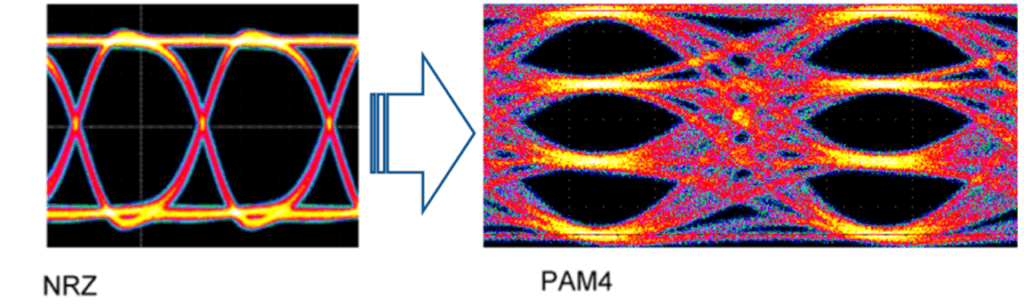

To achieve the higher bandwidth on Thunderbolt 5, it looks like the protocol will use PAM-3 modulation, which is an uncommon approach. So far, in protocols like USB, PCIe, etc., we have seen non-return-to-zero (NRZ) and PAM-4 (Pulse Amplitude Modulation) implementations. The NRZ signals are binary, meaning only 0s and 1s, while the PAM-4 signals are represented in two-bit formats, which are combinations of 0s and 1s (for example 01, 11, 11, 00). For a more detailed explanation, please check out this blog.

The novel PAM-3 uses -1, 0, and +1 states. This approach sits right between NRZ and PAM-4, but it allows the implementation of this signaling technique to be much simpler than PAM-4 while maintaining high bandwidth. With PAM-3, implementation is supposed to be easier and much more efficient, leading to Intel calling it a "novel PAM-3" approach.

The leaked slide also notes that "...N6 test-chip focusing on the new PHY technology is working in... showing promising results". While we can't see the full slide, it means that the Thunderbolt 5 PHY (physical layer) is already working in the fabs and it is producing desired results. As we know that N6 is TSMC's 6 nm manufacturing node, we can assume that Intel tapped TSMC's foundries to manufacture Thunderbolt 5 test chips.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

-

hotaru251 ReplyThunderbolt 5 could potentially offer higher refresh rates for 4K and 8K monitors, which it now supports at up to 120 and 60 Hz respectively.

4k...understandable if you have a huge monitor like an ultra wide.

8k? legit no reason to have 8k monitor when it wouldnt barely if even look any betetr than the 4k....especially when you could have a 4k at higher frame rate.

8k should only be on massive TV/projectors that actually benefit from that high fo a resolution. -

Dantte Replyhotaru251 said:4k...understandable if you have a huge monitor like an ultra wide.

8k? legit no reason to have 8k monitor when it wouldnt barely if even look any betetr than the 4k....especially when you could have a 4k at higher frame rate.

8k should only be on massive TV/projectors that actually benefit from that high fo a resolution.

Partially correct. High resolutions benefit in TWO scenarios; #1 you mentioned when you have an extremely large image; #2 is when you are extremely CLOSE to an image like your eye being 1" from the screen in a VR set! -

InvalidError PAM3 isn't exactly new: in computer networking, it has been used for the mostly forgotten 100Base-T1/T4 and 1GBase-T1.Reply

I wonder how much further they are going to push analog serial busses before going optical. Give it another decade and we'll probably see busses using QAM64 or possibly higher. -

In addition to what @Dantte already said, a higher resolution means less reliance on AA, and therefore a simplified rendering pipeline and less potential for side effects (like how Saints Row 3 supports AA for geometry, but not for transparent textures, which just looks ridiculous).Reply

Playing on a 27" 4K screen, I still notice aliasing in 4K. It's no longer as distracting as it used to be when I still played in 1080p, but it's still far from perfect. If I can buy a decent 27" 8K gaming screen, I will. I don't need other people telling me what I can or can't see, thank you very much. -

InvalidError Reply

It doesn't "simplify the pipeline" all that much since most anti-aliasing methods are just super-sampling and some degree of multi-sampling is already being used during normal texture mapping to keep rotated, scaled and transformed textures from getting mangled beyond recognition.Nolonar said:a higher resolution means less reliance on AA, and therefore a simplified rendering pipeline