AMD 3D V-Cache teardown shows the majority of the Ryzen 7 9800X3D is dummy silicon

Needs an electron microscope for further inspection.

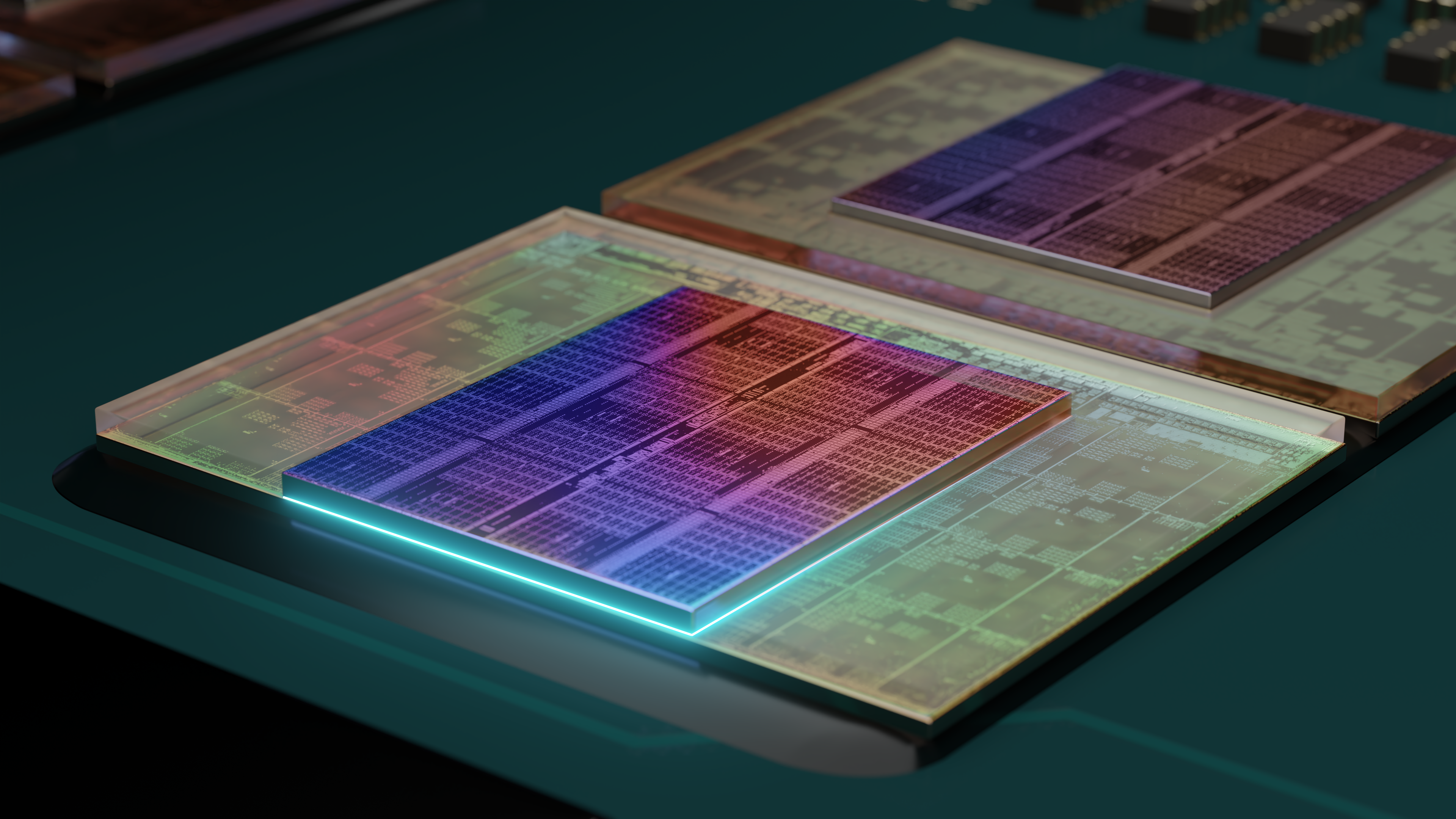

It's been over a month since AMD launched its Ryzen 7 9800X3D processor which quickly established itself as the fastest gaming CPU in the world. To investigate AMD's design philosophy, semiconductor analyst Tom Wassick (via Hardwareluxx) took apart the chip, and the findings of his first report suggest that a large part of the Ryzen 7 9800X3D is just dummy silicon for structural integrity. Still, AMD has extracted a lot of performance from its second-generation 3D V-Cache design, landing a solid victory against Intel's Arrow Lake chips.

Ryzen 9000 X3D processors are structured to slot the L3 SRAM cache chiplet below the heat-generating CCD (the compute die with the eight CPU cores). This allows for higher clock speeds by offering more thermal headroom, though AMD never exactly detailed the ins and outs of its stacking methodology. The report mentions that both the CCD and 3D V-Cache chiplets are thinned down to sub 10µm levels to expose the TSVs for hybrid bonding. Coupled with BEOL (Back-end of Line) - the section with the necessary metal layers for connectivity - the total SRAM and CCD package comes in at 40-45µm thick.

The SRAM die has always been a fraction of the size of the compute die; Ryzen 7000 3D V-Cache chiplets measured 36mm-squared in contrast to the 66.3mm-squared CCD. Tom Wassick's findings state that the SRAM die is actually 50µm larger than the CCD on all four sides. Realistically speaking, a large portion of this die should be empty, but we still await more details.

Excluding interconnects, the SRAM and CCD should add up to less than 20µm thick. To accommodate such small and fragile components, AMD has added a bulky layer of dummy silicon at the top and the bottom for structural integrity. The thickness of the entire package is roughly in the ballpark of 800µm. Subtracting the 50µm die stack (CCD, SRAM, and BEOL) lands us at 750µm of structural support at the top. In other words, 93% of the total stack comprises just dummy Silicon to keep the dies intact.

The different layers are connected through a coating of oxide between them. It is reported that this binding layer is thinner between the core CCD and SRAM than between the dummy silicon and the two dies, to allow for better thermal performance.

There remain several unanswered questions and Tom Wassick plans to address them with the help of a Scanning Electron Microscope in a future follow-up. Despite losing its gaming throne to AMD, Intel has no plans to counter AMD's 3D V-Cache technology, at least for the mainstream segment. Nonetheless, we expect AMD to announce the 12-core and 16-core Ryzen 9 9900X3D and the Ryzen 9 9950X3D at CES next month.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Hassam Nasir is a die-hard hardware enthusiast with years of experience as a tech editor and writer, focusing on detailed CPU comparisons and general hardware news. When he’s not working, you’ll find him bending tubes for his ever-evolving custom water-loop gaming rig or benchmarking the latest CPUs and GPUs just for fun.

-

chaz_music Don't forget that the added silicon also helps add thermal mass to the entire chip system, giving better transient thermal behavior. That thermal mass slows down the thermal time constant and give the power control system more time to react within the system during heavy loading. So it isn't all wasted silicon just for mechanical reasons.Reply -

gjonezin Reply

This makes sense. My first thought was, "you mean they have room to add MORE Vcache?!"chaz_music said:Don't forget that the added silicon also helps add thermal mass to the entire chip system, giving better transient thermal behavior. That thermal mass slows down the thermal time constant and give the power control system more time to react within the system during heavy loading. So it isn't all wasted silicon just for mechanical reasons. -

HardwiredWireless Reply

You say 'don't forget' as if you are retelling what was proven in the analysis, but that was never shown. It's interesting but there's no evidence that is happening or could happen with the layout being what it is.chaz_music said:Don't forget that the added silicon also helps add thermal mass to the entire chip system, giving better transient thermal behavior. That thermal mass slows down the thermal time constant and give the power control system more time to react within the system during heavy loading. So it isn't all wasted silicon just for mechanical reasons. -

edzieba Reply

The cache die is on the opposite side of the compute die from the HSF. Any heat the cache die absorbs can only leave by heating up the compute die again.chaz_music said:Don't forget that the added silicon also helps add thermal mass to the entire chip system, giving better transient thermal behavior. That thermal mass slows down the thermal time constant and give the power control system more time to react within the system during heavy loading. So it isn't all wasted silicon just for mechanical reasons. -

Phyzzi It would be pretty incredible if we got to the point of adding diamond instead of non-computing silicon to these chips for structure and thermal sink. I assume that some of the chip is being built by vapor deposition anyway, and doing it with or on diamond could certainly improve performance.Reply -

mwestall Reply

For heavens sake guys:-Admin said:An in-depth analysis of the Ryzen 7 9800X3D suggests that a large portion of the chip is comprised of structural silicon.

AMD 3D V-Cache teardown suggests the majority of the Ryzen 7 9800X3D is occupied by dummy silicon : Read more

"Ryzen 7000 3D V-Cache chiplets measured 36mm-squared"

No no no no no no no.

It's 36 **square mm** 36mm squared is 1296 sq mm. -

NinoPino Reply

Right, but it could help to transfer heat from the die hotspots, to the near area, distributing the heat homogeneously on all the die.edzieba said:The cache die is on the opposite side of the compute die from the HSF. Any heat the cache die absorbs can only leave by heating up the compute die again. -

bit_user Reply

Why are you so sure it's all just for structural support? Maybe the reason it's that thick is to reduce the gap between the compute die and heat spreader?The article said:The thickness of the entire package is roughly in the ballpark of 800µm. Subtracting the 50µm die stack (CCD, SRAM, and BEOL) lands us at 750µm of structural support at the top. In other words, 93% of the total stack comprises just dummy Silicon to keep the dies intact. -

bit_user Reply

That's silly. CPUs do indeed transfer a non-trivial amount of heat through their pins, into the motherboard. Even though the bulk of it normally goes through the IHS, try pointing an IR thermometer at the backside of your motherboard, under the CPU socket. Heat definitely manages to transfer through the socket, into the motherboard.edzieba said:The cache die is on the opposite side of the compute die from the HSF. Any heat the cache die absorbs can only leave by heating up the compute die again.

What @chaz_music said seems plausible to me. To go further down this path, we'd need data on the thermal mass of that base layer and the thermal conductivity of the SRAM die. Since the SRAM die is so thin, I doubt it's providing much thermal resistance.