PCI-SIG Talks PCIe 4.0 at Its Developers Conference

During the PCI-SIG Developers Conference, PCI-SIG discussed PCIe 3.0, PCIe 4.0 technology, new form factors and more...

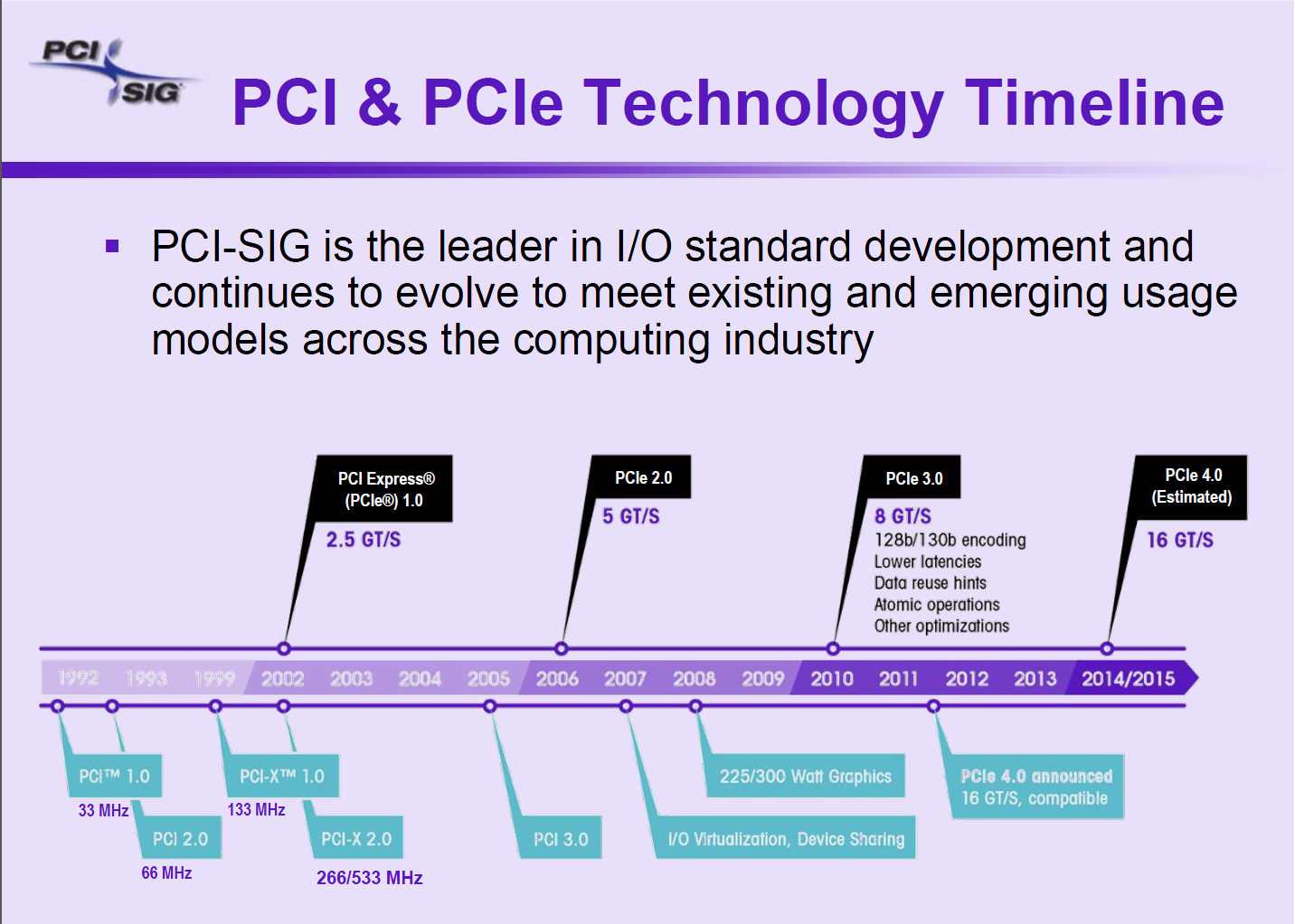

Featured speakers at this week's PCI-SIG developer conference included Al Yanes, President and Chairman, and Ramin Neshati, Serial Communications Workgroup Chair. Discussion included talk of PCI Express (PCIe) and new updates to meet the evolving demands of a variety of computing markets from high-performance storage to ultra-thin and light mobile devices. Increased performance and new form factors frame the organization's focus as it delivers new technologies built upon the 20-year legacy of the Peripheral Component Interface (PCI).

This year marks 10 years of PCIe press specification development and PCI-SIG is now turning its focus to driving I/O technology forward through advancements in PCIe-attached storage, new form factors and performance enhancements for the PCIe specification.

In June of 2011, we learned for the first time about the upcoming PCIe 4.0, even before PCIe 3.0 hit the market. PCIe 4.0 technology is being developed to deliver 16GT/s, doubling the bandwidth over the PCIe 3.0 specification with seamless backward compatibility to all previous versions of PCIe technology. The PCIe 4.0 architecture is designed to double the data rate, while maintaining its position as a low-cost, high performance I/O technology. With the increase in clock rate designers can implement narrower links, thereby saving cost through pin reduction. The final PCIe 4.0 specifications, including form factor specification updates, are expected to be available in late 2015.

Article continues belowIn late 2011, we saw the first wide spread implementation of the PCIe 3.0 standard in the market. With implementation of PCIe 3.0, PCIe-attached storage can achieve significantly higher bandwidth using processor-integrated PCIe 3.0 technology that is directly attached to storage sub-systems. As we discussed in 2010, PCIe 3.0 offers double the bandwidth over previous generation PCIe 2.0.

"PCI Express 2.0 uses an 8b/10b encoding scheme, where 8 bits of data are mapped to 10-bit symbols to achieve DC balance. The result is 20% overhead, cutting effective bit rate. PCI Express 3.0 moves to a much more efficient 128b/130b encoding scheme, eliminating the 20% overhead. So, the 8 GT/s won’t be a “theoretical” speed; it will be the actual bit rate, comparable in performance to 10 GT/s signaling with 8b/10b."

The PCIe 3.0 standard is optimized for high performance solid-state drives (SSDs) in enterprise and client applications, and is well-positioned to address growing demands for increased storage I/O speeds.

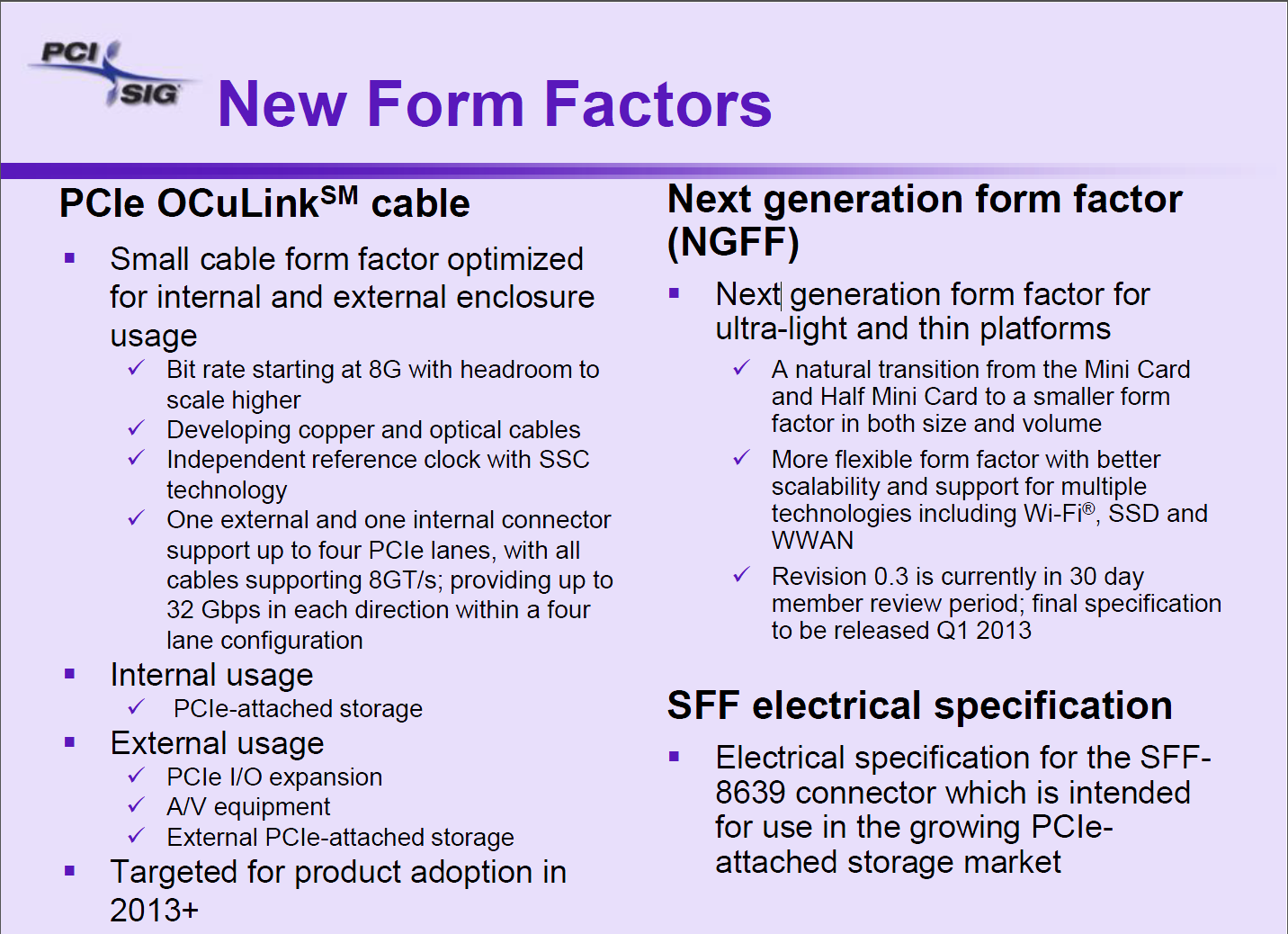

PCI-SIG also provided some insight on new form factors, which include the PCIe OCuLink, NGFF and SFF electrial specifications.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

- PCIe OCuLink, a small cable form factor supporting optical and copper optimized for internal and external enclosure usage, is being designed to offer bit rates starting at 8Gbps, with headroom to scale, and new independent cable clock integration. The internal and external connector supports up to four PCIe lanes, with all cables supporting 8GT/s. This provides up to 32Gbps in each direction within a four lane configuration; one lane and two lane configurations are also supported.

- Next generation form factor that will be part of the Mini CEM specification is being designed for the emerging ultra-light and thin platforms. A natural transition from the existing Mini CEM specification, this form factor is more flexible, smaller in both size and volume, offers better scalability and supports multiple technologies including Wi-Fi®, SSD and wireless wide area network (WWAN).

- The development of an electrical specification for the SFF-8639 connector which is intended for use in the growing PCIe-attached storage market.

"Each new technical innovation is a testament to the importance of PCI-SIG, providing our membership and the computing industry with future-focused technology, ensuring that increased performance is among one of our top priorities," said Al Yanes, PCI-SIG president and chairman. "We plan to celebrate 20 years of innovation by continuing to seek new ways to deliver PCIe technology across a variety of computing platforms."

"The PCI-SIG has amassed a long-term record of technical innovation tempered by real-world requirements for backward compatibility," said Bob Wheeler, senior analyst at The Linley Group. "PCIe 4.0 is poised to continue this market-savvy approach while keeping the technology on the leading edge of economical interconnects."

-

Pinhedd loopsI just need to find a GPU that will fill the lanes.Reply

Graphics cards may be the most popular PCIe add-in cards but many onboard devices also communicate with the chipset or CPU by PCIe. Onboard peripherals that are added by the motherboard manufacturer such as audio, ethernet, USB 3.0, extra SATA ports, bluetooth, wifi, etc... are often wired up using PCIe links. Newer PCIe generations will allow these devices to provide greater services without increasing the complexity of the motherboard. -

the3dsgeek i don't know where are they going with this, today's graphic cards performs the same in the old generation PCIe slots, or i don't know, maybe 2-3% difference. First make the hardware that can take advantage of the available bandwidth. Its like putting a car on a 200mph race track when it can only do 100.Reply -

rocknrollz Its like putting a car on a 200mph race track when it can only do 100.Reply

Exactly, but what happens when we get the tech to go up to the track? Then we gotta rebuild it all. Better to have it available now, then later.

-

A Bad Day For those who say that there's no need for so much bandwidth...Reply

PCI-E 1.0 had lots of bandwidth during its introduction, but now GPUs saturate it fairly well.

AGP had lots of bandwidth during its introduction, until it reached a point where OCing it actually improved GPU performance.

PCI original had lots of bandwidth during its introduction. However, the last GPU that used it today was a modified GTX 520.

USB 2.0 had lots of bandwidth during its introduction. But today, SSDs require a lot more than two USB 2.0 ports to avoid being bottlenecked.

-

opmopadop I know 'GigaTransfers' is the correct description for PCIe transfer speed, but I miss the old tried-and-true Gigabits-per-second measurement.Reply

http://en.wikipedia.org/wiki/Transfer_(computing) -

do renember this tech would not hit the market until 2016-2017. just look at 4 years ago, saturating a pcie-gen2 seemed impossible. looking foward, high end gpus might start reaching the upper limits of pci-e gen3, (sli and crossfire also present their own issues, as often getting two x16 slots is tough) besides, more lanes will affect other areas, more bandwidth for SATA, usb3 (which someday every port will be native 3.0) thunderbolt.Reply

-

DRosencraft I understand where the3dsgeek is coming from. The problem with building stuff like this so far out into the future sometimes is that it takes what can seem like an eternity for the useful hardware to catch up. Enterprise will love this because they do virtually everything through PCI and can never get it done fast enough. But most people here are consumers, and the consumer sector has limited use for PCIe 3.0 at this point, such that even talking about 4.0 seems at least a little early, if not ridiculous. I mean, if you're an AMD fan, they don't even have a MB with 3.0 on it yet. And the benefit of 3.0 for the latest gen. of GPUs is not that terrific. As for consumer SSDs on PCIe, most don't take full advantage of 2.0, let alone touch 3.0, and are so wildly expensive that few people seem to give a care for them at all.Reply

It is nice to have these sorts of upgrades planned out, but increasingly we are seeing that they come out farther and farther in advance of any actually useful means of implementation. So, if you're a consumer now, you end up buying hoping that a use will come along now, or you end up paying a premium, even if only slightly, for the sake of having a newer/higher standard that no one will have any meaningful use for. But, 2015 is 3 years away, and the first implementations probably wont be until 2016, so maybe things will change faster than they have been of late.