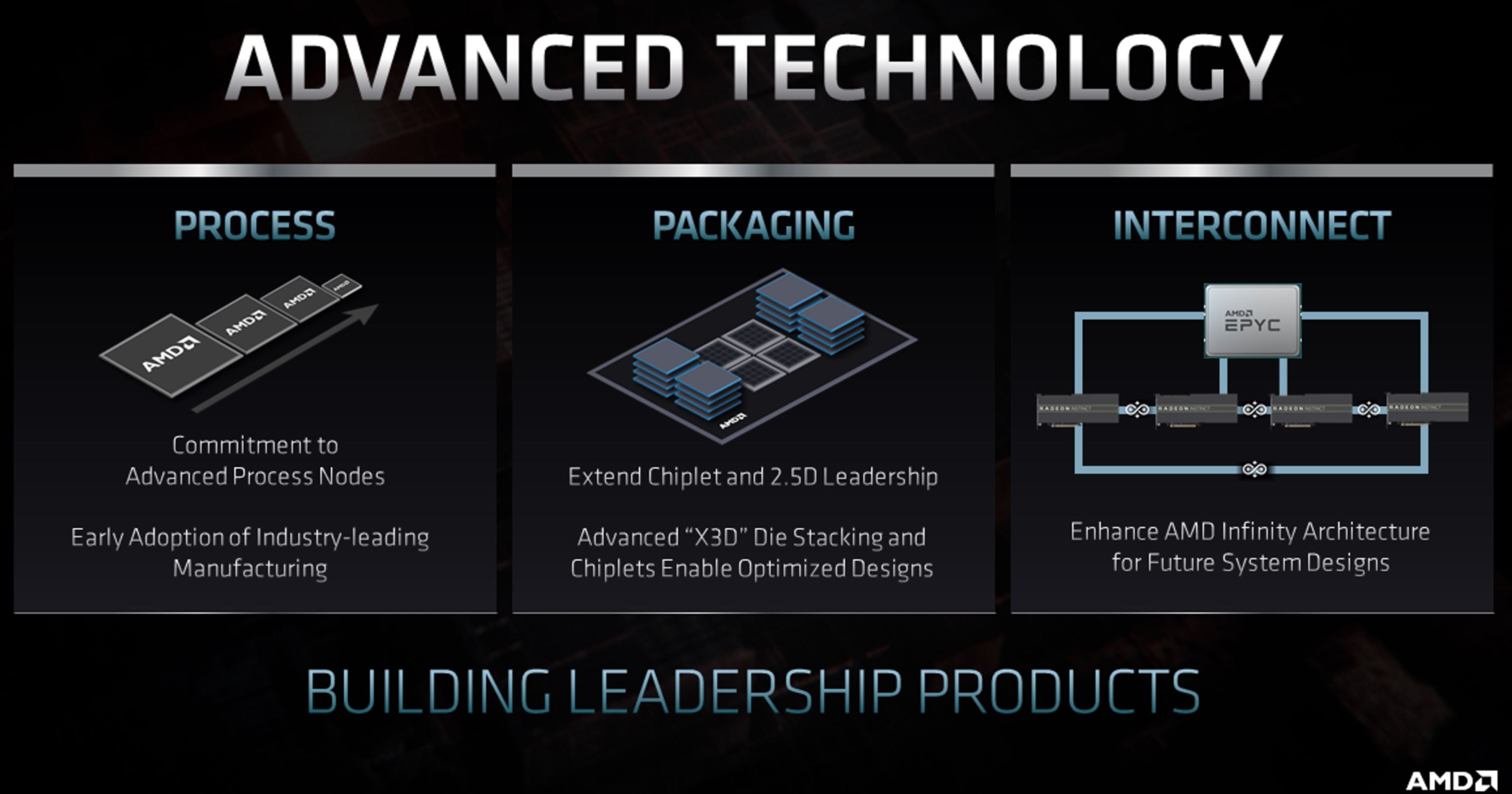

AMD Announces X3D Chip Stacking and Infinity Architecture

AMD takes chip design into the third dimension

AMD's innovative chiplet-based Zen microarchitecture allows the company to tie together several die into single multi-chip modules (MCM) like the Ryzen and EPYC processors, but the company isn't stopping there: Today at its Financial Analyst Day 2020 the company unveiled its new X3D chip packaging technology that will bring its MCMs into the third dimension and provide up to an 10X improvement in bandwidth density.

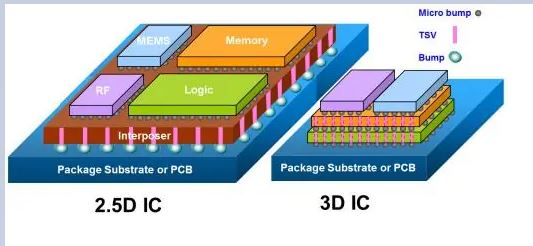

The new technology is a combination of 2.5D packaging, which involves placing multiple chips on a single interposer and tying them together with through-silicon vias (TSV), and 3D stacking, which uses multiple dies stacked atop one another that are then mounted to an interposer (as seen below) with TSV connections extending throughout

AMD hasn't provided details of which elements, be they memory or compute die (logic), it will incorporate into the X3D stacking designs, instead telling us that it will unveil the more technical aspects of its new packaging technique at a more tech-centric event in the future. From AMD's images, it appears that the stacked elements may be comprised of memory elements, perhaps HBM packages, making it hard to determine the exact nature of the new technology.

The key takeaway is that it appears those stacks of HBM will be incorporated onto the same package as CPU cores, which could be a breakthrough advance, particularly in the data center. This could radically boost throughput to the execution cores, in effect creating another tier of memory for bandwidth-sensitive workloads.

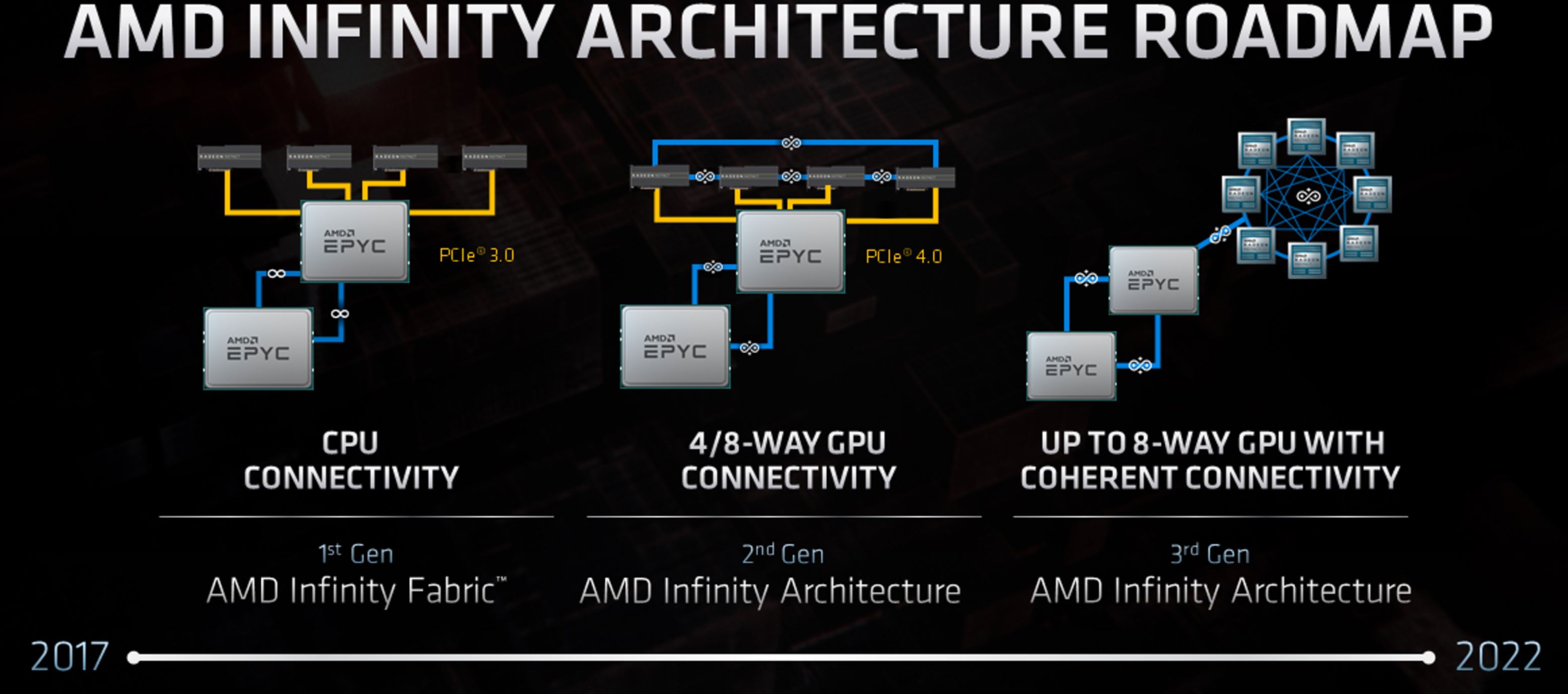

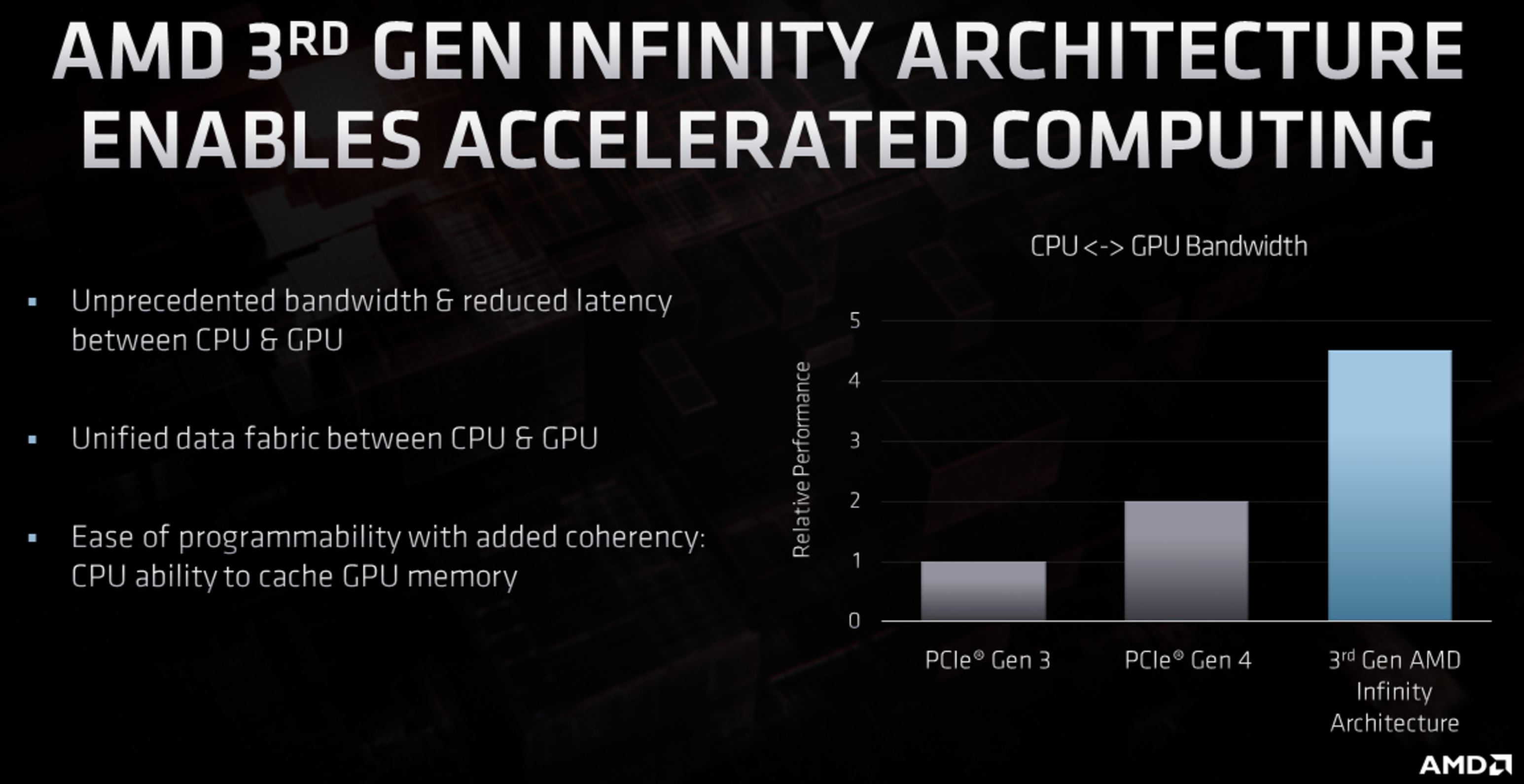

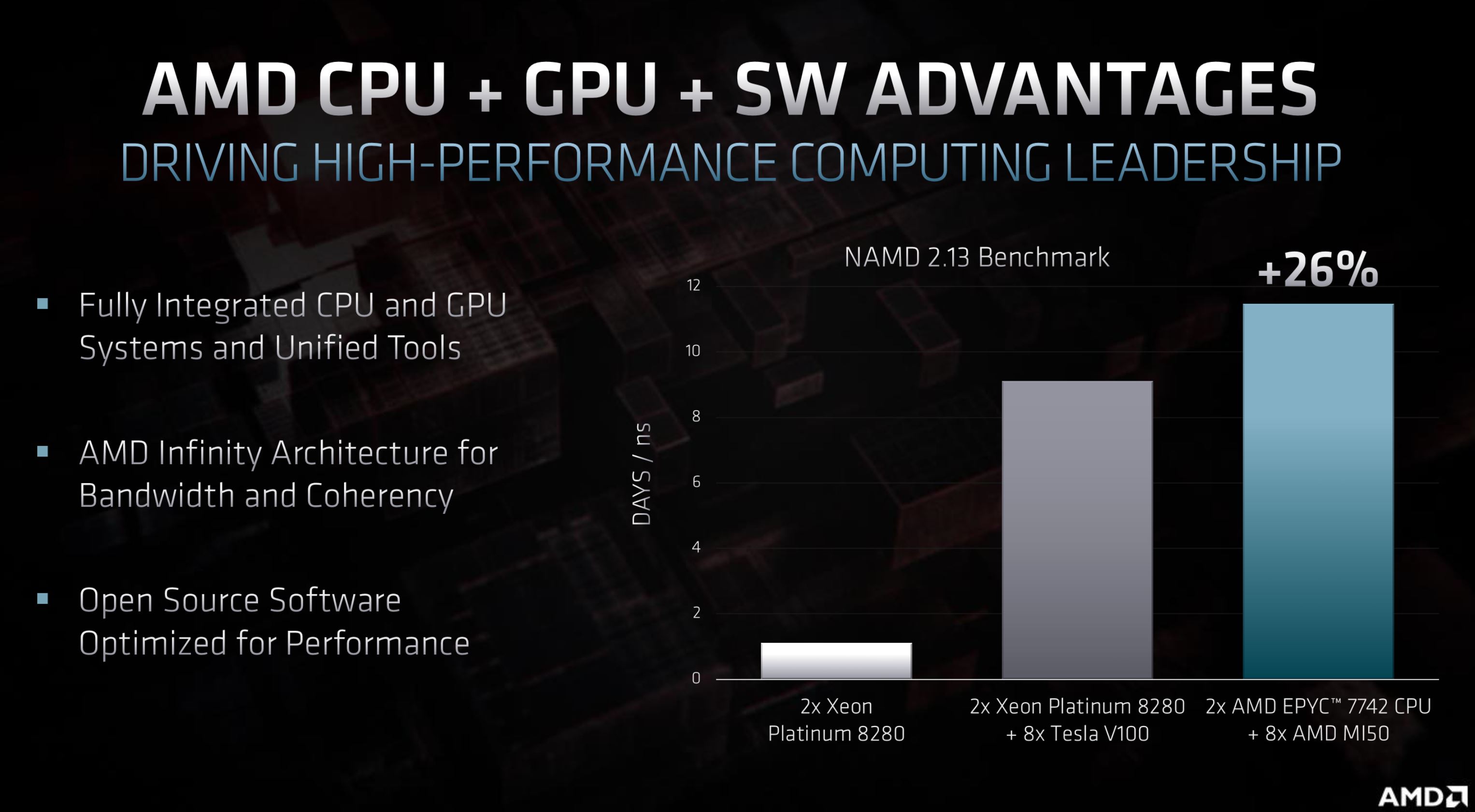

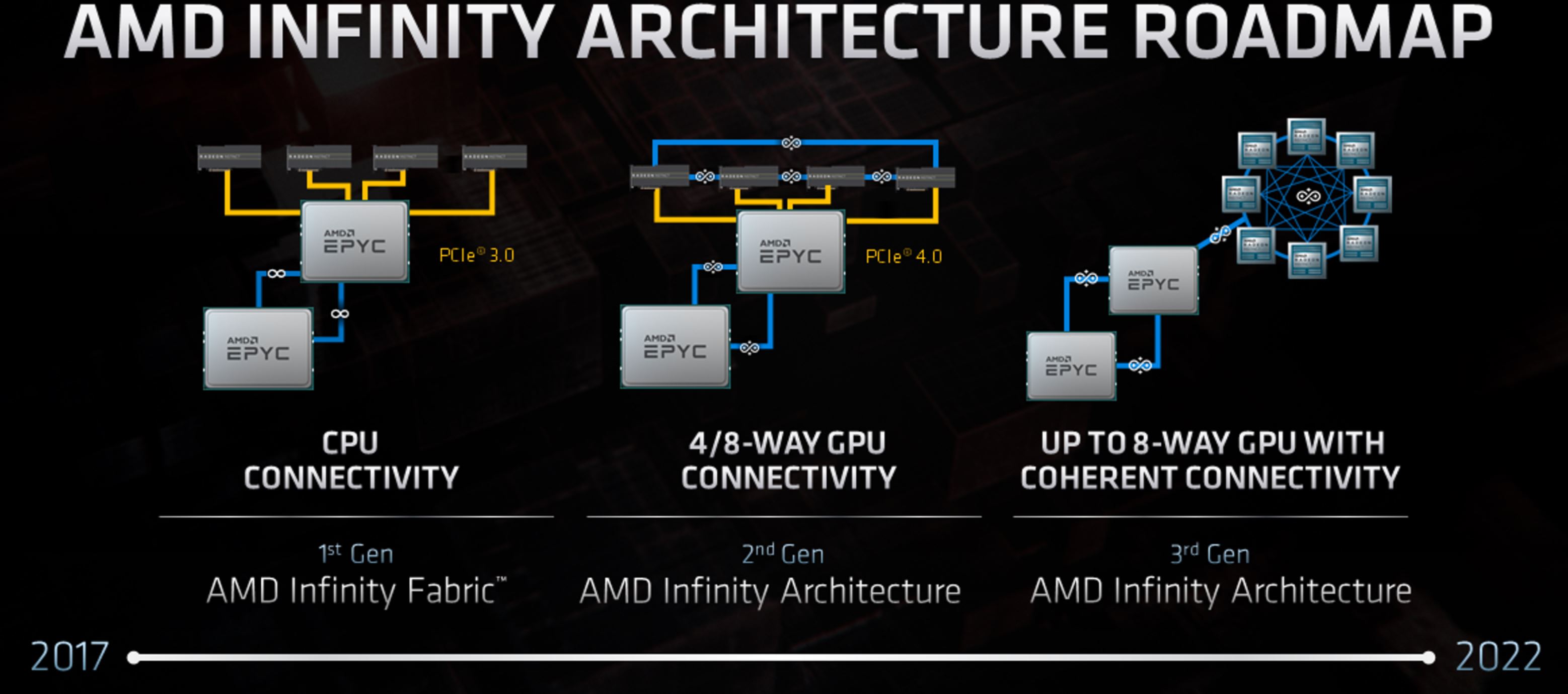

The company also unveiled a new Infinity Architecture, which is a system-level approach to tying together AMD's CPUs and GPUs. We covered this Infinity Fabric 3.0-driven approach in this recent article. In short, it enables cache coherency between AMD's CPUs and GPUs, which reduces data movement to improve performance, reduce latency, and boost performance per watt. It also eases programming requirements. The illustrations include eight GPUs tied into a mesh/taurus-type topology that's connected to the CPUs.

AMD also touted the recent advancements to its open ROCm software suite that it layers on top of the hardware.

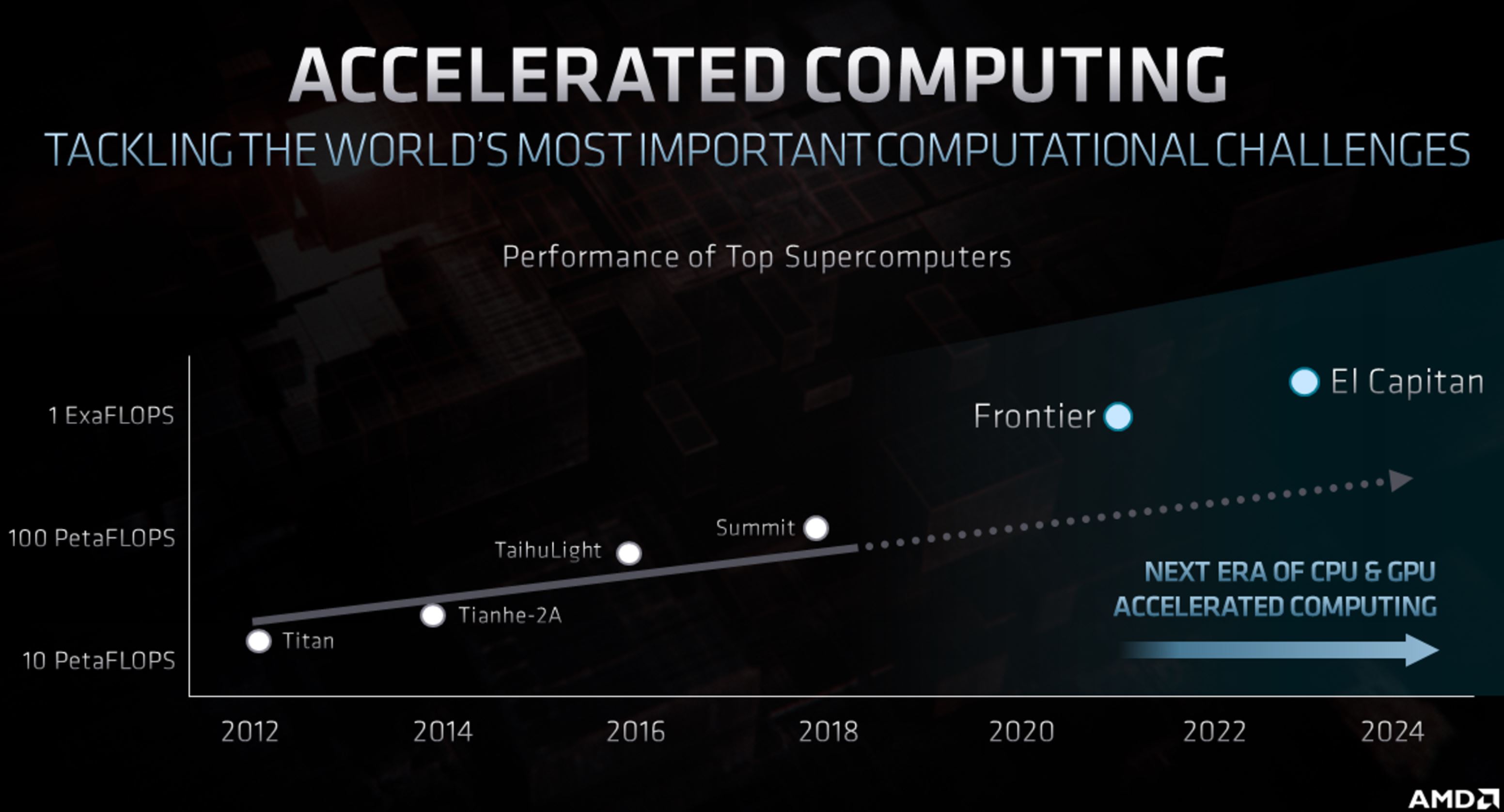

Intel takes a similar approach with its Ponte Vecchio GPUs, but Nvidia doesn't produce CPUs, so it can't match this level of integration. The DOE recently suggested that the Infinity Fabric 3.0 architecture was a key factor in its decision to award AMD two contracts for exascale-class supercomputers, including Frontier and El Capitan, while Intel has taken one exascale supercomputer design win with its coherent Ponte Vecchio architecture. Nvidia has yet to win an exascale contract.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

In either case, X3D stacking is an obvious answer to Intel's Foveros die stacking. We'll update as we learn more.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.