First Details About Samsung's 1.4nm Process Emerge

On track for 2027

Samsung said that its upcoming SF1.4 (1.4nm-class) process technology will increase the number of nanosheets from three to four, Jeong Gi-Tae, vice president of Samsung Foundry, told The Elec, reports DigiTimes. The move promises to bring significant benefits for performance and power consumption.

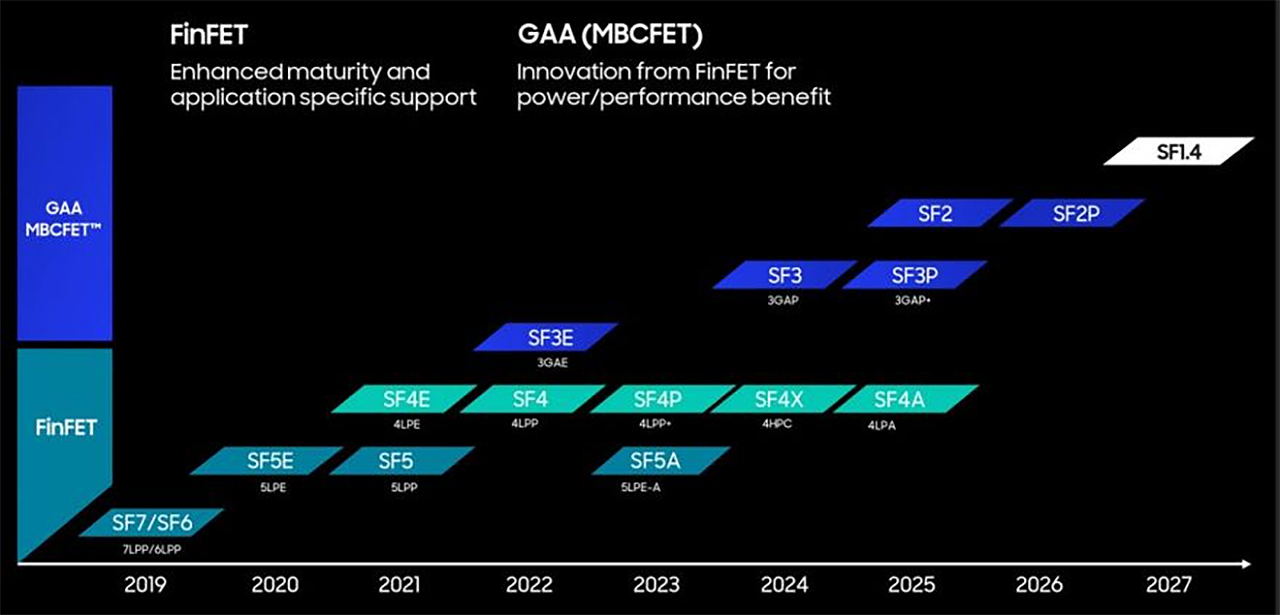

Samsung was the first company to introduce a process technology that relies on gate-all-around (GAA) nanosheet transistors with its SF3E (also known as 3nm-class gate-all-around ear, 3GAE) in mid-2022. The company uses the technology to make various chips, but it is believed that usage of the node is limited to tiny chips, such as those used for cryptocurrency mining. Next year Samsung plans to introduce its SF3 technology, which is poised to be used by a wider range of applications. In 2025, Samsung plans to roll out its performance-enhanced SF3P technology that is designed with data center CPUs and GPUs in mind.

Also in 2025, Samsung expects to introduce its SF2 (2nm-class) fabrication process, which will not only rely on GAA transistors, but will also feature backside power delivery, which brings substantial benefits when it comes to transistor density and power delivery,

Perhaps the biggest overhaul of Samsung production nodes after the introduction of GAA-based SF3E will happen in 2027, when Samsung's SF1.4 technology will gain an additional nanosheet by increasing the number of nanosheets from three to four.

Increasing the number of nanosheets per transistor can enhance the driving current, improving performance. More nanosheets allow for more current to flow through the transistor, enhancing its switching capabilities and operational speed. Also, more nanosheets can lead to better control of the current flow, which can help in reducing leakage current, thus reducing power consumption. Furthermore, improved control over current flow also means that the transistors generate less heat, which increases power efficiency.

Both Intel and TSMC intend to start using GAA transistors with their 20A and N2 (2nm-class) process technologies due in 2024 and 2025, respectively. By the time these companies introduce their nanosheet-based nodes, Samsung will have significant experience with gate-all-around transistors, which might be beneficial for the foundry.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

pug_s Samsung is lagging behind TSMC in terms of chip performance. In fact, Samsung decided not to release an Exynos chip in its flagship S23 phone. Despite that, I'm surprised that Google decided to stick with Samsung's Fab for its tensor chip.Reply -

NinoPino Reply

This is becoming a refrain on technical journalism and forums but from what is written in the article Samsung have years of advantage with GAA and have performance problems only with large chips.pug_s said:Samsung is lagging behind TSMC in terms of chip performance.

The situation of Samsung is not so bad as often described.