India's First CPUs Are Ready for App Development

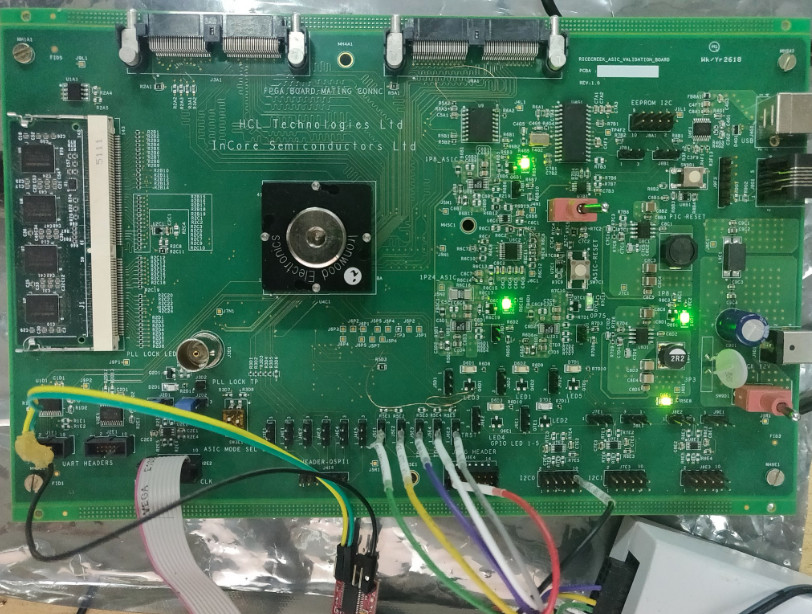

The Indian Institute of Technology (IIT) Madras has released the software development kit (SDK) for its open-source Shakti processor. Shakti is based on the open-source RISC-V instruction set architecture and was funded by the Indian Ministry of Electronics and Information Technology. The institute promised that a development board will also be released soon.

The RISE group at IIT Madras started working on the Shakti project in 2016 with a plan to release a family of six classes of processors, each serving a different market. The group promised that the reference processors will be competitive with commercial offerings in terms of area, performance and power consumption.

Now India, like China and the European Union, are showing interest in designing their own processors, rather than relying on ones designed by U.S. manufacturers.

With the release of the Shakti SDK, developers can begin to develop applications for the Shakti processors, even before they're commercialized.

E Class

The E class is a 3-stage in-order processor targeted at embedded devices such as Internet of Things (IoT) devices, robotic platforms, motor controls, et cetera.

C Class

This is a 32-bit 5 stage in-order microcontroller-class of processors supporting 0.2-1 GHz clock speeds. It's aimed at mid-range application workloads and has a very low power profile, plus support for optional memory protection.

I Class

The I class 64-bit out-of-order processors support 1.5-2.5 GHz clock speeds and support for multi-threading. It targets mobile, storage and networking applications.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

M Class

The M stands for multi-core here, as the M class processors support up to eight CPU cores, which can also be I and C class cores.

S Class

The S class of Shakti processors is aimed at workstation and server-type workloads. It’s an enhanced version of the I class processor that features multi-threading support.

H Class

These are processors for the high-performance computing and analytics workloads. Their primary features include a high single-thread performance, optional L4 cache, as well as support for Gen-Z fabric and storage-class memory.

Experimental Designs

The RISE group is also working on two new experimental classes of processors. The first is the T class, which should support object-level security and coarse grain tags for micro-VM-like functionality to mitigate software attacks like buffer-overflow.

The second is the F class, which can be thought of as an upgrade over the T class with additional support for redundant compute blocks and bus fabrics, ECC memory and functionality to detect permanent faults.

Lucian Armasu is a Contributing Writer for Tom's Hardware US. He covers software news and the issues surrounding privacy and security.

-

bit_user Hmmm... not as interesting as those VISC cores, we read about a few years back.Reply

Anyway, good luck to them. They'll hardly have the RISC V market to themselves. It'd be interesting to know what manufacturing node they're using. I think they'll have to compete on price, because I imagine it'll take a few generations before they can close the power/performance gap with ARM.

The second is the F class, which can be thought of as an upgrade over the T class with additional support for redundant compute blocks and bus fabrics, ECC memory and functionality to detect permanent faults.

...maybe for India's burgeoning space industry?

BTW, I have a suspicion the letters might stand for some Hindi words or names. If so, going with just the letters was probably a good call. -

prtskg Reply

I doubt it's for space industry. ISRO designs and manufactures its own chips, AFAIK. DRDO now has that capability too. But of course both, along with local industry will benefit from it.bit_user said:...maybe for India's burgeoning space industry?

I think the main reason is be to be free from foreign interference. There has been history of US banning crucial technologies to India. In recent decade, the relationship between these two big democracies have been good except for trade tensions in recent times and India's relationship with Iran and Russia. Also there's a sense that if Trump manages to get upper hold in trade relations to China, its next step would be India. So there is more emergency in them with regards to technology. -

bit_user Reply

So, what do you think is the application for the F class? The comment you quoted was specific about that.prtskg said:I doubt it's for space industry. ISRO designs and manufactures its own chips, AFAIK. DRDO now has that capability too.