AMD teases its first 2nm chip, EPYC 'Venice' fabbed on TSMC N2 node — also announces USA production of current-gen chips

First 2nm HPC design.

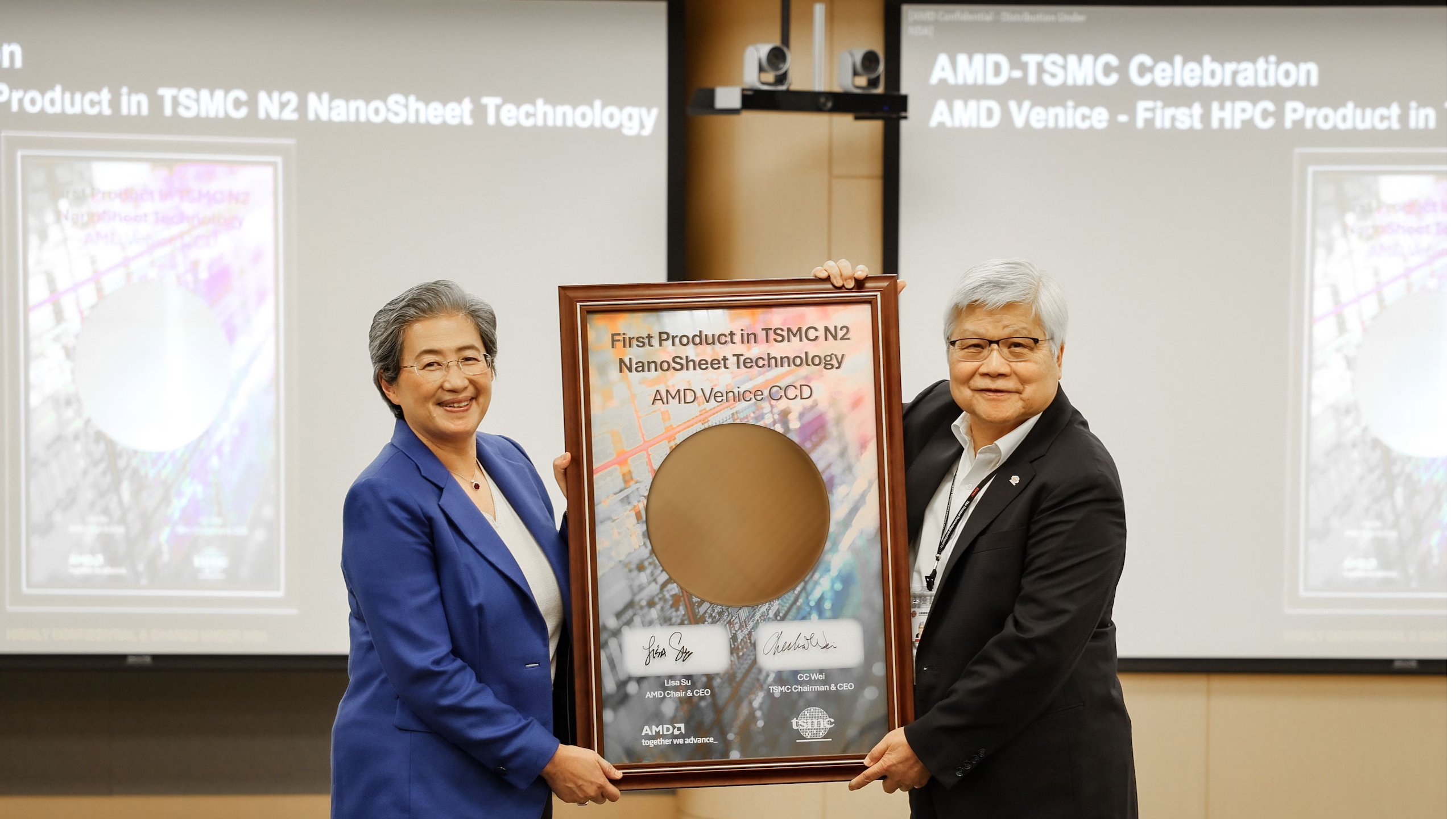

In a rather unexpected turn of events, AMD announced late on Monday that it had obtained its first 2nm-class silicon, a core complex die (CCD) for its 6th Generation EPYC 'Venice' processor, which is expected to launch next year. The Venice CCD is the industry's first HPC CPU design to be taped out on TSMC's N2 process technology, highlighting AMD's aggressive roadmap and the readiness of TSMC's production node.

AMD's 6th Generation EPYC 'Venice' is expected to be based on the company's Zen 6 microarchitecture and is expected to be launched sometime in 2026. The CPU will rely on CCDs to be made on TSMC's N2 (2nm-class) fabrication process, so it is about time for the company to get the first Venice CCDs out of the fab. Yet, the fact that AMD already has chips it can talk about highlights the long-standing collaboration between AMD and TSMC as well as the culmination of joint efforts to build chips on one the most advanced process technologies that TSMC has ever developed to date.

For now, AMD isn't discussing the details of its EPYC 'Venice' processors or CCDs, though the company's press release claims that the silicon had been taped out and brought up, which means that the CCD has successfully powered on and has passed basic functional testing and validation.

"TSMC has been a key partner for many years, and our deep collaboration with their R&D and manufacturing teams has enabled AMD to consistently deliver leadership products that push the limits of high-performance computing," said Dr. Lisa Su, chief executive of AMD. "Being a lead HPC customer for TSMC's N2 process and for TSMC Arizona Fab 21 are great examples of how we are working closely together to drive innovation and deliver the advanced technologies that will power the future of computing."

TSMC's N2 is the foundry's first process technology that relies on gate-all-around (GAA) nanosheet transistors. The company expects its manufacturing technology to offer either a 24% to 35% reduction in power consumption or a 15% increase in performance at constant voltage, along with a 1.15X boost in transistor density compared to the previous N3 (3nm-class) generation. These gains are primarily driven by the new type of transistors and the N2 NanoFlex design-technology co-optimization framework.

AMD's announcement comes after its arch-rival Intel delayed the release of its next-generation Xeon 'Clearwater Forest' processor made on its 18A manufacturing technology (which is set to rival TSMC's N2) to the first half of next year.

Separately, AMD announced that it has successfully validated the silicon of its 5th Generation EPYC processor produced by TSMC at its Fab 21 facility near Phoenix, Arizona. As a result, some of the company's current-generation EPYC CPUs can now be produced in the U.S.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

"We are proud to have AMD be a lead HPC customer for our advanced 2nm (N2) process technology and TSMC Arizona fab," said Dr. C.C. Wei, chief executive and chairman of TSMC. "By working together, we are driving significant technology scaling resulting in better performance, power efficiency and yields for high-performance silicon. We look forward to continuing to work closely with AMD to enable the next era of computing."

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Pemalite Be interesting to see what kind of impacts Tariffs does to AMD's next-gen chips in regards to pricing.Reply

They have been fairly consistent gen-on-gen thus far. -

thestryker I wonder if the Epyc CPUs on N2 will be all of them or just the high density ones like the current N4/N3 split. This is also our first official confirmation that Apple didn't buy out the first run of N2.Reply -

hannibal Reply

Consumer and pro stuff are different thing totally.jackt said:And they are stilll selling 4nm... -

Neilbob The whole 2nm thing aside, I find it interesting that they're pulling out the 'Venice' code name again after 20 or so years.Reply

It was used for the 90nm Athlon 64 that, at the time, turned out to be vastly superior to the truly awful Intel Prescott Pentium 4 space-heaters. -

bit_user Reply

TSMC's 2 nm doesn't hit volume production until the end of this year.jackt said:And they are stilll selling 4nm...

https://www.tomshardware.com/tech-industry/tsmcs-1-6nm-node-to-be-production-ready-in-late-2026-roadmap-remains-on-track

Yeah, it's a little disappointing Zen 5 used a N4 node, but there are a few benefits:

TMSC has N4 production currently in its Arizona fabs and AMD is a customer. This is good for US sales of these chips and resilient supply if Taiwan gets cut off.

N4 is cheaper, giving AMD more flexibility with pricing.

Considering how competitive Zen 5 has been on N4, that bodes quite well for further reductions.

Honestly, the biggest complaint I have about Zen 5 isn't the CCDs, but rather the N6 IO die that they reused from Zen 4. Because of that, it has higher idle power and worse memory performance. I sort of wish they'd do a refresh with a newer IO die and then I might even be tempted to take the plunge. -

bit_user Reply

All of the AMD Epyc CPUs have been named after cities in Italy.Neilbob said:The whole 2nm thing aside, I find it interesting that they're pulling out the 'Venice' code name again after 20 or so years.

Zen 1 = Naples

Zen 2 = Rome

Zen 3 = Milan

Zen 4 = Genoa; Zen 4C = Siena

Zen 5 = Turin

You can see here that their naming convention was much looser, just picking an assortment of big cities from all over the place:Neilbob said:It was used for the 90nm Athlon 64 that, at the time, turned out to be vastly superior to the truly awful Intel Prescott Pentium 4 space-heaters.

https://en.wikipedia.org/wiki/List_of_AMD_processors#K8_core_architecture_(2003%E2%80%932014)

I think it's okay for them to reuse Venice, by now. Nobody is going to be confused by this. -

ottonis With an expected launch date "somwhere in 2026" , these N2-based chips from AMD will probably hit the market around the same time as Intel's 18A chips (first half of 2026), or maybe even a few months later than Intel. So, that's nothing I would call "aggressive strategy", as both AMD and Intel are moving along toe to toe, as it seems.Reply -

TerryLaze Reply

How isn't being toe to toe aggressive?!ottonis said:So, that's nothing I would call "aggressive strategy", as both AMD and Intel are moving along toe to toe, as it seems.

I mean sure, it's just normal pace and that's what amd would do even without intel being there but as far as sensationalism this is like very low. -

ottonis Reply

Well, depends on what one associates with the term "aggressive". For me, aggressive means that a company is really pushing forward and taking the lead. So, if AMD were to bring their N2-based chips to market subsantially earlier than Intel their own 18A chips - now that would indeed be "agressive" in the best sense of this word.TerryLaze said:How isn't being toe to toe aggressive?!

I mean sure, it's just normal pace and that's what amd would do even without intel being there but as far as sensationalism this is like very low.