New RISC-V microprocessor can run CPU, GPU, and NPU workloads simultaneously

One core to rule them all?

X-Silicon Inc. (XSi) has created a new RISC-V microprocessing chip architecture that combines a RISC-V CPU core with vector capabilities and GPU acceleration into a single chip. The CPU/GPU hybrid chip is open-standard and will reportedly be open-source as well, Jon Peddie Research reports, and it's designed to handle a variety of different functions, including AI, which dedicated CPUs and GPUs would normally handle. The catch is that it's supposed to do all this in a far more efficient manner.

The new CPU/GPU hybrid is designed as a “jack of all trades” processor. According to JPR, the industry has been seeking an open-standard GPU that's flexible and scalable enough to support a variety of markets, including virtual reality, automobiles, and IoT devices. This new RISC-V CPU/GPU aims to solve this issue by providing manufacturers with a single open chip design that can handle any desired workload.

X-Silicon's chip is unlike other architectures, as its design combines the capabilities of a CPU and GPU into a single-core architecture. This isn’t like the typical designs from Intel and AMD where there are separate CPU cores and GPU cores. Instead, the core itself is designed to handle both CPU and GPU tasks. In that sense, it sounds a bit like Intel's abandoned Larabee project, which attempted to use x86 for graphics and other workloads.

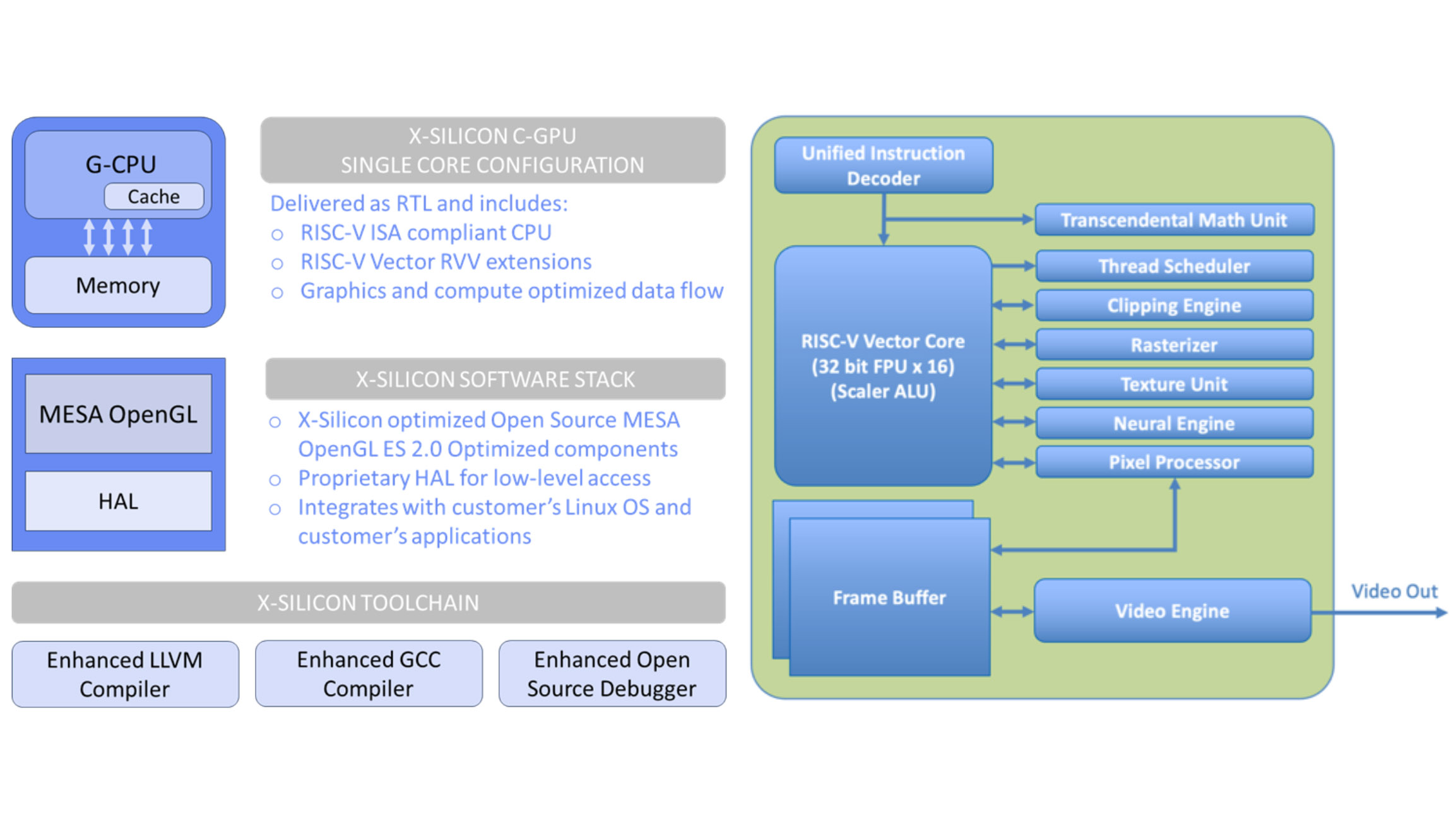

The chip utilizes X-Silicon’s C-GPU architecture that merges GPU acceleration into a RISC-V vector CPU core. The architecture has a RISC-V vector core with a 32-bit FPU and Scaler ALU. It features a Thread Scheduler, Clipping Engine, Rasterizer, Texture Unit, Neural Engine, and Pixel Processor. The chip is intended to handle applications including AI, high-performance computing (HPC), geometry computing, as well as 2D and 3D graphics.

In theory, the ability of X-Silicon’s hybrid chip to handle CPU and GPU code in the same core affords it many advantages. The chip uses the open-standard RISC-V ISA for CPU and GPU, running a single instruction stream. This provides low-memory footprint execution and better efficiency, as there's no copying of data between the CPU memory space and GPU memory space.

The CPU/GPU cores can be meshed together into a muti-core design, enabling manufacturers to scale up processing power as needed. In a multi-core format, multiple cores are tiled across a chip and connected using a speedy fabric. Fast on-chip SRAM or eDRAM caches are also implemented in this design, and these serve as an L2 cache that can aggregate data from multiple cores. Each core can be scheduled to run graphics, AI, video, physics, HPC, or other workloads independently of the other cores as needed.

With this design, X-Silicon’s C-GPU architecture can potentially run any type of CPU or GPU workload. X-Silicon claims to already have the Vulkan graphics API working with "fused GPU acceleration." This should greatly help with its development and adoption on Android devices.

As the new design is based on RISC-V, anyone can utilize the architecture without having to pay instruction-set royalty fees — unlike x86 and ARM. If it works as intended, the chips could shake up the microprocessor industry. The standard designs currently used are, in theory, not as flexible or capable as what X-Silicon claims to have created.

Whether it all works as well in practice as it does on paper remains to be seen, though we might not have to wait long to find out. Software development kits will reportedly be released to early partners sometime this year.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Aaron Klotz is a contributing writer for Tom’s Hardware, covering news related to computer hardware such as CPUs, and graphics cards.

-

ezst036 Hopefully the designs come together with the ultimate socket and the ultimate motherboard otherwise it is the ultimate thing we cannot use.Reply

Or the ultimate UEFI/BIOS update, chip uses potential socket AM5/LGA1700? -

Findecanor Whatever it is, at least it is both buzzword and superlative-compliant ...Reply

The description reminded me of Tachyum's promises of a "universal processor", which we also know very little about. Although people have compared RISC-V's vector unit with GPU's compute units for a while now.

I could find only one of the "14" patents: an application for a Dynamic processing memory core on a single memory chip.

In descriptions of the company, it supposedly in the "embedded", "low power" sector.

Is their target to be GPUs in smartphones? -

ekio Wow, a core that can handle cpu/gpu/npu tasks...Reply

If this is efficient, that means that most of the transistors can be used instead of a small part of the die.

But I bet this kind of tech will be killed by a bigger company that doesn't want any threat to their old business model. -

Conor Stewart Whilst it claims to be a RISC-V processor and have a "RISC-V ISA compliant CPU", will the chip as a whole actually fully comply with the RISC-V ISA and it's extensions? I would be very surprised if they are able to create this and have the whole thing fully compliant. They do only say it is "RISC-V based".Reply

as its design combines the capabilities of a CPU and GPU into a single-core architecture. This isn’t like the typical designs from Intel and AMD where there are separate CPU cores and GPU cores.

The chip uses the open-source RISC-V ISA for CPU and GPU

There seems to be a lot of contradiction or confusion. Why do they need to specify they use RISC-V for the CPU and GPU if the CPU and GPU are actually combined into a single core and uses a "single-core architecture".

The CPU/GPU cores can be meshed together into a muti-core design

Note the plural here in "cores" and that they say "CPU/GPU cores", if it was one single core then wouldn't they just say their hybrid core can be meshed into multi core designs?

RISC-V microprocessing chip architecture that combines a RISC-V CPU core with vector capabilities and GPU acceleration into a single chip.

Again this seems to imply that the CPU cores and the GPU acceleration are separate. Interestingly they call them CPU and GPU cores but when referring to what they have made they only refer to it as a "hybrid chip" why not call them hybrid cores? From this quote they also say it combines a CPU core with a GPU acceleration into a single chip, this seems to me to also be implying that the CPU and GPU are actually separate.

Also very important is what it says in the image:

Proprietary HAL for low level access

If it is fully RISC-V based and compliant then why do they need a proprietary HAL?

Also in the image:

RISC-V ISA compliant CPU

They also say elsewhere that the CPU and GPU are RISC-V ISA so is the GPU not compliant?

Too much of what they say could be seen as vague or slightly contradicting itself so something doesn't seem quite right. They really should clarify exactly what they mean.

It seems to me they may be using separate CPU and GPU cores but claiming it is a single core architecture because they are both RISC-V based. -

bit_user ReplyA completely open-source 'ultimate' chip?

@JarredWaltonGPU can these guys ever learn? "Open source" would be if they put the hardware design up on a public github repo for anyone to download, layout, and send to a fab to have it manufactured. That's not at all what they did, any more than it's what Intel or AMD does.

As the new design is based on RISC-V, anyone can utilize the architecture without having to pay instruction-set royalty fees — unlike x86 and ARM.

This part is better, but "architecture" is an overloaded term. It could refer to:

System architecture - the part of the machine specification that tells the operating system how to boot the CPU, configure the page translation tables, how interrupts are handled, etc.

SoC architecture - the high-level design of a SoC, including its interconnect network, I/O, cache hierarchy, and core configuration.

Instruction Set Architecture (ISA) - specifies the instruction op codes, their semantics & behavior, the register files, instruction scheduling constraints, etc. Basically, the details central to writing programs for the cores that implement it.

Micro-architecture - the detailed, internal design of the cores, including things like the way they're pipelined, their branch-predictor, the micro-ops the front-end decodes to, details of the micro-op cache, if they have one, their physical register file, if it's distinct from the logical register file specified in the ISA, etc. Basically, all the internal details that software doesn't usually need to worry about.

So, what's open about RISC-V is the ISA (#3) and I believe at least some core parts of the system architecture (#1). -

bit_user As for the claim of this being a ground-breaking, first-of-its-kind approach ...eh, sort of.Reply

Think Silicon has a line of NEOX iGPUs, targeted at embedded markets, which is RISC-V based:

https://www.think-silicon.com/neox

I think their claims are slightly more modest, in that they don't claim to be the only kind of core you need - just that you could run generic RISC-V code on the iGPU, if you wanted to.

More recently, Imagination has announced something similar:

https://www.tomshardware.com/pc-components/cpus/imagination-and-ventana-to-build-a-risc-v-cpu-gpu-platform

I think the Jack-of-all-trades makes the most sense for small, low-cost embedded cores, where you really don't want to waste die space on a separate set of CPU and GPU (and AI) cores. That's where I think it makes the most sense to prioritize flexibility and area efficiency over performance or energy-efficiency. -

JarredWaltonGPU Reply

Tweaked the tagline, though it's worth noting that JPR says the company will open-source the material. It hasn't happened yet, AFAIK, but it could potentially happen. Maybe. Unless the company pulls an OpenAI and shuts down all the "open" aspects. LOLbit_user said:@JarredWaltonGPU can these guys ever learn? "Open source" would be if they put the hardware design up on a public github repo for anyone to download, layout, and send to a fab to have it manufactured. That's not at all what they did, any more than it's what Intel or AMD does.

This part is better, but "architecture" is an overloaded term. It could refer to:

System architecture - the part of the machine specification that tells the operating system how to boot the CPU, configure the page translation tables, how interrupts are handled, etc.

SoC architecture - the high-level design of a SoC, including its interconnect network, I/O, cache hierarchy, and core configuration.

Instruction Set Architecture (ISA) - specifies the instruction op codes, their semantics & behavior, the register files, instruction scheduling constraints, etc. Basically, the details central to writing programs for the cores that implement it.

Micro-architecture - the detailed, internal design of the cores, including things like the way they're pipelined, their branch-predictor, the micro-ops the front-end decodes to, details of the micro-op cache, if they have one, their physical register file, if it's distinct from the logical register file specified in the ISA, etc. Basically, all the internal details that software doesn't usually need to worry about.

So, what's open about RISC-V is the ISA (#3) and I believe at least some core parts of the system architecture (#1). -

Pierce2623 Reply

It was kinda mind-blowing how quickly OpenAI went from a non-profit with open source models and a heavy emphasis on “safe” AI to a for-prophet behemoth.JarredWaltonGPU said:Tweaked the tagline, though it's worth noting that JPR says the company will open-source the material. It hasn't happened yet, AFAIK, but it could potentially happen. Maybe. Unless the company pulls an OpenAI and shuts down all the "open" aspects. LOL -

bit_user TL;DR: maybe they're contributing some new RISC-V instruction opcodes to the standard, but it would be awesome & very journalistic of you guys to shoot X-Silicon a quick email and ask exactly what's meant by this "open source" talk.Reply

Thanks for pointing that out. I've now read the JPR report and that's definitely a muddled mess.JarredWaltonGPU said:Tweaked the tagline, though it's worth noting that JPR says the company will open-source the material. It hasn't happened yet, AFAIK, but it could potentially happen.

Unfortunately, I can't find any press release on the newswire that JPR is reporting. Furthermore, a visit to the News tab of x-silicon's site just pulls up an even older article by JPR.

So, given that all we have to go on is the JPR article, let's spread out the entrails and try to see if they're trying to convey any coherent message, or if we can at least find where JPR got confused.

"X-Silicon Inc. (XSi) revealed its open-standard, low-power C-GPU architecture, combining GPU acceleration with a RISC-V vector CPU core and tightly coupled memory for a low-power, single-processor solution. It is an open-sourcing of its unified RISC-V vector CPU-with-GPU ISA and offers register-level hardware access via a hardware abstraction layer (HAL)."First, nothing I can find about X-Silicon says they're trying to establish their architecture as an open-standard. I guess the first sentence could allude to the set of standard RISC-V instructions they implemented, but it's a confusing use of "architecture".

Then, it goes on to talk about open-sourcing their ISA, which is basically nonsense. I guess they could mean they implemented new RISC-V instructions that they're trying to get included in the ISA.

"For over 20 years, the industry has been seeking an open-standard GPU ..."Here, I suppose he's talking about each GPU being a proprietary implementation, at the hardware level. Of course, there are open-standard APIs for programming them, like OpenGL, OpenCL, and Vulkan. However, with no standard for the actual hardware, you're reliant on the manufacturer to provide support for those or other APIs.

"X-Silicon Inc (XSi), a San Diego based start-up founded in March 2022, unveiled its latest innovation: the open-standard, low-power C-GPU architecture, merging GPU acceleration into a RISC-V vector CPU core with tightly coupled memory, offering a low-power, single-processor solution. XSi’s approach introduces open-sourcing of its unified RISC-V vector CPU-with-GPU ISA and provides register-level hardware access through a hardware abstraction layer (HAL). That, says the company, empowers OEMs and content providers to tailor drivers and applications with unusual customization, diverging from the closed solutions of competitors."Again, talking about open-sourcing the ISA. The following sentence talks about the implications for software that's running on the chip. If they were really open-sourcing the hardware he would be spinning a different value proposition.

"XSi’s open-standard, low-power C-GPU architecture and NanoTile platform suggest a paradigm shift in GPU technology. With its support of open standards, customizable hardware access, and approach to dynamic content rendering, XSi thinks it will set a new standard for GPU architecture, empowering developers and OEMs to unlock unprecedented levels of performance and efficiency in graphics rendering and AI/ML-compute applications."Again, it's not clear if the "open-standard" architecture merely refers to the use of RISC-V, or if there are new instructions they've implemented that they're trying to contribute back to RISC-V, where others can also implement them.

"The company reports the RISC-V ecosystem is reacting positively to the launch of a new compute-graphics company that is fully committed to furthering the open-standard ecosystem."More general excitement about RISC-V.

The company plans to make its software development kits available to a select set of early development partners later this year.Ooooh... yeesh. That's not very open, eh? If the programming model of the hardware were an open standard, they'd be talking about when they're going to publish it. If they were opening even more, they'd be talking about like a github repo they're going to publish or open up.

Best-case scenario, they've created some new RISC-V instructions they're now trying to standardize. I think that's about the extent of their openness.JarredWaltonGPU said:Maybe. Unless the company pulls an OpenAI and shuts down all the "open" aspects. LOL

If you search the entire article for the word "source" or "sourcing", the only hits are basically 2 repetitions of this construct:

"open-sourcing of its unified RISC-V vector CPU-with-GPU ISA"In both cases, talking about the ISA. That could mean what I said above, but it's quite a stretch to read anything more dramatic into it.

I also did a little bit of web-searching, to see if there was anything special about this company, or if they had publicly said anything else about open source. I found neither. -

bit_user Reply

Uh, according to this, it sure does have vector support!TheoKrom said:There is also another one by Think Silicon targeted without Vector support for low end devices.

It doesn't even make sense to have a GPU architecture that lacks any kind of vector support. Perhaps wherever you read that about its vector support was complaining that they didn't implement the standard RISC-V vector instructions? Those were only standardized somewhat recently - maybe not in time for the first NEOX?

P.S. I just noticed your profile pic is someone standing in front of a Think Silicon logo. If that's really you, would you care to tell us more?