Chiplet processors leverage light-based communication — new active optical interposers connect multi-chiplets with minimal latency

CEA-Leti are looking for commercial partners

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

As the era of multi-chiplet designs looms, chiplet-to-chiplet interconnections become an important battleground as their performance and power consumption can define how competitive a particular design is. CEA-Leti, a European technology research institute, recently demonstrated a unique technology that may have a disruptive impact in the coming years: active optical interposers that can be used to connect chiplets, reports EE Times Europe.

CEA-Leti's optical interposer technology is called Starac and the research institute demonstrated it at its Leti Innovation Days 2024 which took place this summer.

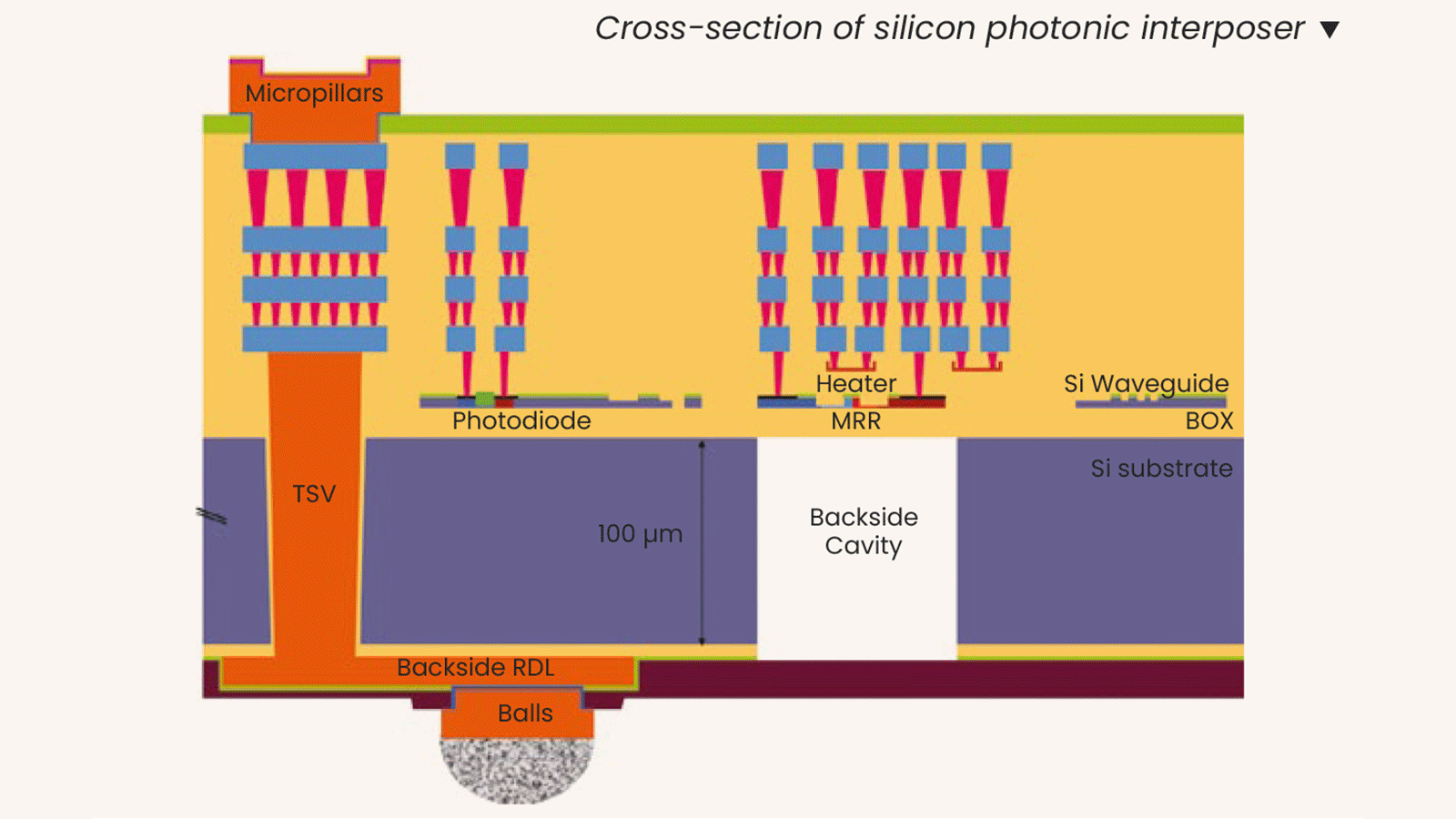

Starac uses silicon photonics instead of copper to transfer data, which automatically improves performance as well as reducing latency and power consumption. It also enables routing that cannot be built using conventional methods. Unlike traditional passive interposers used to connect chiplets that require multiple steps (or hops) for data to travel between distant chiplets, active optical interposers integrate logic circuits that enable direct communication.

The Starac demonstrator, introduced by CEA-Leti, showcases this technology with a network-on-chip (ONoC) design comprising of four chiplets (with 16 cores each), six electro-optical drivers, Ø10 x 100 μm mid-process TSVs, and four front-side routing levels. Its spiral waveguide structure (impossible to build on a passive interposer) enables chiplets to communicate directly with each other, bypassing the need for intermediary hops. This eliminates delays common in conventional multi-chiplet designs and latencies are getting more important as the number of chiplets continues to grow.

Article continues belowCutting down latency while increasing bandwidth and keeping power consumption in check is crucial for current and future multi-chiplet system-in-packages. Optical interposers like those in the Starac system allow multiple processors and high-bandwidth memory units to quickly and efficiently exchange data, even over long distances within a system. CEA-Leti's work marks a significant step toward using photonics for faster, more scalable communication solutions for SiPs.

Being a research institute, CEA-Leti does not produce anything. CEA-Leti is actively seeking industrial partners to further develop its Starac demonstrator and eventually commercialize its active optical interposer technology. Building the Starac was very challenging as it required CEA-Leti to develop manufacturing approaches that do not exist just yet.

Now, the institute aims to collaborate with both SiP designers, who would use the new technology, and foundries, to prepare the technology for large-scale production. For now, the research project looks promising, but CEA-Leti and its potential partners have to refine their manufacturing process before it can be put into high-volume production.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Elf_Boy AMD could go to town (I am guessing) with this tech. Will it be in the Ryzen 10950x3d (or is that too soon) in the 12/13 series? Maybe? Inter CCD latency (and associated issues) does seem to be the big problem for AMD to solve. I wonder what the next bottle neck will be? And if it is a big enough one will it make fixing latency less of or no issue?Reply