TSMC charts a course to trillion-transistor chips, eyes 1nm monolithic chips with 200 billion transistors

TSMC mulls A14, A10 process technologies in the next few years.

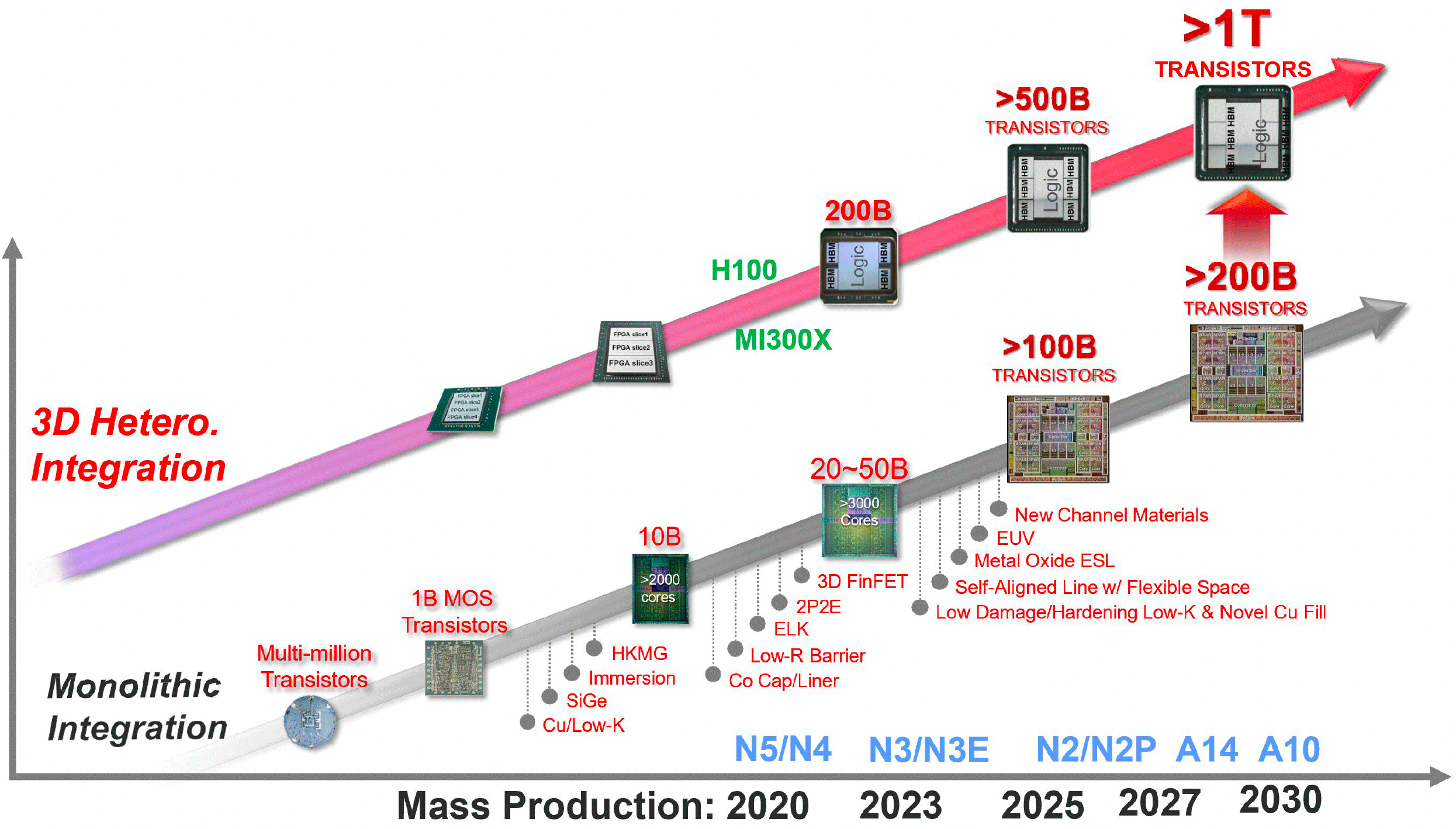

At the IEDM conference, TSMC charted a course to delivering chip packages with one trillion transistors, much like Intel divulged last year. Those behemoths will come courtesy of 3D-packaged collections of chiplets on a single chip package, but TSMC is also working to develop chips with 200 billion transistors on a single piece of silicon. To meet that goal, the company reaffirmed that it is working on 2nm-class N2 and N2P production nodes and 1.4nm-class A14 and 1nm-class A10 fabrication processes that are due by 2030.

In addition, TSMC foresees advancements in packaging technologies (CoWoS, InFO, SoIC, etc.), allowing it to build massive multi-chiplet solutions packing more than a trillion transistors around 2030.

The development of leading-edge process technologies has slowed somewhat during recent years as chipmakers face technological and financial challenges. TSMC faces the same challenges as other companies, but the world's largest foundry is confident that it will be able to advance its production nodes in terms of performance, power, and transistor density in the next five or six years as TSMC launches its 2nm, 1.4nm, and 1nm nodes.

Nvidia's 80-billion-transistor GH100 is one of the most complex monolithic processors on the market, and according to TSMC, there will be even more complex monolithic chips with over 100 billion transistors soon. But building such large processors is getting more complex and expensive, so many companies opt for multi-chiplet designs. For example, AMD's Instinct MI300X and Intel's Ponte Vecchio consist of dozens of chiplets.

This trend will continue, and several years down the road, we will see multi-chiplet solutions consisting of over a trillion transistors, according to TSMC. But at the same time, monolithic chips will continue to gain complexity, and we will see monolithic processors featuring a whopping 200 billion transistors, according to one of TSMC's presentations at IEDM.

TSMC and its customers must develop both logic and packaging technologies in lockstep, with the former feeding the latter with density improvements, which is why the company included both the evolution of production nodes and the packaging technologies on the same slide.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

George³ It's a grim prospect. I don't even know how to arrange so many tightly packed transistors to work. It was a time when transistors were few and far between. And now we read about times when there will be more and more redundant, perhaps completely unnecessary, number of transistors.Reply -

usertests Reply

Last I heard, "AI" is being used to arrange them and cut down on inefficiencies.George³ said:It's a grim prospect. I don't even know how to arrange so many tightly packed transistors to work. It was a time when transistors were few and far between. And now we read about times when there will be more and more redundant, perhaps completely unnecessary, number of transistors. -

neojack how would 1nm be even possible without triggering quantum effects ?Reply

going to 2 to 1 nm essentially means doubling the process's efficiency in like 3 years. it's very ambitious. -

bit_user Reply

Because these numbers are just marketing lies.neojack said:how would 1nm be even possible without triggering quantum effects ?

At best, they refer to relative areal density improvements. However, density could be improved in many ways, such as backside power delivery, because it reduces the amount of die area spent on power delivery, thereby improving logic density. All, without actually shrinking any of the logic elements, yet they count it as a density improvement, because that's the net effect.

One advancement they've revealed is a new transistor design:

https://www.tomshardware.com/news/intel-and-tsmc-to-report-on-next-gen-cfet-transistor-progress

You'll find more, here:

https://www.tomshardware.com/news/imec-reveals-sub-1nm-transistor-roadmap-3d-stacked-cmos-20-plans -

jasonf2 Reply

If you look at the slide they are noting different channel materials. Quantum tunneling happens at different rates for different materials. That isn't to say that the transistor design itself won't be designed to be more resilient to tunneling effects as well (ie thicker 3d barrier). Also the fab industry has been really bad about overstating node size to its smallest component, not the average size. That is for the most part why intel rebranded 10nm to "Intel 7" because it is really pretty equivalent to what TSMC calls 7nm. So what is 1nm really? At a real 1 nm you are only 3-10 atoms wide depending on the atom.neojack said:how would 1nm be even possible without triggering quantum effects ?

going to 2 to 1 nm essentially means doubling the process's efficiency in like 3 years. it's very ambitious.

Intel and TSMC are in a full on race right now. I think it is pretty safe to say that this last leg of the race to minimum possible transistor size is going to be really ambitious and really expensive for both companies. Contracts from companies like Qualcom, Apple, Nvidia and possibly AMD are going to make or break the bankroll for future development if these fabs really move into the $20 billion + number. -

George.a.spix Reply

There is a billion dollars hiding behind the first supplier to integrate Cadence or it's equivalent with an scanning electron Microscope or a secondary emission scanner. To scan a sample die for it's roads streets and buildings. And compare it with what was designed in the tools. Run a short test using the scan rings. And if it checks out we have some confidence that what was built is what was designed. Then back we go to the stepper and ticky tacky out die that are identical to the verified die. So we need not spend all that money within the US to create unneeded duplicate fabs in the interest of attempting to protect a given die from being altered by some government or adversary or or even business interest.. for all I know this may already be going on, but I have not seen any evidence of it. As we continue to build Fabs to build essentially the same chips. Unclear if this is because of some national interest to create your own assurance by owning the end to end process at Great expense. Rather than address the actual issue in all cases. Is what has been built what was specified?usertests said:Last I heard, "AI" is being used to arrange them and cut down on inefficiencies. -

bit_user Reply

Shouldn't it be enough just to analyze the masks? That should be easier and masks are becoming such a bottleneck in the production process that it's impractical for a bad actor to make alternate masks and swap them in. I feel like this is probably being done, on some level, just to validate that the masks don't have defects, in which case maybe what you really want to verify is the net list against the RTL.George.a.spix said:scan a sample die for it's roads streets and buildings. And compare it with what was designed in the tools.

I think that's not the main concern. The issue is quite simply the supply chain. If the governments of Taiwan or South Korea turned hostile, it could restrict or halt domestic supply of cutting edge chips, with devastating economic consequences... or have you already forgotten the Great Chip Shortage of '21 - '22? That would be just a taste of what could happen...George.a.spix said:we need not spend all that money within the US to create unneeded duplicate fabs in the interest of attempting to protect a given die from being altered by some government or adversary or or even business interest. -

George.a.spix Reply

I'm not sure I understand, if there are standard between steppers, we should not care which Fab makes the chips, so we can have any supplier do that. Just like happened when Ford came out with standards for parts. When there was a supply chain interruption they would simply go to other manufacturers who were already competing in that space on something other than design. Like quality and cost. As they were already having to track every use of apart as they needed to assign responsibility for a given failure that forced a recall to the manufacturer or that part of the supply chain that was responsible. So I believe it's in our interest to ensure that we don't care which Fab burned the part. As long as we could check at least one die out of the lot at least once before we let the steppers run wild replicating. You're right about the RTL but I believe that's one step short of an actual verification where a scanning electron microscope or a secondary emission scope can inspect not only the streets and buildings but the plumbing underneath via's Etc. I have thought about just verifying the mask but I still think this is insufficient. As we seem to be reluctant to let any Fab in the world create chips that we might need to use, including for military applications. Where if we can't use and compete parts around the world. We greatly damage our ability to fight, our security and even safety in my opinionbit_user said:Shouldn't it be enough just to analyze the masks? That should be easier and masks are becoming such a bottleneck in the production process that it's impractical for a bad actor to make alternate masks and swap them in. I feel like this is probably being done, on some level, just to validate that the masks don't have defects, in which case maybe what you really want to verify is the net list against the RTL.

I think that's not the main concern. The issue is quite simply the supply chain. If the governments of Taiwan or South Korea turned hostile, it could restrict or halt domestic supply of cutting edge chips, with devastating economic consequences... or have you already forgotten the Great Chip Shortage of '21 - '22? That would be just a taste of what could happen... -

bit_user Reply

Cutting-edge silicon fabrication is not just a commodity service, where you can swap in one manufacturer for another. Even if it were, there's a limited amount of global production capacity available.George.a.spix said:if there are standard between steppers, we should not care which Fab makes the chips, so we can have any supplier do that.

Again, I think this point is overemphasized. The main issue is just ensuring adequate supply.George.a.spix said:we seem to be reluctant to let any Fab in the world create chips that we might need to use, including for military applications.

For instance, food can be grown in any country. Does that mean we don't need to worry about growing our own food? No, most countries consider it a matter of national security to retain some domestic food production capacity, even when it must be subsidized to make it economically viable.

Same thing, here. -

usertests Reply

This is the exact thing I was thinking of when I wrote the comment, DREAMPlace:George.a.spix said:There is a billion dollars hiding behind the first supplier to integrate Cadence or it's equivalent with an scanning electron Microscope or a secondary emission scanner. To scan a sample die for it's roads streets and buildings. And compare it with what was designed in the tools. Run a short test using the scan rings. And if it checks out we have some confidence that what was built is what was designed. Then back we go to the stepper and ticky tacky out die that are identical to the verified die. So we need not spend all that money within the US to create unneeded duplicate fabs in the interest of attempting to protect a given die from being altered by some government or adversary or or even business interest.. for all I know this may already be going on, but I have not seen any evidence of it. As we continue to build Fabs to build essentially the same chips. Unclear if this is because of some national interest to create your own assurance by owning the end to end process at Great expense. Rather than address the actual issue in all cases. Is what has been built what was specified?

https://developer.nvidia.com/blog/autodmp-optimizes-macro-placement-for-chip-design-with-ai-and-gpus/

But there's more:

https://blogs.nvidia.com/blog/ai-acceleration-dally-dac/https://www.hpcwire.com/2022/04/18/nvidia-rd-chief-on-how-ai-is-improving-chip-design/https://blogs.nvidia.com/blog/itf-world-2023/

They're even supposedly getting some usefulness out of a chatbot:

https://blogs.nvidia.com/blog/llm-semiconductors-chip-nemo/