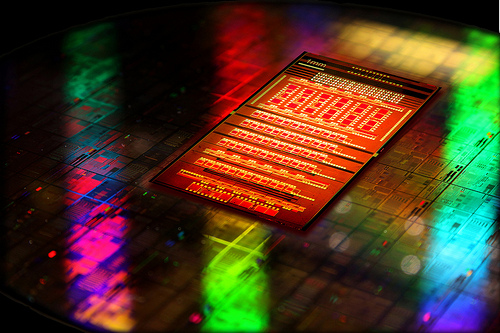

MIT Advances E-Beam Lithography for Chips

Researchers at MIT consider e-beam lithography as a potential future candidate for semiconductor mass production.

It is unclear how far in the future, as the current immersion lithography technology has been much more stubborn than we originally thought a decade ago. Companies such as Intel, have successfully pushed out the adoption of the extremely expensive transition to extreme ultraviolet lithography (EUV) so far.

MIT researchers now believe that e-beam lithography, which is commonly used for prototyping and is currently a slow and low-volume production process for semiconductors, could be an option for chip manufacturers as the technology can be scaled down to structures of 9 nm. Compared to e-beam lithography, traditional photolithography uses light that shines through the entire surface of a mask at once. The e-beam uses electrons that scans across the surface of the resist (a material that covers each layer of a chip) on a row-by-row basis.

The MIT researchers said that they were able to increase the efficiency of e-beam lithography by using a thinner mask, which requires less energy per beam and enables a higher number of parallel electron beams to accelerate the production process. They also said they used a common table salt solution to "develop the resist, hardening the regions that received slightly more electrons but not those that received slightly less."

Article continues belowThere is doubt that the MIT approach will find its way into production. One manufacturer of lithography systems, Mapper, said that the presented system was "a little bit too sensitive."

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Douglas Perry was a freelance writer for Tom's Hardware covering semiconductors, storage technology, quantum computing, and processor power delivery. He has authored several books and is currently an editor for The Oregonian/OregonLive.

-

house70 "One manufacturer of lithography systems, Mapper, said that the presented system was "a little bit too sensitive."Reply

Time will prove Mapper wrong. If you can't imagine something, that doesn't mean it's impossible. -

house70 this is not a question about imagination they are basically saying the resist system is too sensitive when combined the noise inherent in their exposure tool to give the type of results customers are asking for. Sounds like the researchers haven't been listening hard enough to their end customers which strikes me as bad business.Reply

-

phatboe OK I don't know too much about transistor lithography but I thought the main problem with going to smaller scales wasn't so much that they couldn't make smaller transistors but that was the transistor size shrinks electron tunneling which leads to current leakage increases.Reply

How will using an E-beam help with that? -

alidan phatboeOK I don't know too much about transistor lithography but I thought the main problem with going to smaller scales wasn't so much that they couldn't make smaller transistors but that was the transistor size shrinks electron tunneling which leads to current leakage increases.How will using an E-beam help with that?Reply

im guessing that it would make it more accurate, and if dont right, make the process faster than it currently is.

how long does it take now to process a chip? and how much of that time is waiting on crap to finish? -

dogman_1234 It seems to better manufacturing, not really changing how the transistor works. Some research is also being done on using graphene as a template, but still too small for light.Reply

Best chances the semiconductor industry has is to build transistors by atom. -

cheepstuff phatboeOK I don't know too much about transistor lithography but I thought the main problem with going to smaller scales wasn't so much that they couldn't make smaller transistors but that was the transistor size shrinks electron tunneling which leads to current leakage increases.How will using an E-beam help with that?Reply

Of course shrinking to smaller scales is a problem. If it wasn't why didn't we reach the theoretical transistor size limit a decade ago? Making transistors smaller is a problem that may escape our notice, however because chip makers have been able to consistently whittle down sizes since the first CPU.

MIT has revisited and possibly improved on a lithography method that, although less expensive than Intel's method, has a yield that is too low volume to be practical in mass production. It has nothing to do with the transistor size limit, there is a whole lot more involved with chip fabrication than a single theoretical boundary the industry has not run into yet. -

We're already at the point of diminishing returns, it'll only get worse from here. 40, 32, 28 and 22nm have been problematic for everyone. Fortunately, Intel PR convinced everyone it wasn't, with "we haven't made a 32nm quad yet because we don't feel the need to" and "please disregard that the 22nm delay has ruined our stated tick-tock strategy".Reply

Leakage is the enemy, and it's going to be exponentially worse at future nodes. -

bison88 How small can they go is the question before having to move into a different direction instead of shrinkage to increase processing power?Reply -

whatisupthere phatboeOK I don't know too much about transistor lithography but I thought the main problem with going to smaller scales wasn't so much that they couldn't make smaller transistors but that was the transistor size shrinks electron tunneling which leads to current leakage increases.How will using an E-beam help with that?Reply

I may be wrong but I believe phatboe is talking about quantum tunneling. To keep it simple. The cpu is made up of many circuits with paths for electrons to flow. The paths are divided by barriers to electron flow. When the barrier width becomes to small it cannot contain the electrons very well. Even if the barriers are really really high it doesn't matter because the electron can just appear on the other side sometimes. This results in increased current leakage. I believe it is supposed to become a major problem at 9nm. I imagine this technology would not help with this problem. anyone have insight on this?