Micron unveils MRDIMMs for Intel Xeon 6: Up to 256GB DDR5-8800 modules

Next-gen memory for next-gen servers.

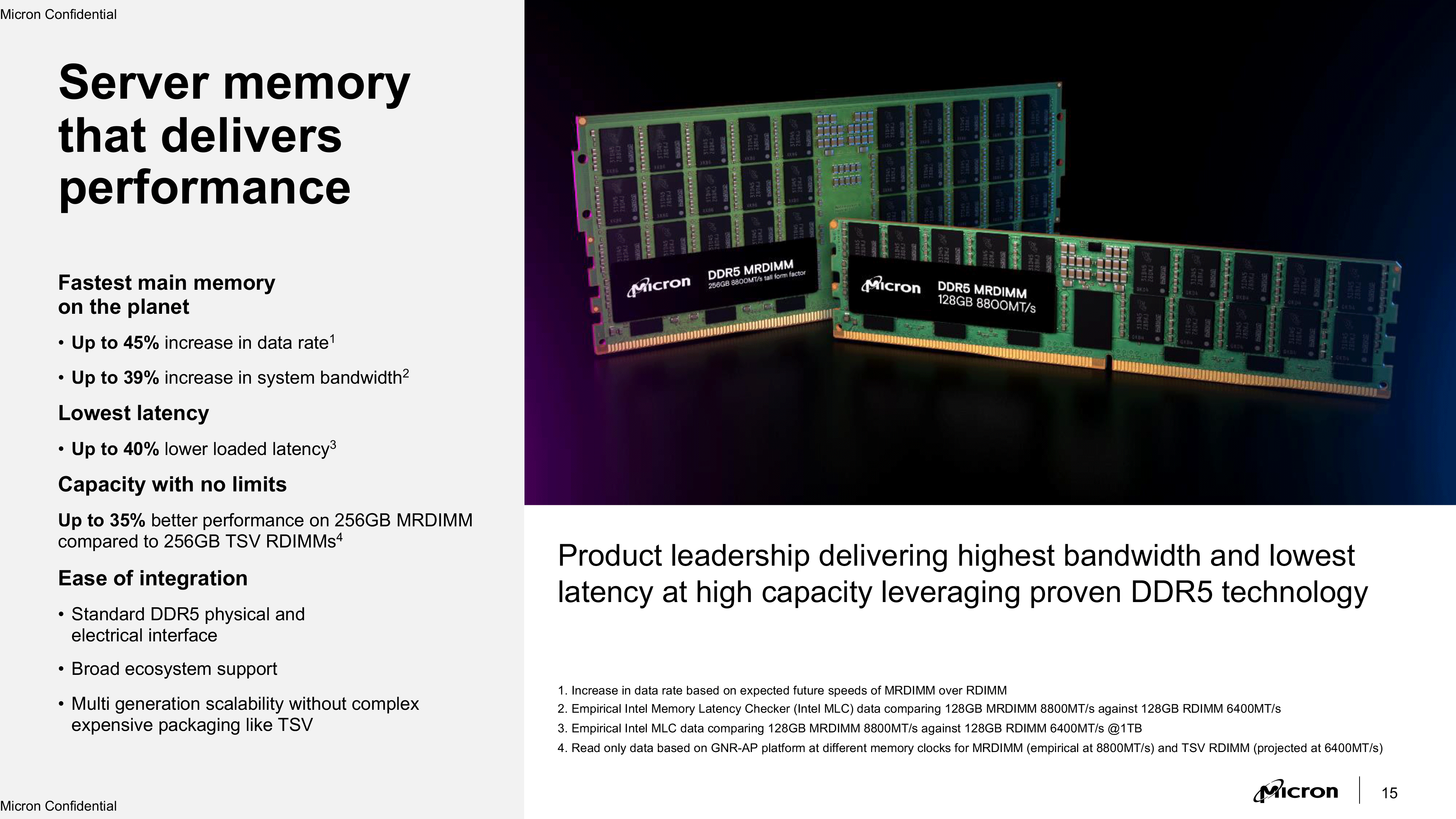

Micron Technology has introduced its new multiplexed rank dual inline memory modules (MRDIMMs) designed to combine high performance, low latency, high capacity, and predictable power consumption for next-generation Intel Xeon 6 server platforms. As the number of cores per socket rise, the new modules will be particularly useful to ensure decent per-core memory bandwidth, which will be valuable for artificial intelligence (AI) and high-performance computing (HPC) applications.

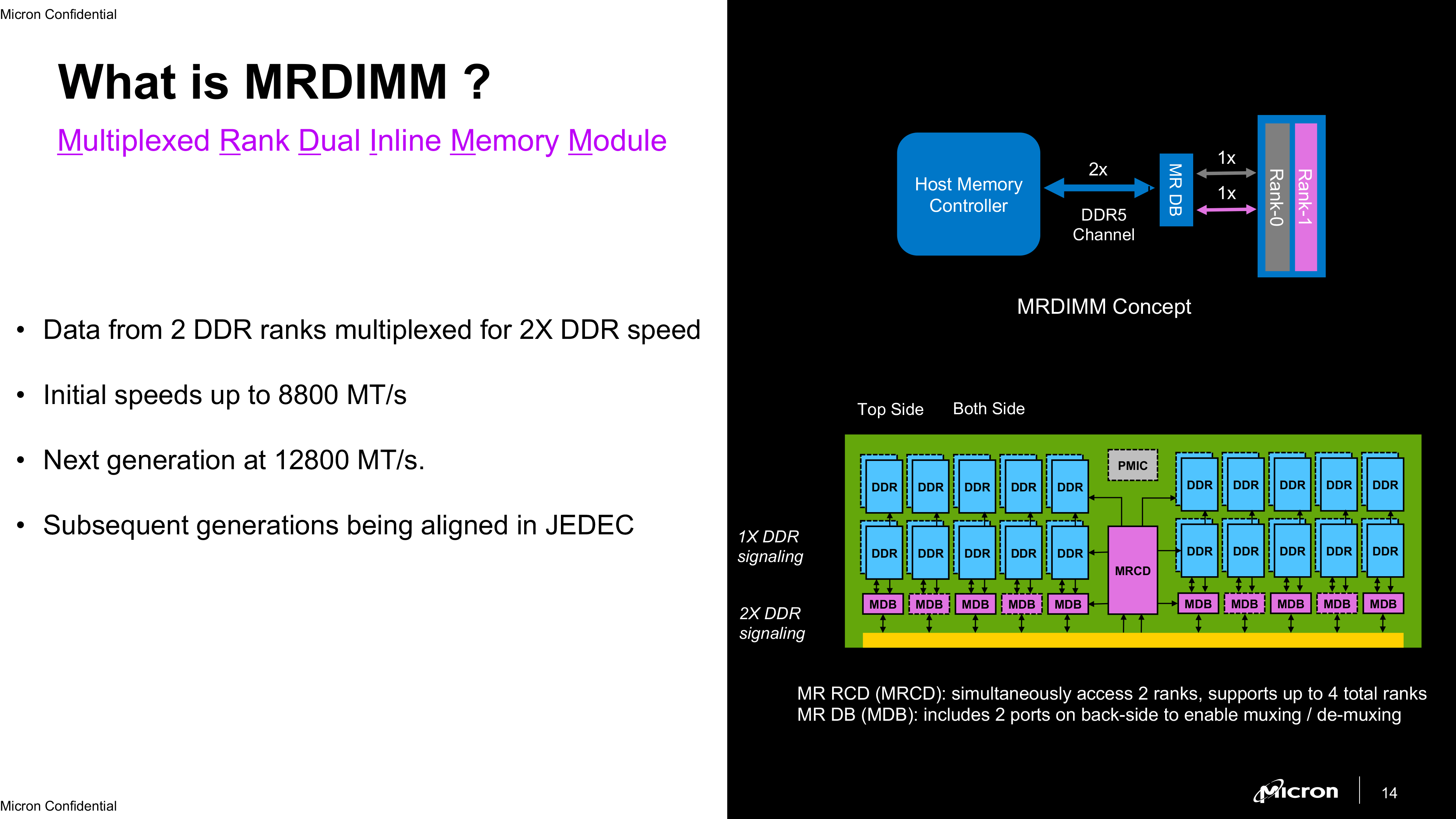

MRDIMMs are JEDEC-standardized next-generation memory modules that essentially feature two DDR ranks that run in a multiplexed mode to double the speed. To enable such operation, the modules are equipped not only with more memory devices, but also with an MRCD chip that allows simultaneous access to both ranks and MDB chips that enable muxing and demuxing. The host CPU interacts with an MRDIMM module at an 8800 MT/s data transfer rate (for the first generation, the next generation expected to reach 12800 MT/s), but all the components on the module work at half the rate, enabling to tighter latencies and keeping power consumption of the module in check.

Lower latencies greatly increases the real-world performance of memory subsystems. Micron and Intel claim that a 128 GB DDR5-8800 MRDIMM can offer an up to 40% lower loaded latency than a 128 GB DDR5-6400 RDIMM. As for power consumption, keeping it in chip is important for modern server platforms as combined consumption of memory modules can be comparable or even higher than power consumption of some server CPUs.

"Micron's latest innovative main memory solution, MRDIMM, delivers the much-needed bandwidth and capacity at lower latency to scale AI inference and HPC applications on next-generation server platforms," said Praveen Vaidyanathan, vice president and general manager of Micron’s Compute Products Group. "MRDIMMs significantly lower the amount of energy used per task while offering the same reliability, availability and serviceability capabilities and interface as RDIMMs, thus providing customers a flexible solution that scales performance. Micron’s close industry collaborations ensure seamless integration into existing server infrastructures and smooth transitions to future compute platforms."

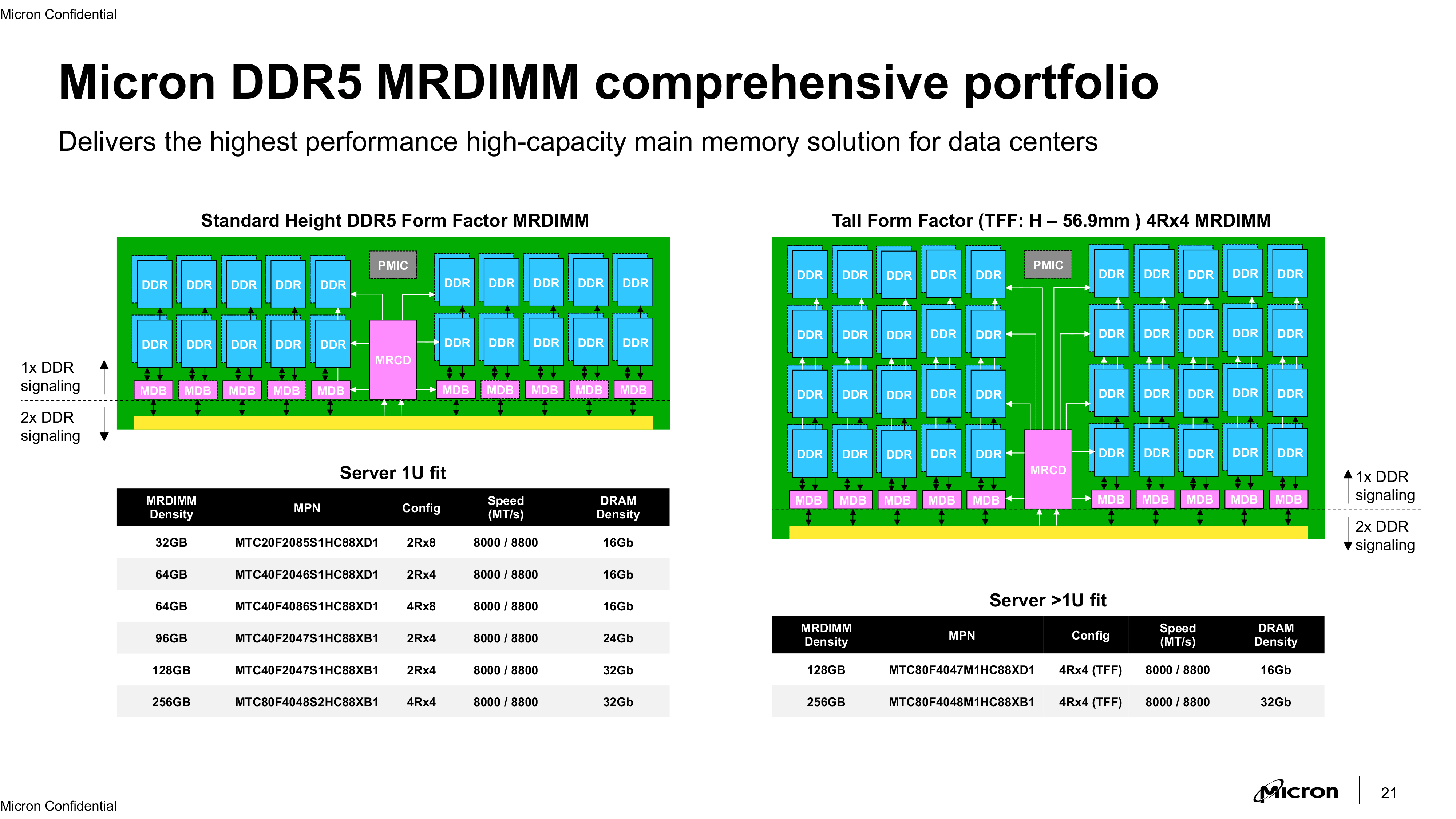

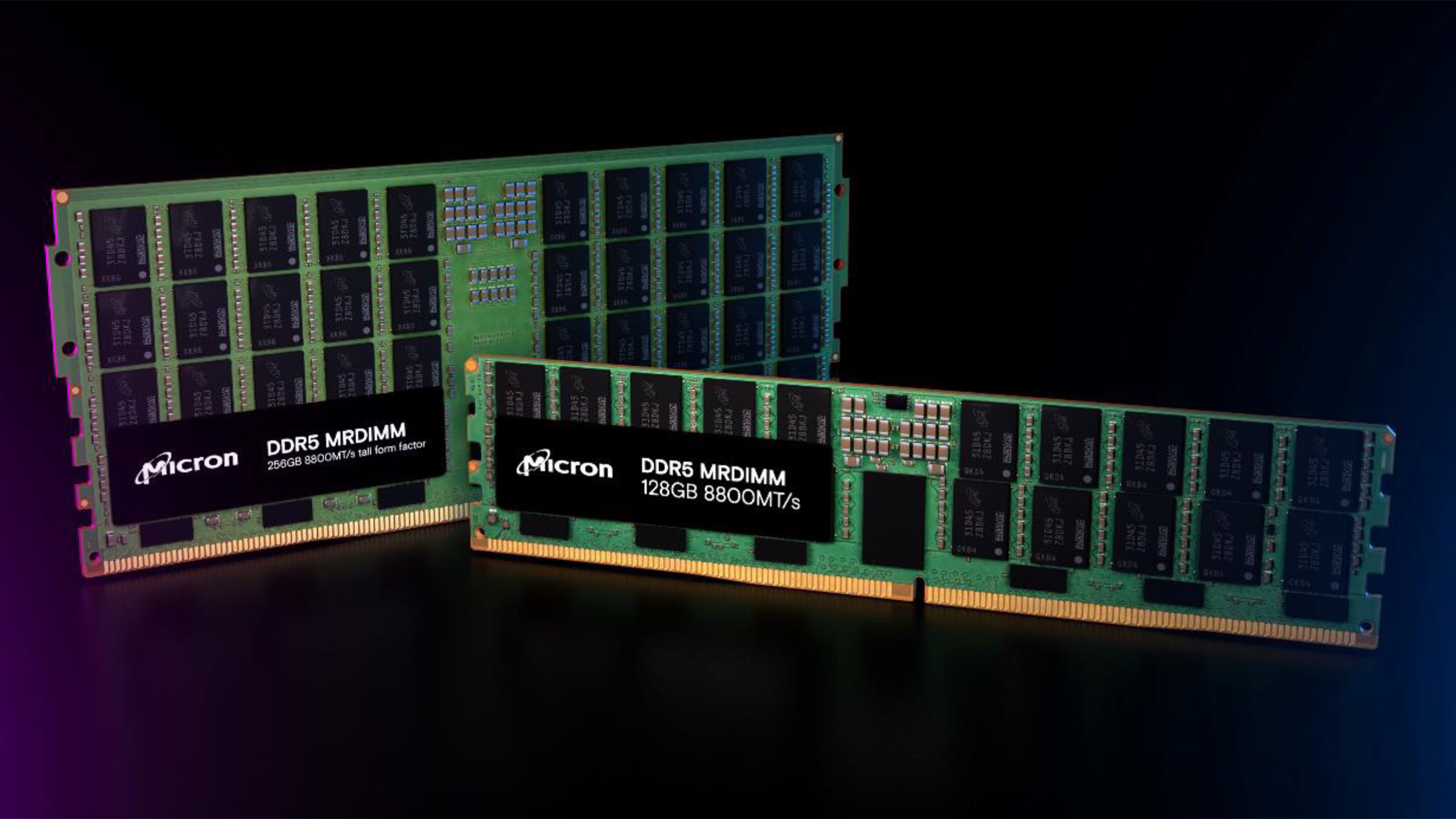

Micron plans to offer a comprehensive line-up of DDR5-8000 and DDR5-8800 MRDIMMs in both standard and tall form factors (TFF) based on 16 Gb, 24 Gb, and 32 Gb DDR5 DRAM devices made using its proven 1β technology. Standard-height MRDIMMs will be available in 32 GB, 64 GB, 96 GB, 128 GB, and 256 GB density without using any 3D-stacked DRAM devices, which means higher performance, lower power, and lower costs. TFF MRDIMMs with a 56.9 mm height and aimed at over 1U servers will be available in 128 GB and 128 GB capacities.

Tall form-factor MRDIMMs have a larger surface area compared to standard-sized modules, which, for the same airflow, results in a 24% lower temperature. This design reduces the likelihood of thermal throttling and enhances energy efficiency, making them particularly suitable for AI and HPC machines.

Upcoming MRDIMMs from Micron and other suppliers (including both first-party makers like Samsung and SK Hynix and third-party suppliers like Adata) are set to be compatible with Intel's Xeon 6 platforms. On the software side of matters, DDR5 MRDIMMs do not require any software development or turning, though expect large server OEMs like Dell, HPE, and Lenovo to run comprehensive tests to ensure compatibility and stable performance across hundreds of workloads.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Micron's MRDIMMs are currently sampling and are expected to ship in volume in the latter half of 2024. Subsequent generations promise even greater performance, with up to 45% better memory bandwidth per channel – at 12800 MT/s — compared to current RDIMMs at 6400 MT/s.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

rluker5 My tuned DDR5 runs at a latency of 55ns. Which isn't great, but seems fairly decent. If these new Mr.DIMMs can knock 40% off of that it would put the latency in L3 cache range.Reply

That sounds too good to be true. But if it is then it would also change how CPUs are built with large L2 taking priority and large L3 becoming irrelevant.

Edit: The Dec 2021 Micron DDR5 DIMMS I have could only do about 65ns latency so 60% of that drops it to 39ns tuned, which is not quite as good as L3 anymore. Hopefully Hynix figures out a way to make these. -

anoldnewb OnReply

60% of 55ns is 33 ns. L3 Cache is about 10ns latency (40 cycles at 4 GHz) so there is still a large difference compared to DDR5 memory.rluker5 said:My tuned DDR5 runs at a latency of 55ns. Which isn't great, but seems fairly decent. If these new Mr.DIMMs can knock 40% off of that it would put the latency in L3 cache range.

That sounds too good to be true. But if it is then it would also change how CPUs are built with large L2 taking priority and large L3 becoming irrelevant.

Edit: The Dec 2021 Micron DDR5 DIMMS I have could only do about 65ns latency so 60% of that drops it to 39ns tuned, which is not quite as good as L3 anymore. Hopefully Hynix figures out a way to make these.

From nice article at chipsandcheese -AMD’s Zen 4, Memory Subsystem