AMD's Jaguar to Support AVX

A note posted by an AMD developer suggests that the Kabini processor, a 28 nm mobile chip that will integrate the Jaguar processing core, will support Intel's AVX instruction set, as well bit-manipulation instructions (BMI).

The quote:

"We are expecting some changes to tunings and costs. We will update them in near future. There are ISA changes as well like btver2 supports AVX, BMI."

It was recently reported that AMD scrapped SSE5 in favor of AVX, which is likely to also introduce SSE4 in Jaguar. Jaguar's predecessor Bobcat only supports SSE3.

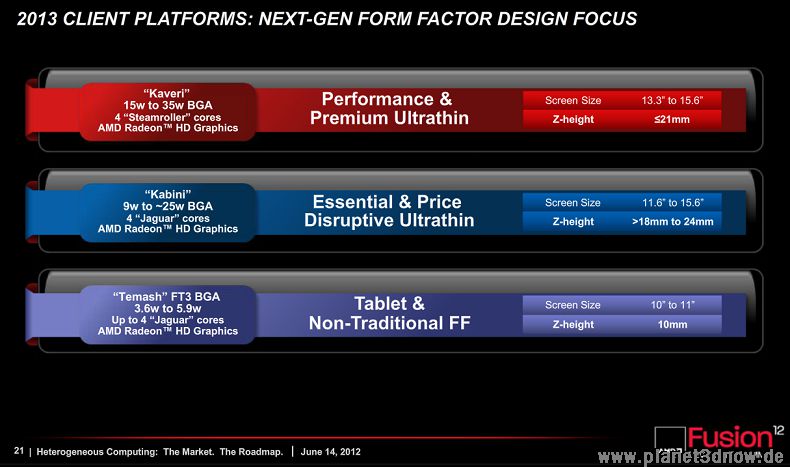

Article continues belowKabini is expected to be released in 2013 as a low-price and low-power mobile processor with up to four cores and a power envelope spanning 9 to 25 watts. The program of the upcoming Hot Chips 24 conference in Cupertino indicates that AMD will be revealing more information about Jaguar at the end of August.

Contact Us for News Tips, Corrections and Feedback

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Douglas Perry was a freelance writer for Tom's Hardware covering semiconductors, storage technology, quantum computing, and processor power delivery. He has authored several books and is currently an editor for The Oregonian/OregonLive.

-

silverblue AVX is interesting in its own right, but BMI? As Bobcat had the same instruction set support as K10, I'd have thought it already supported POPCNT and LZCNT as well as SSE4a.Reply

Supporting SSE4.1 and 4.2 is a good move, but will it make for a far more complex core? -

BulkZerker In b4 "Not as fast as my core i7 with 16 gigs of ram and a $700 Nvidia that self destructs with the odd numbered beta drivers" comments.Reply

And yet another reason to hold off on purchasing another laptop... again. -

opmopadop silverblue POPCNT and LZCNT Oh man, I havn't thought of Assembler in decades. Thanks for reminding an old programmer about the good times. Now to read up on the SSE4.1 ops for an asm fix.Reply -

danwat1234 chromonoidi hope this chip turns out to be good and not like bulldozerJaguar is a low powered x86 CPU or APU for tablets.Reply -

blazorthon silverblueAVX is interesting in its own right, but BMI? As Bobcat had the same instruction set support as K10, I'd have thought it already supported POPCNT and LZCNT as well as SSE4a.Supporting SSE4.1 and 4.2 is a good move, but will it make for a far more complex core?Reply

Trinity already supports SSE 4.1, SSE 4.2, SSSE3, and probably AVX, but I don't know if it supports BMI. Excluding BMI, I also know that Bulldozer supports all of these and that it might support BMI. I'd have to look up BMI support to know that one for sure. -

blazorthon otacon72low-price and low-power and low performance mobile processorReply

It's not like there is such thing as a high performance, very low power and low price CPU, especially in mobile markets. -

silverblue blazorthonTrinity already supports SSE 4.1, SSE 4.2, SSSE3, and probably AVX, but I don't know if it supports BMI. Excluding BMI, I also know that Bulldozer supports all of these and that it might support BMI. I'd have to look up BMI support to know that one for sure.Bulldozer supports SSE4a so I'm very much interested in what these BMI instructions are; I can't find any reference to an instruction set. If AMD indeed have worked on one, it'd make a lot of sense to implement it into the Bulldozer design especially if they're sticking with starving their cores for work.Reply -

ashinms I've heard speculation of a modular architecture, too. Xbit labs listed their reasons for believing this on their article. Reason being is that AVX requires two 128 bit or one 256 bit FPU. Bulldozer accomplishes AVX through one 256 bit "flex" FPU that is really more like two glued together. It's hard to imagine a mobile processor with a massive 256 bit FPU, but if two cores with one 128 bit each worked together at a modular level, the thinking goes, this could be accomplished much easier and with fewer transistors. Also, modifications have been made to allow addressing of upwards of 2MB of L2 cache, much higher than bobcat. This could point to a shared L2 cache, like in bulldozer.Reply