AMD's Bulldozer: More Design Details Surface

AMD has released new documents outlining the architecture for its upcoming Bulldozer release.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

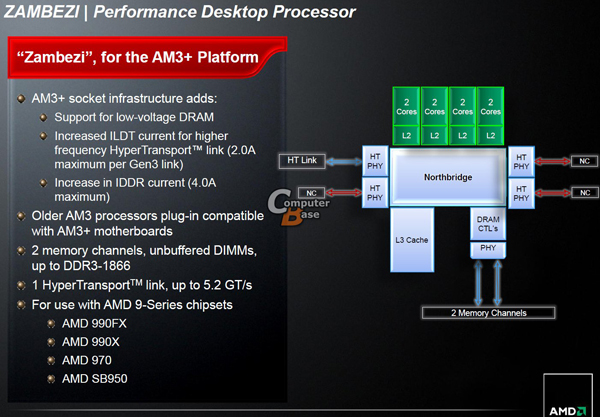

AMD's Bulldozer is one of the most highly-anticipated CPU architectures in recent memory. For those who are eager for more info on this new processor design, some new slides outlining Zambezi for the Socket AM3+ platform recently surfaced.

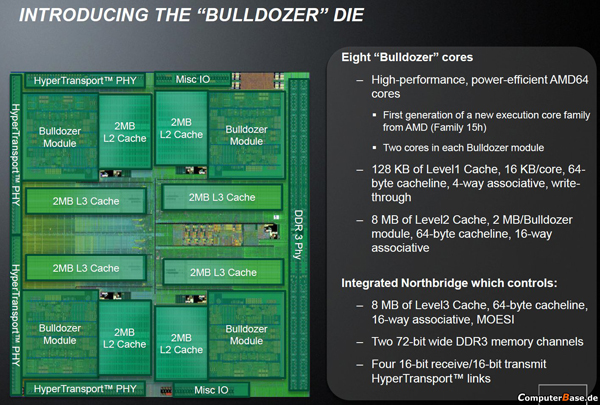

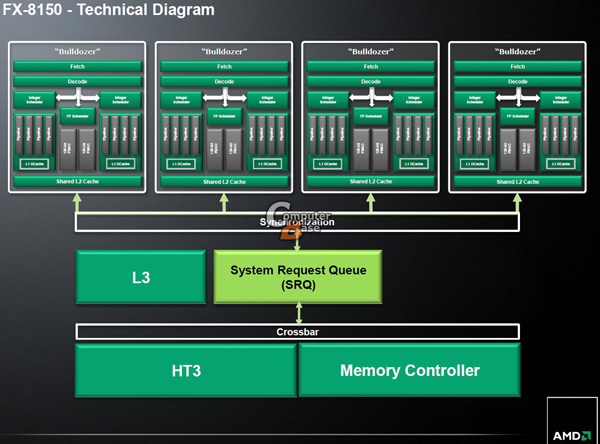

Breaking down the eight-core "Bulldozer" die, we find four modules that are each composed of two cores. Each module packs 2 MB L2 cache for a total of 8 MB. The is also an integrated Northbridge that contains 8 MB of L3 cache, two 72-bit DDR3 memory channels and four 16-bit receive/16-bit transmit HyperTransport links.

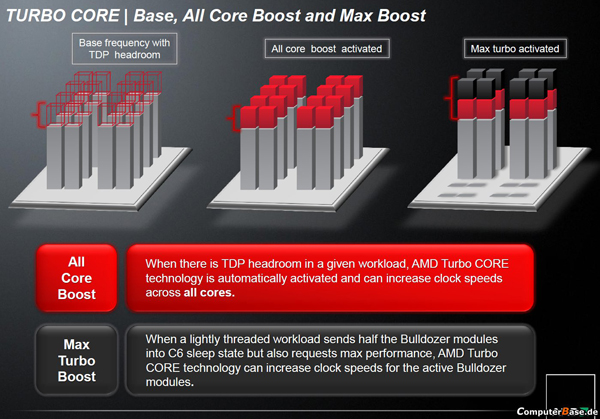

From the slides, we also see how Turbo Core will behave in Bulldozer. When the CPU's workload is within the TDP headroom, there is no core boost activity. When there is TDP headroom in given a workload, the Turbo Core kicks in and increases clock speed across the board. Conversely, when there is a lightly threaded workload, half the modules go into C6 sleep state, and the remaining cores get clocked up higher for better performance.

Article continues belowSee the full deck of slides at Computerbase.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

-

tacoslave This looks great and all but its going to supposedly be released on september 19th right? thats the new date given to us. Hopefully this wont be like their june, july, or august release dates or "end of 2010". Yup hopefully this is it. Hopefully it was a marketing decision so they could release it with there 7000 series gpu's. Then i can FINALLY upgradeReply -

acadia11 Taht doesn't sound like a release date to me! We don't care. AMD stop trying to be Apple.Reply -

ben850 Can't wait for this damn thing to be released!! Just hope it is a viable option by the time it comes out..Reply -

Thunderfox Bulldozer has been Dukeing us for years. Hopefully it has a better outcome. Ivy Bridge has been delayed til next year, so if AMD has its act together, they could make some headway this holiday season.Reply

If these things are mediocre chips released in homeopathic doses, AMD is in trouble. -

rantoc I hope this will be a worthy contender or surpases the current sandy bridges, otherwise we all are sure looking at higher CPU prices with the next intel refresh - both major cpu makers need to be competing or the prices will skyrocket and at the same time lower upgrades.Reply

We all remember intel back in the days before the Athlon came and started the competition that we today are enjoying. -

Martin9630 acadia11Taht doesn't sound like a release date to me! We don't care. AMD stop trying to be Apple.Reply

acadia11, nothing can be like Apple. -

killerclick This will be slower and use more power than Sandy Bridge. In addition, the die is too big so AMD will have slim margins. ALso, they will have to compete on price against Intel (because AMD has no other options), so this will probably be the last major CPU architecture AMD produces. Too bad, I've been buying AMD exclusively since the first Athlons came out.Reply -

ronch79 Does the Bulldozer include specialized circuitry for Turbo Core which will intelligently boost/shut down cores? Sandy Bridge had such mechanism, allowing it to take advantage of available TDP more efficiently and intelligently than the Phenom II X6, which just featured a reversed Cool and Quiet mechanism and probably doesn't really have a clue when to boost or shut down cores. It's also the reason why the Phenom II X6, according to reviews, doesn't spend too much time boosting its cores.Reply