Intel Demonstrates 10nm 116 Gbps Transceiver Test Chip on Agilex-I FPGA

Intel demonstrated 116G transceiver on 10nm.

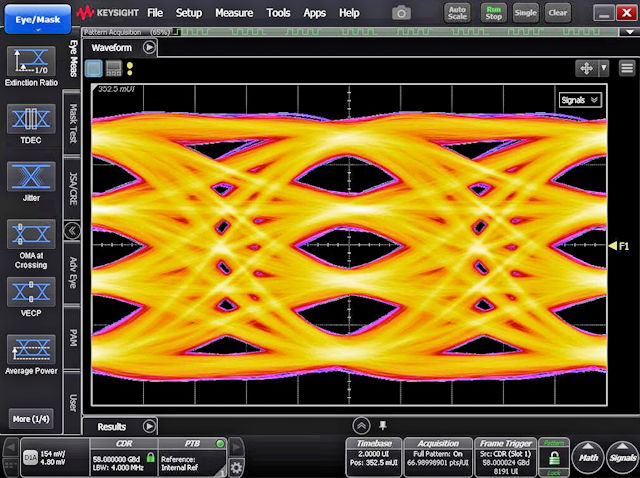

Intel on Monday demonstrated a long-reach transceiver test chip operating at 116 Gbps with PAM4 modulation and built on its 10nm process. It complies with the specification for 112G PAM4 transceivers and will be used in next year's Agilex-I series of FPGAs.

Intel said the test chip’s 116 Gbps operation demonstrates the design’s added margin compared to the 112G standard. It supports existing 100, 200 and 400 Gigabit Ethernet (GbE) standards and can also support emerging protocols and forward error-correction (FEC) standards, according to Intel.

- What Is an FPGA? A basic definition

- AMD Partner Summit delayed over coronavirus

In the demonstration, the transceiver chip’s transmitter sent a 116 Gbps data pattern to a receiver on the same chip through interconnect and external cabling, which represented a total insertion loss of greater than 35dB from BGA ball to BGA ball on the chip. However, Intel said it exceeded the CEI-112G-LR-PAM4 specification’s raw bit error ratio (BER) requirement by almost three orders of magnitude, even at 116 Gbps.

The transceiver’s architecture will be incorporated in the 2021 Agilex-I series along with a hardened up to 400GbE protocol stack.

Xilinx today unveiled its Versal Premium ACAP with 112G transceiver support.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.