The P6600 Is Imagination's First High-Performance 64-Bit CPU With OmniShield Support

In the past few years, we've seen rising demand for 64-bit mobile CPUs, as smartphones and tablets become more PC-like in terms of the performance they provide. We've seen 64-bit mobile CPUs from ARM chip makers and Intel, and today, Imagination launched its own MIPS64 mobile CPU design, called the P6600. Imagination also announced two new mid-range M6200 and M6250 CPUs.

The 64-bit P6600 is the next-generation CPU core from Imagination, and the successor to the 32-bit P5600. The new core is based on the MIPS64 Release 6 architecture, and it will target a broad range of applications, including mobile, but also home entertainment, networking, HPC, and industrial and embedded computing.

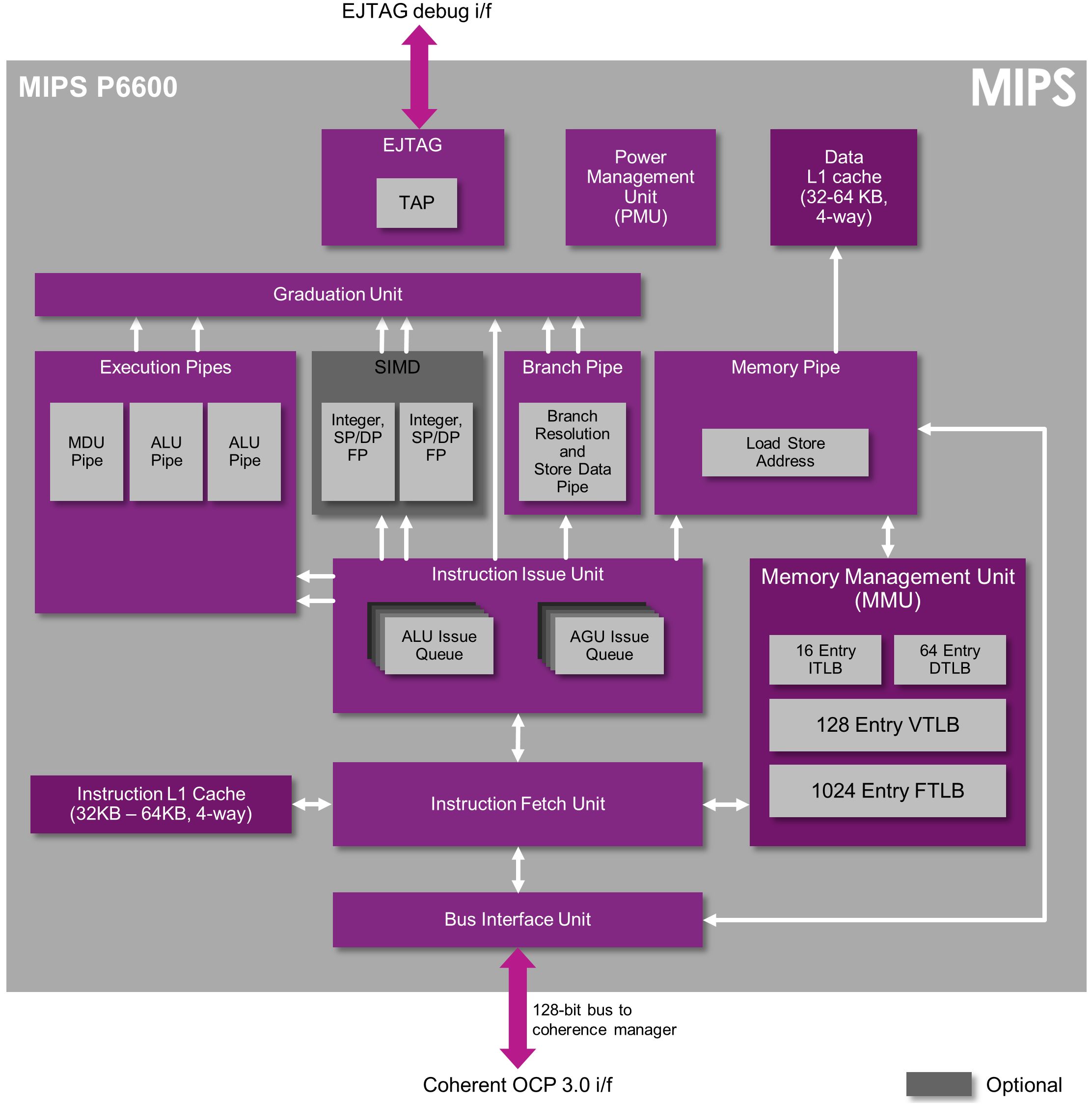

The P6600 is a high-performance core that combines a multi-issue 16-stage pipeline and out-of-order execution to deliver high computational throughput for modern mobile applications. Imagination also claimed that the P6600 includes "best-in-class branch prediction" and a load/store instruction bonding mechanism, which provide a "clear boost in real-world workloads" while keeping die size and power consumption low.

The P6600 is OmniShield-ready, while supporting more than twice as many (15) guest operating systems as its predecessor, the P5600. The guest operating systems can all run simultaneously in "fully isolated and trusted environments."

This is one of the features that sets Imagination's CPUs apart from the competition, as security starts to play a bigger role in mobile, with billions of users owning a smartphone, but also in IoT, the automotive industry, and so on.

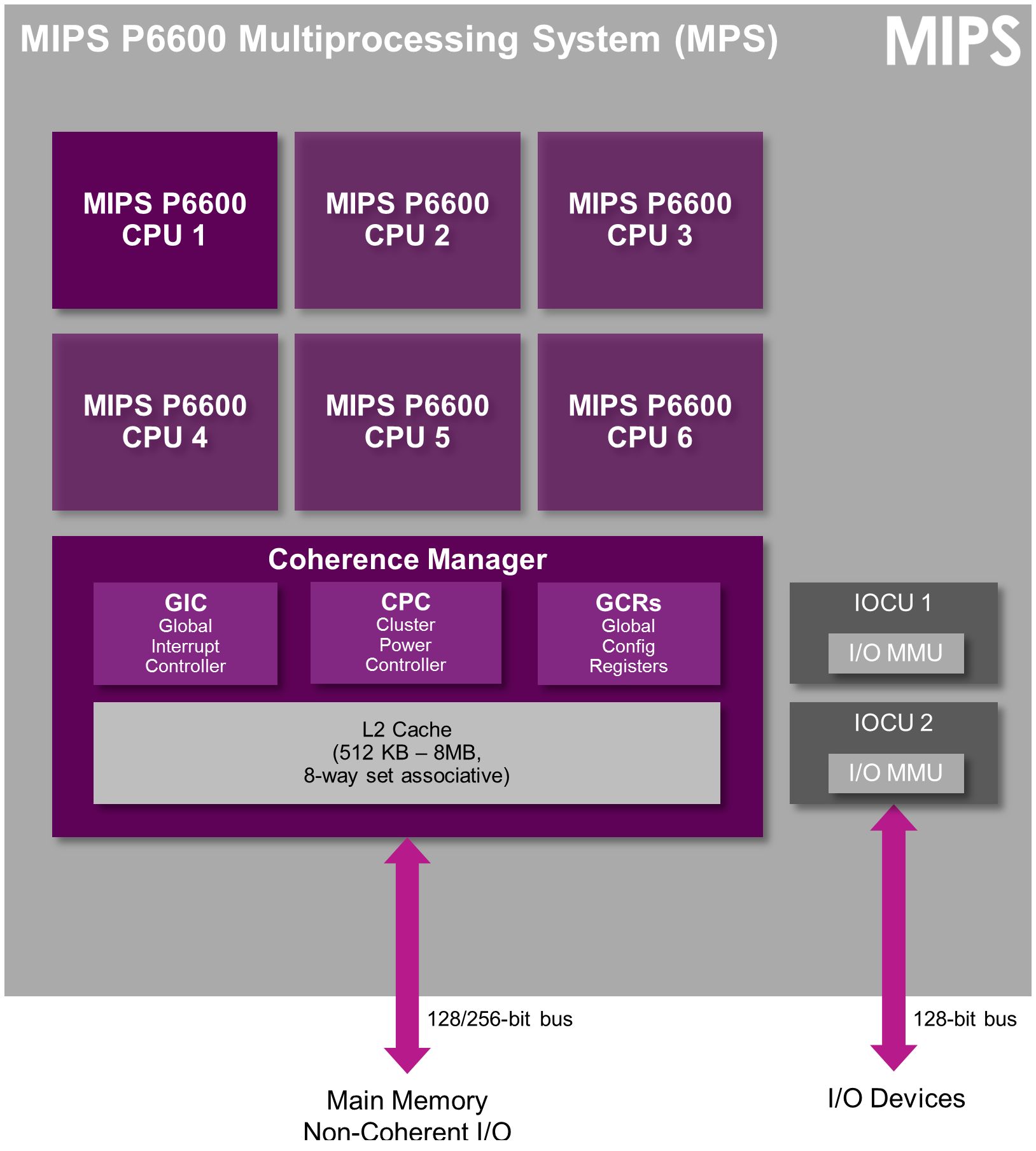

System builders can include up to six P6600 cores in their designs. Imagination's new chip comes with a SIMD engine, which is utilized for fast media acceleration such as VP9 decoding.

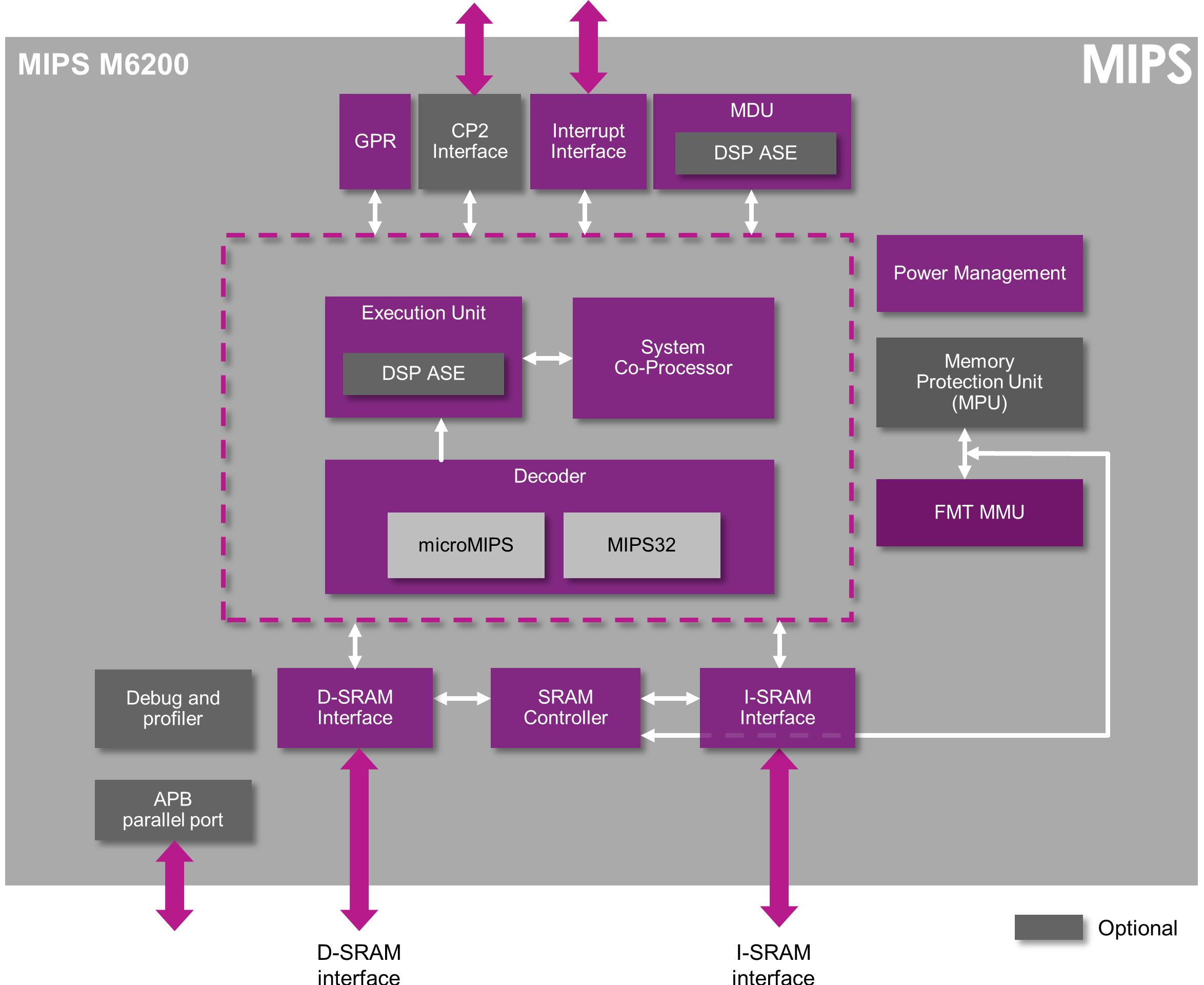

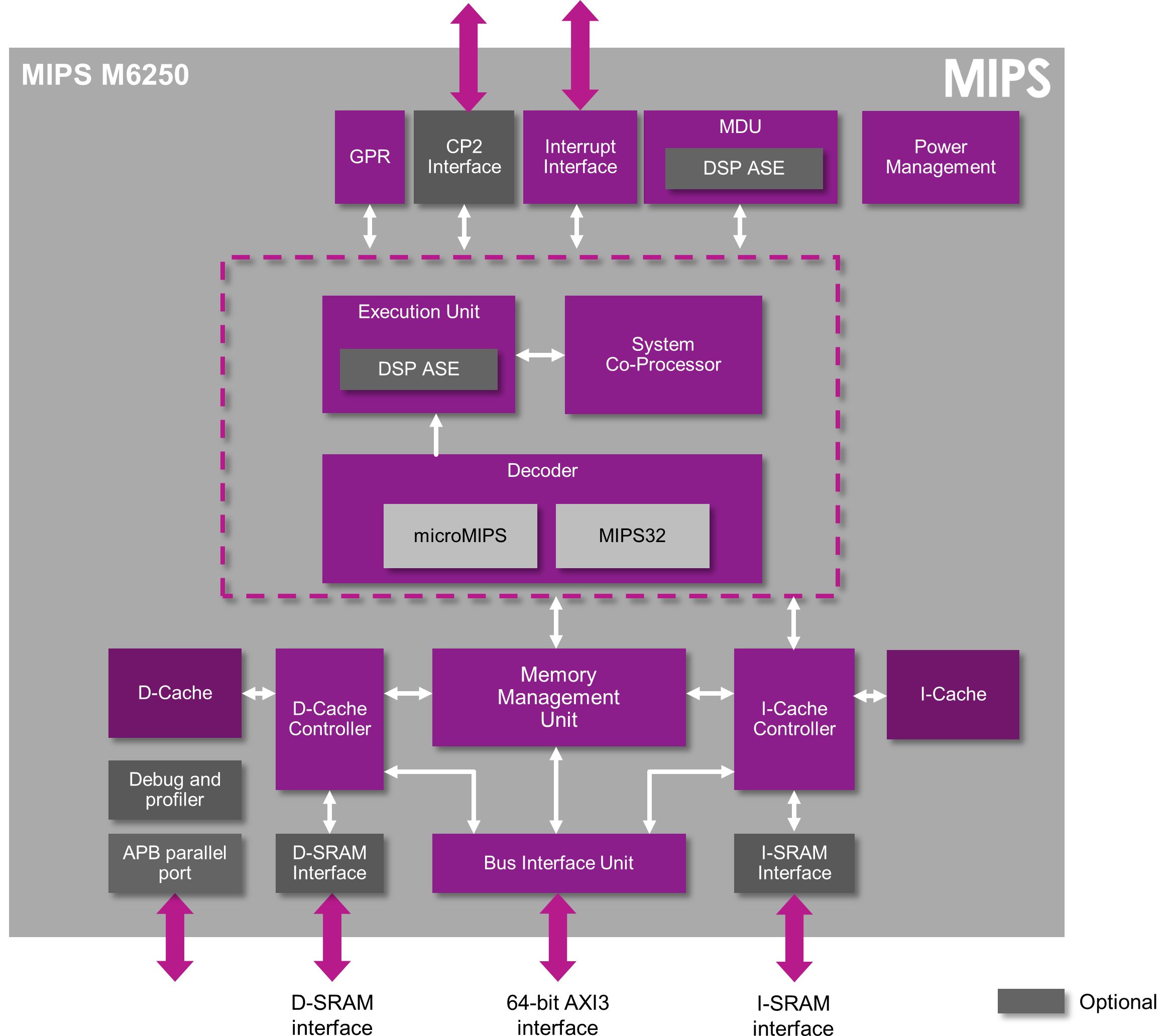

The company also introduced the M6200 and M6250, which have 30 percent higher clock speeds compared to their predecessors, the microAptiv UC and UP. They both also include:

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Tightly coupled memory (TCM) for high-performance applicationsAn interrupt controller supporting up to 256 interruptsThe MIPS DSP Module Revision 3 as a configurable option, providing a high level of digital signal processing capabilities and SIMD support.ECC and parity on instruction and data memories as a configurable option for increased reliabilityA new APB interface enabling JTAG, multicore and mixed core debugging

The new M-class CPU cores have 6-stage pipeline designs and are built on the MIPS32 Release 6 architecture. They also include support for the microMIPS32 ISA, which contains a set of optimized 16-bit and 32-bit instructions that significantly reduce the code size.

The M6200 CPU targets mainly the embedded market and will run a real-time operating system, while the M6250 will be able to run full Linux distros.

The M6250 comes with a high-speed 64-bit AXI bus interface, a Memory Management Unit (MMU), data and instruction cache controllers, and support for eXtended Memory Addressing (XPA) to 40-bit physical address space (up to 1 TB of system memory).

Imagination said that it will remain committed to expanding its range of CPUs in the future, based on Release 6 of its MIPS architecture, on which cores such as the I6400, M6200, M6250 and the P6600 have already been designed. However, it will be up to chip makers and OEMs to want to adopt MIPS CPUs in a greater number of devices before most consumers can see them on the market as a real alternative to ARM-based and x86-based chips.

______________________________________________________________________

Lucian Armasu joined Tom’s Hardware in early 2014. He writes news stories on mobile, chipsets, security, privacy, and anything else that might be of interest to him from the technology world. Outside of Tom’s Hardware, he dreams of becoming an entrepreneur.

You can follow him at @lucian_armasu. Follow us on Facebook, Google+, RSS, Twitter and YouTube.

Lucian Armasu is a Contributing Writer for Tom's Hardware US. He covers software news and the issues surrounding privacy and security.

-

g00ey It's kind of saddening when I hear young people saying the Bill Gates or Steve Jobs are the innovators of the PC while being totally ignorant to the techonogical development that took place in the '80s and the '90s in particular.Reply

Back in the '90s, the absolute state of the art of computers came from Silicon Graphics with their machines running on MIPS CPUs. They were found on state-of-the art workstations such as Crimson, Indigo2, or Indy. If you wanted something bigger there were products in the SGI Onyx series or SGI Challenge. These products costed upwards millions of dollars. They were competing with SPARC products and IBM POWER mainframes while the average consumer were fiddling around with bleeping monochrome terminals on shitty x86 hardware.

It's funny how such hardware has found a place in cheap mobile applications today. Even the PowerPC/Freescale CPUs that used to be in powerMacs are now commonly found in setop boxes and embedded systems. Wonder what happened to the DecAlpha CPUs, a series of high-end CPUs that were commonly used to render computer graphics for TV and movies.

Now these companies are much more interesting than a sloppy BIOS manufacturer like American Megatrends. -

therealduckofdeath It's also funny to see young people today thinking the x86 hardware today works the same way as it did 20 years ago. All hardware evolves, neither of the platforms is neither true x86 or MIPS based. The reason x86 killed MIPS is because Intel were smarter in designing really scalable hardware and they did that a long time ago.Reply -

g00ey Smarter with designing scalable hardware? I don't think so! Intel had a larger customer base = more money for research and development and therefore they managed to compete with more price efficient products. This was coming from economies of scale and not because they were better. In fact, the Intel hardware with their 32bit CISC architecture was inferior to e.g. MIPS and SPARC that used 64bit RISC architectures with better pipelining and much faster bus/memory speeds. But Intel hardware was also a lot cheaper.Reply

The Intel stuff was shit, but with the help of a lot of R&D they managed to overcome a lot of those hurdles. I'm not sure exactly when but they did a total redesign "under the hood" and now those x86 instructions are merely a layer on top of an internal instruction set of what they call "microcode". But this instruction set has been updated with quite a lot of extensions that render many of the old instructions redundant and obsolete. I think we are at AVX2.0 now. So yes, I'm aware of their redesign...

The current instruction set is a performance hurdle for Intel still to this day, how big a hurdle it is is hard to tell. I think one shouldn't rule out the possibility that one day the x86/x64 might get replaced by more efficient architectures in the future. The ARM CPU can gain market share, I think it is still inferior to Intel in server environments but it is developing as well and future ARM64 technologies may come with what is required for server environments. There is a lot of talk about power efficient ARM-based servers right now. The thing is that Intel has so far not yet managed to penetrate the mobile market and that could one day spell the end of Intel's architectures. -

therealduckofdeath Intel does redundancy at a fraction of the cost of any other platform. You can whine about made up things like "microcode" and instructions. The reality is, Intel did everything right and now MIPS are once again trying to play catchup.Reply

I'll just rest my case with asking you what the server hardware market looked like 20 years ago and what it looks like today. -

alidan ReplyIntel does redundancy at a fraction of the cost of any other platform. You can whine about made up things like "microcode" and instructions. The reality is, Intel did everything right and now MIPS are once again trying to play catchup.

I'll just rest my case with asking you what the server hardware market looked like 20 years ago and what it looks like today.

if i remember right there are some workloads that those old as dirt sg computers do faster than todays, i honestly forget what as it was quite a while ago that i was looking at that. -

therealduckofdeath Reply

Yeah, you remember it wrong. A current smartphone outperforms an early 90s super computer. :)16942241 said:Intel does redundancy at a fraction of the cost of any other platform. You can whine about made up things like "microcode" and instructions. The reality is, Intel did everything right and now MIPS are once again trying to play catchup.

I'll just rest my case with asking you what the server hardware market looked like 20 years ago and what it looks like today.

if i remember right there are some workloads that those old as dirt sg computers do faster than todays, i honestly forget what as it was quite a while ago that i was looking at that.