Papermaster: AMD's 3rd-Gen Ryzen Core Complex Design Won’t Require New Optimizations

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

AMD demoed its 7nm third-gen Ryzen chips and new 7nm Radeon VI gaming GPU at CES, but as with many new product announcements, we weren't given many details beyond the demos.

Luckily, we caught up with AMD Chief Technology Officer Mark Papermaster after the event. As expected, Papermaster couldn't share many of the fine-grained details we're searching for, but he did give us some insight into the basic design of the third-gen Ryzen processors and assured us that existing software will work fine with the new design.

AMD's first-gen Ryzen processors landed with a revolutionary new core design that initially led to lower-than-expected performance in some applications. Latency-sensitive applications (like games) suffered the most, but AMD made a concerted effort to arm software developers with the knowledge to tailor their code for the unique Zen microarchitecture, largely correcting the issue with the mainstream desktop chips. We asked Papermaster if those optimizations would carry over to the new third-gen Ryzen products that appear to have a more unique architecture.

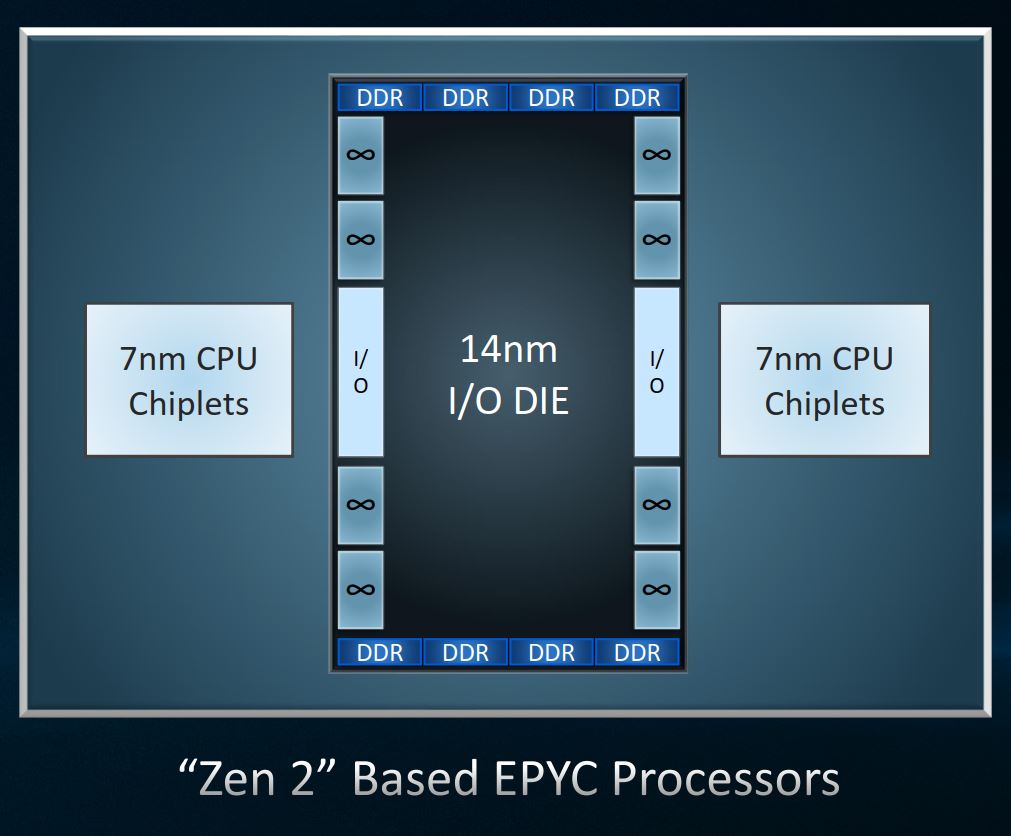

Article continues below"The optimization that we worked with the industry as we first rolled out Ryzen was our core complex," Papermaster said, "We very successfully worked across the OS, with Windows and Linux, so there is a recognition of AMD’s core complex, and so you can really have your workloads leverage that organization. As we go forward into this next-generation with Zen 2-based products, we actually just make it easier because as you have cores going into a common I/O die, it is the same core complex approach that we had before, and you actually just have a very centralized path. In our server implementation all the way through the Ryzen implementation we showed today, it adds no complication whatsoever for the software providers. All the work we did with first-gen Ryzen will carry right over. All those optimizations carry right over."

Papermaster's comments confirm that the company is still utilizing a core complex approach for the compute die, and although the company could have made adjustments to the architecture, his statement could give us a clearer image of the new design.

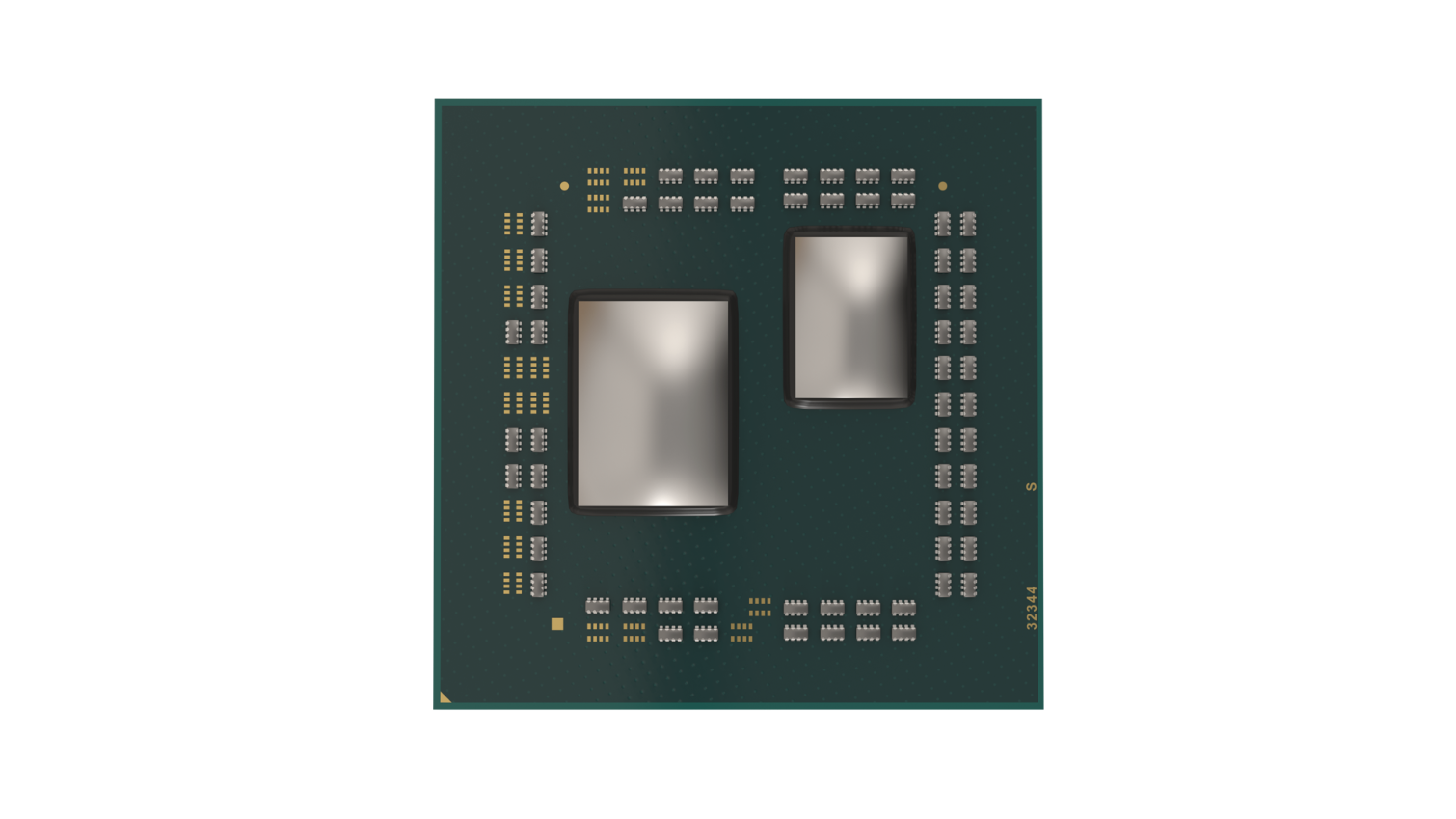

Third-Gen Ryzen Chip

As a quick refresher, the third-generation Ryzen processor comes with a multi-chiplet arrangement. This modular design consists of an eight-core 7nm chiplet (upper right) connected to a 14nm I/O die (left). The I/O die contains the memory controllers, Infinity Fabric links, and I/O connections. Aside from support for PCIe 4.0, AMD is still keeping details about the chips' resources close to the chest.

AMD is now using a second-gen Infinity Fabric to connect the compute die to the I/O die. This design helps AMD keep the areas of the chip that don’t scale well, like the memory controllers and I/O, on a proven and mature node, while also leveraging the performance, density and economic advantages of the 7nm node for the important compute functions.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

We know that the new 7nm Ryzen compute die has eight cores, but it is logical to assume that it will be optimized to remove the resources that have moved to the new I/O die.

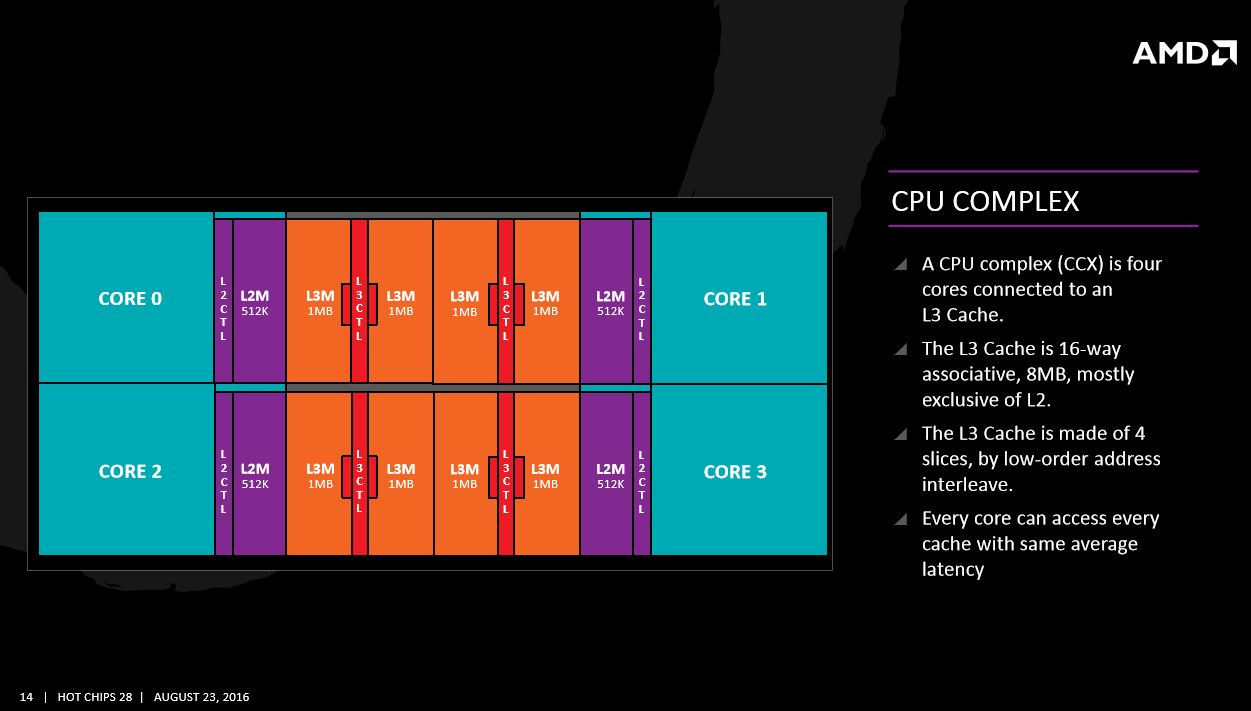

Here we see the current arrangement of AMD's Core Complex. AMD arranged the CPU complex (CCX) into four cores connected to a centralized 8MB L3 cache split into four slices. Each core also has a private 512KB L2 cache. AMD connects multiple CCXs together to create higher chips with higher core counts, such as the 8-core/16-thread (2 x CCX) first-gen Ryzen processors.

It's possible that AMD has increased the capacity of some of the caches, such as L1, L2, and L3, on the third-gen Ryzen chips, and/or adjusted the associativity of the caches, but we'll have to wait for further information.

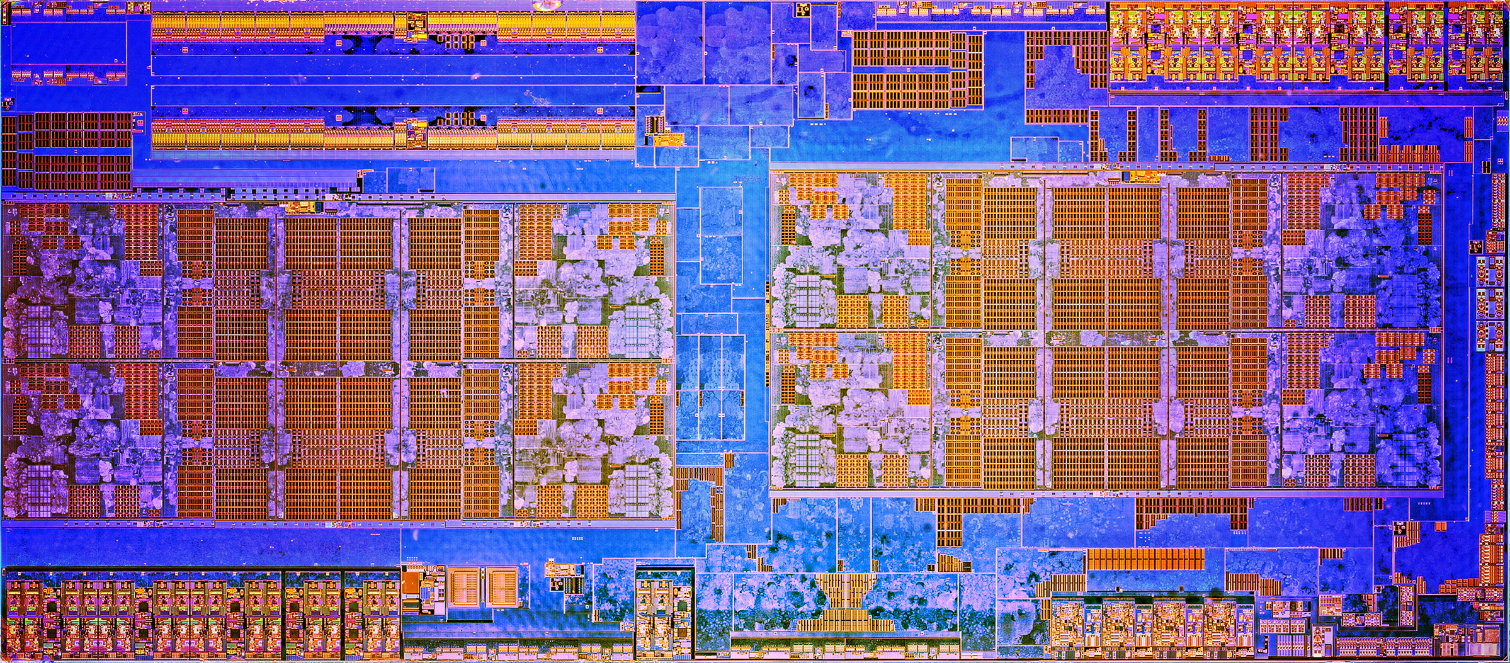

Zooming out, here we can see how AMD currently arranges the two Core Complexes onto a single Zeppelin die. Two CCXes (orange blocks in the center) come together to create an eight-core Zeppelin die, and they communicate via AMD’s Infinity Fabric interconnect. The CCXes also share the same memory controller. This is basically two quad-core CPUs talking to each other over the dedicated Infinity Fabric interconnect that also handles northbridge and PCIe traffic.

In the image above we can see a block diagram of the first-gen die, courtesy of WikiChip. With third-gen Ryzen, the DDR4 memory controllers, USB, SATA, and platform I/O units have now all migrated to the I/O die. Those adjustments should provide AMD with more density benefits on its small 7nm compute die as more of its area can be dedicated specifically to the eight cores. However, it remains to be seen if AMD will still use two separate four-core Core Complexes inside a single eight-core die, or if it will expand the core complex design to eight cores. AMD hasn't listed PCIe resources on its I/O die, implying those controllers could also remain on the eight-core compute die.

We also know that at least some form of the IFOP (Infinity Fabric On-Package) SerDes will have to be present on the new die, as these units facilitate communication with other die. Papermaster also told us that the company's next-generation Infinity Fabric would have improvements to its protocol and efficiency, with bandwidth and bandwidth-per-watt being key focus areas.

It's encouraging to hear that AMD's next round of Ryzen chips will not need specific new software enhancements to accommodate the design, as that was a key concern when the first-gen chips arrived. AMD has said that it will release the new third-gen Ryzen processors in mid-2019, which lines up nicely with Computex. As with AMD's previous big launches, we expect more information to come to light slowly in the intervening months as the company builds the hype for its newest round of processors.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

jpe1701 I'm like a kid waiting for Christmas. Hope they knock it out of the park with this one. Competition is good for all of us consumers.Reply -

Gillerer Hint: PCIe *is* I/O.Reply

I can think of at least two reasons why they didn't specify "PCIe" instead of the more generic "I/O":

1) There is also other I/O in addition to PCIe: earlier Ryzen processors had on-CPU USB and SATA, for instance;

2) The lanes can operate flexibly in either PCIe or Infinity Fabric mode (1st gen EPYC on dual-socket systems used half the PCIe lanes in IF mode to connect the CPUs and half were left in PCIe mode). Maybe AMD has some plans to expand on the Infinity Fabric usage beyond dual-socket and intra-CPU? -

redgarl Reply21703895 said:I'm like a kid waiting for Christmas. Hope they knock it out of the park with this one. Competition is good for all of us consumers.

So they can buy the competition (Intel/Nvidia) at a lower price?

No, I want the better product to sell, end of story, and we know which one is going to be the best product.

Things like MSI CEO interview is disturbing at best and I fear that Intel is going back to their good old tactics of buying OEM and blocking the superior product until an anti-competitive lawsuit surface which is going to last 10 years while the damage will be done. -

redgarl Reply21704939 said:Hint: PCIe *is* I/O.

I can think of at least two reasons why they didn't specify "PCIe" instead of the more generic "I/O":

1) There is also other I/O in addition to PCIe: earlier Ryzen processors had on-CPU USB and SATA, for instance;

2) The lanes can operate flexibly in either PCIe or Infinity Fabric mode (1st gen EPYC on dual-socket systems used half the PCIe lanes in IF mode to connect the CPUs and half were left in PCIe mode). Maybe AMD has some plans to expand on the Infinity Fabric usage beyond dual-socket and intra-CPU?

Multi-GPU for compute and ML. Mentioned a long time ago. -

Gillerer Reply21705017 said:21704939 said:... Maybe AMD has some plans to expand on the Infinity Fabric usage beyond dual-socket and intra-CPU?

Multi-GPU for compute and ML. Mentioned a long time ago.

I should have prefaced "...Infinity Fabric usage" with "CPU...", since that's what I meant - and was talking about. -

Olle P Has it really been confirmed yet that the I/O die for Ryzen is 14nm?Reply

(I've seen no official quote from AMD.) -

irish_adam Reply21705405 said:Has it really been confirmed yet that the I/O die for Ryzen is 14nm?

(I've seen no official quote from AMD.)

AMD Announces 64-Core 7nm Rome CPUs, 7nm MI60 GPUs, and Zen 4

They told us when they detailed Rome back in November