TSMC and Partners Develop Key Feature for Sub 1nm Process Technology

TSMC's 1nm process begins to take shape.

Update 5/21/2020 8:45am PT: TSMC has reached out and asked to clarify that the findings by the researchers may not necessarily be used in commercial chip production. The statement reads as follows:

The article “Ultralow contact resistance between semimetal and monolayer semiconductors”, published in the journal Nature is an exciting finding for the application of 2D materials to semiconductors, but it does not necessarily mean that this research will be applied by TSMC in future technology nodes. TSMC provided support to the work described in this article performed by researchers from MIT and National Taiwan University, and it is an excellent example of our collaboration with global leading academic institutions. However, all TSMC technologies beyond the 3nm node are in the pathfinding or exploratory research stage at this time.”

Original Article:

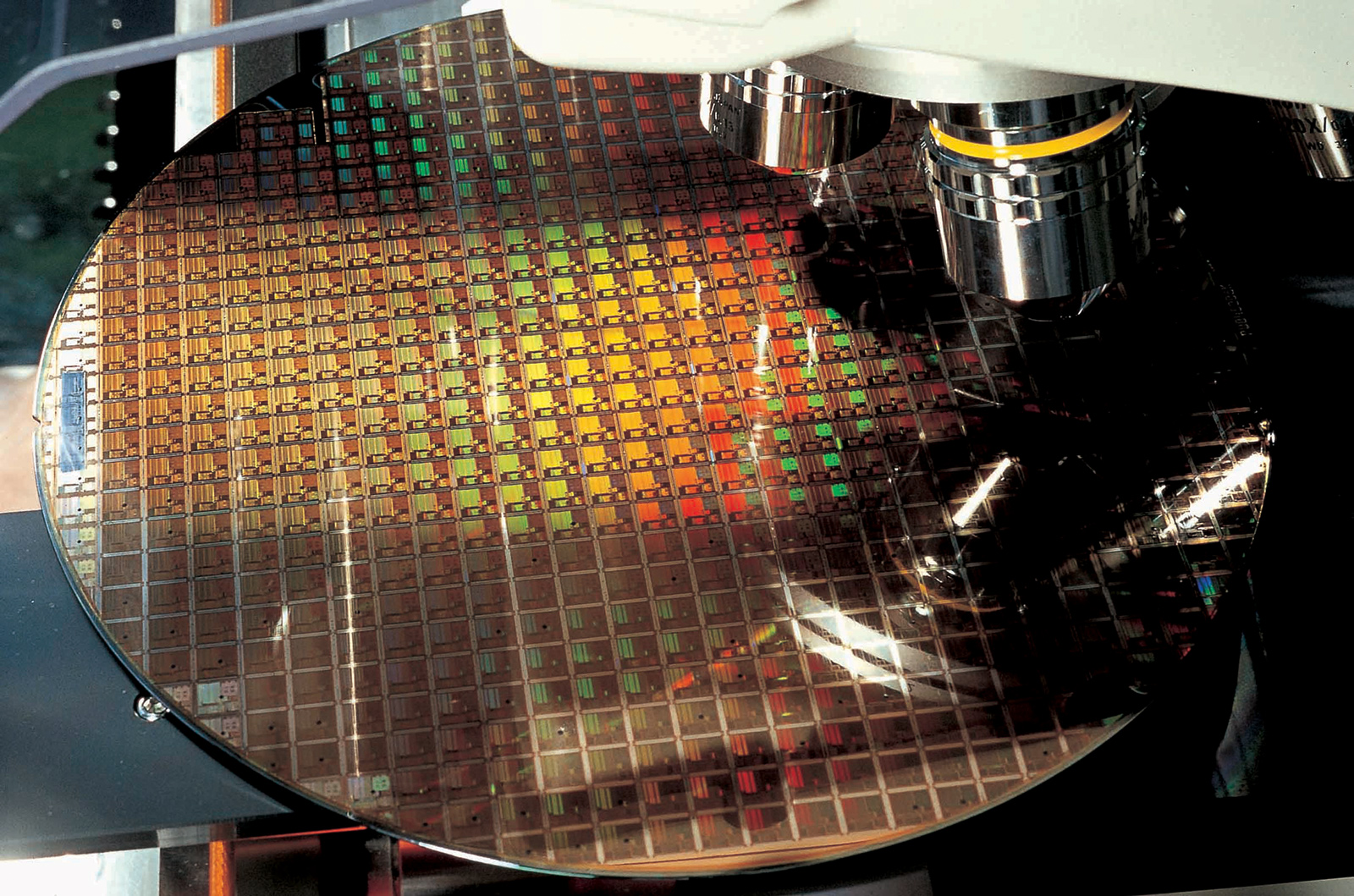

According to a publication by TSMC, NTU, and MIT in Nature (noticed by Verdict), Taiwan Semiconductor Manufacturing Co. (TSMC) and its research partners from the National University of Taiwan (NTU) and Massachusetts Institute of Technology (MIT) have said that they have developed material that will be used for transistor contact electrodes with an upcoming 1nm fabrication process.

Every new process technology brings new challenges and in this case the key challenges are finding the right transistor structure as well as the right transistor materials. Meanwhile, transistor contacts that bring power to transistors are crucial for their performance. Further miniaturization of the semiconductor process technologies increases resistance at contacts, which limits their performance. Therefore, TSMC and other chip makers need to find a contact material that has a very low resistance, can transfer high currents, and can be used for volume production.

The publication indicates that usage of semi-metal bismuth (Bi) as the transistor's contact electrode can greatly reduce the resistance and increase the current. TSMC currently uses tungsten interconnects (made using selective tungsten deposition process), whereas Intel uses cobalt interconnects. Both have their advantages and both require specific factory tools.

In a bid to use semi-metal bismuth (Bi) as transistor's contact electrode, researchers had to use a helium ion beam (HIB) lithography system and design an 'easy deposition process.' This 'process' was only used on an R&D production line, so it is not quite ready for mass production.

Right now, TSMC's 1nm node is in path-finding mode and the foundry is experimenting with various options. TSMC's 1nm fabrication process will not be used for high volume manufacturing for years to come and it is not guaranteed that semi-metal bismuth will indeed be used at all. Nonetheless, it is evident that TSMC is already working on its 1nm technology.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

InvalidError At this scale, they could start naming processes based on how many substrate atoms wide stuff is.Reply -

Asakha ReplyInvalidError said:At this scale, they could start naming processes based on how many substrate atoms wide stuff is.

Since silicon atoms are about 0,2nm wide, this 1nm process would be a 5 atoms process ! -

techrabbit2015 For all of you excited about how many atoms wide these are, this isn't how these companies are designating "1nm" or even "5nm" at this stage. It is no longer calculated like that. The transistors are actually much bigger.Reply -

InvalidError Reply

Nobody wrote anything about transistors.techrabbit2015 said:For all of you excited about how many atoms wide these are, this isn't how these companies are designating "1nm" or even "5nm" at this stage. It is no longer calculated like that. The transistors are actually much bigger.

The "size" of processes has been about an unspecified feature's size which varies between manufacturers that isn't necessarily the smallest part of the design for a long time and a "feature" is something like minimum trace-to-trace pitch, FET channel width, gate insulation thickness, etc., not entire transistors.

Doesn't change the fact that at 1nm, most dimensions can indeed be described by single-digit atom count. We're almost at the point where atomic decay of the materials CPUs are made from could become enough to cause issues: can't afford too many of a 1nmsq channel's ~25 atoms cross-section changing into anything else. -

Solandri Reply

The nm refers to the size of certain structures used to make transistors. Unfortunately each company uses a different structure as a reference, so you can't compare the nm number between companies.techrabbit2015 said:For all of you excited about how many atoms wide these are, this isn't how these companies are designating "1nm" or even "5nm" at this stage. It is no longer calculated like that. The transistors are actually much bigger.

TSMC 12nm is about 29 million transistors / mm^2

Intel 14 nm is about 35 MT / mm^2

TSMC 10nm is about 52 MT / mm^2

Intel 10nm is about equal to TSMC 7nm (both around 100-110 MT / mm^2).

TSMC 5nm is about 173 MT/mm^2.

Intel 7nm (if it ever gets here) is estimated to be at about 225-250 MT / mm^2,

TSMC 3nm is supposed to be 70% higher than their 5nm, which would be about 290 MT/mm^2.From what I gather, a silicon atom is about 0.132 nm across. So 1 mm^2 = 7.5 million x 7.5 million silicon atoms. Or about 325,000 atoms (surface area) per transistor. Or 570x570 atoms per transistor if they were square (less probably after accounting for dead space between transistors).

If you compare transistor density to process, the relationship is close to (but slightly less than) the square. So if you figure a 1 nm process results in about 25% the linear density of their 5 nm process, then you get transistors about 140 x 140 atoms across. -

escksu ReplyInvalidError said:Nobody wrote anything about transistors.

The "size" of processes has been about an unspecified feature's size which varies between manufacturers that isn't necessarily the smallest part of the design for a long time and a "feature" is something like minimum trace-to-trace pitch, FET channel width, gate insulation thickness, etc., not entire transistors.

Doesn't change the fact that at 1nm, most dimensions can indeed be described by single-digit atom count. We're almost at the point where atomic decay of the materials CPUs are made from could become enough to cause issues: can't afford too many of a 1nmsq channel's ~25 atoms cross-section changing into anything else.

From what i see, its probably going to be gaafet cross section. -

InvalidError Reply

That wouldn't be much of a metric on its own since the width of FET channels depends on the total current the FET needs to pass which can itself be divided between multiple vertically and horizontally stacked parallel channels sharing an all-around gate.escksu said:From what i see, its probably going to be gaafet cross section. -

gg83 Reply

Awesome!Solandri said:The nm refers to the size of certain structures used to make transistors. Unfortunately each company uses a different structure as a reference, so you can't compare the nm number between companies.

TSMC 12nm is about 29 million transistors / mm^2

Intel 14 nm is about 35 MT / mm^2

TSMC 10nm is about 52 MT / mm^2

Intel 10nm is about equal to TSMC 7nm (both around 100-110 MT / mm^2).

TSMC 5nm is about 173 MT/mm^2.

Intel 7nm (if it ever gets here) is estimated to be at about 225-250 MT / mm^2,

TSMC 3nm is supposed to be 70% higher than their 5nm, which would be about 290 MT/mm^2.From what I gather, a silicon atom is about 0.132 nm across. So 1 mm^2 = 7.5 million x 7.5 million silicon atoms. Or about 325,000 atoms (surface area) per transistor. Or 570x570 atoms per transistor if they were square (less probably after accounting for dead space between transistors).

If you compare transistor density to process, the relationship is close to (but slightly less than) the square. So if you figure a 1 nm process results in about 25% the linear density of their 5 nm process, then you get transistors about 140 x 140 atoms across. -

neatep I remember reading years ago that it would be impossible to go below 3nm as electricity currents start to interfere with each other.Reply

Was this solved just by changing the alloys? Or was it actually only a theoretical issue and not a real world problem.