Core Ultra K prototype appears on CPU-Z, uses Intel 4 process node and hits 5 GHz, lacks AVX-512 support

Intel's new silicon comes on a B0 stepping.

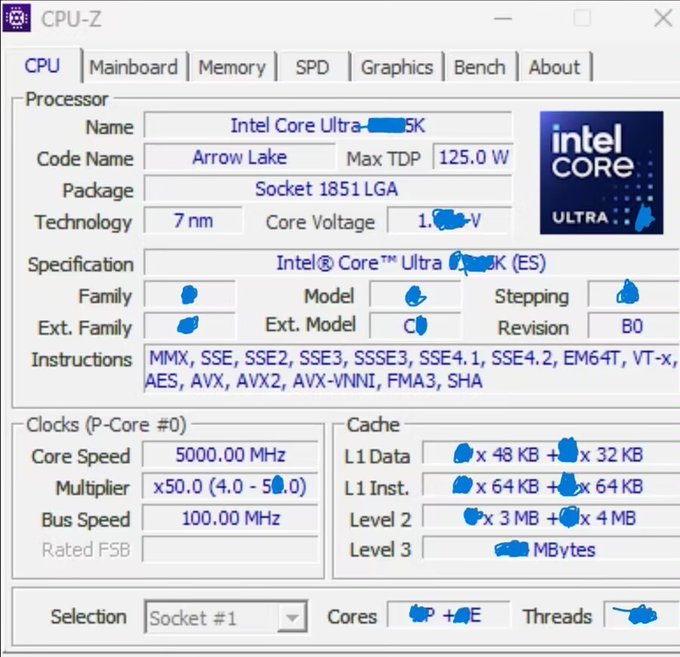

A mysterious Core Ultra K series engineering sample has made an appearance on CPU-Z. Алексей on X (Twitter) a screenshot of the mysterious part, with many of the critical system specifications blanked out to hide its true identity. Among the interesting findings is that the chip is listed with a 7nm node, denoting it uses the Intel 4 process, and lacks support for AVX-512.

The specs reveal that this particular engineering sample is made on the B0 revision of silicon and uses Intel's next-generation LGA 1851 socket. Multiplier specs show that the maximum boost clock is somewhere in the 5GHz range, similar to Intel's outgoing 13th and 14th Gen processors.

pic.twitter.com/59hZ91TxWrJuly 23, 2024

| Processor | Cores / Threads (P+E) | PBP (W) |

|---|---|---|

| Core i9-14900K | 24 / 32 (8+16) | 125 |

| Core Ultra 9 285K | 24 / 24 (8+16) | 125 |

| Core i7-14700K | 20 / 28 (8+12) | 125 |

| Core Ultra 7 265K | 20 / 20 (8 + 12) | 125 |

| Core i5-14600K | 14 / 20 (6+8) | 125 |

| Core Ultra 5 245K | 14 / 14 (6 + 8) | 125 |

The model in question could be any of the three K SKU parts we know of right now. Previous leaks have unveiled three unlocked K-series variants for Arrow Lake-S: the flagship Core Ultra 9 285K, Core Ultra 7 265K, and Core Ultra 5 245 K. The Core Ultra 9 285K will purportedly have 8 Lion Cove P-cores and 16 Skymont E-cores, Core Ultra 7 285K will have 8 P-cores and 12 E-cores, and Core Ultra 5 245K will come with 6 P-cores and 8 E-cores.

Article continues belowOne of the most interesting tidbits from the CPU-Z screenshot is the lack of hardware-accelerated AVX-512, as noted in the CPU-Z instructions entries. This little detail suggests that Intel is once again derailing AVX-512 for another generation, leaving AMD's competing Ryzen 9000 series processors as the sole models to support the full-fat AVX-512 acceleration units.

This is not the first time Intel has removed AVX-512 functionality from its hybrid CPUs. Intel began pulling AVX-512 support, starting with Alder Lake, due to complications that stemmed from Intel's decision to include AVX-512 support in its Golden Cove P-cores but remove it entirely from its Gracemount E-cores to save space.

The lack of AVX-512 support on the Gracemount cores forced Intel to completely remove AVX-512 support from Alder Lake CPUs altogether. However, the first batches of Alder Lake CPUs (and motherboard BIOS firmware) ironically allowed you to run AVX-512 instructions. The only caveat is that users had to disable the E-cores from the BIOS first for AVX-512 to work. Eventually, Intel culled this workaround entirely by first disabling AVX-512 enablement in firmware and then fusing it off physically on newer Alder Lake batches.

This trend continued to Raptor Lake/Raptor Lake Refresh, and now it appears to be making its way to Arrow Lake-S. This is pretty disappointing since AMD has enabled full 512-bit acceleration paths for AVX-512 with its Zen 5 and Zen 5c cores. The icing on the cake is that AMD can also run AVX-512 with minimal to no penalty to clock speed, which is a far cry from Intel's chips, which have had to reduce clock speeds when running AVX-512 instructions to prevent the CPUs from overheating.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Aaron Klotz is a contributing writer for Tom’s Hardware, covering news related to computer hardware such as CPUs, and graphics cards.

-

bit_user Reply

Intel killed AVX-512. In client CPUs, it's dead and not coming back. Server CPUs will continue to support it, as a matter of backwards compatibility, but Intel considers it a legacy feature.The article said:This little detail suggests that Intel is once again derailing AVX-512 for another generation, leaving AMD's competing Ryzen 9000 series processors as the sole models to support the full-fat AVX-512 acceleration units.

AVX10 is meant to replace it. Client CPUs will implement AVX10/256, which inherits AVX-512 functionality, but only supports 128-bit and 256-bit vector widths (AVX-512 supported these operand sizes, also). Server CPUs will implement AVX10 at 512-bit width (again, also supporting 128-bit and 256-bit operands), but this is referred to somewhat pejoratively, in Intel's AVX10 literature as a legacy thing.

Golden Cove and its Intel 7 process node largely solved that. Sapphire Rapids can run AVX-512 workloads with minimal clockspeed penalties and while staying inside their specified power envelop (which only allows up to 25% excursions above TDP and I assume only within the time window defined by the Tau parameter).The article said:... Intel's chips, which have had to reduce clock speeds when running AVX-512 instructions to prevent the CPUs from overheating.