Everything We Know About Intel's Skylake Platform

Intel's Skylake architecture and corresponding platform represent a huge evolution in connectivity, overclocking and, ultimately, system performance. This resource should help answer any questions you have about the company's current desktop PC design.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

HSIO Lanes And Connectivity

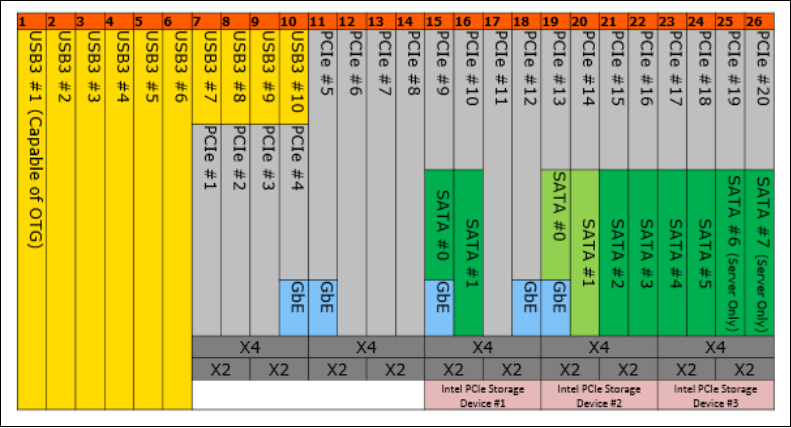

Intel has been using a similar technology to HSIO (high-speed I/O) lanes (Flex /IO on Haswell-based chipsets) to interface between add-ins for years. Compared to its Haswell- and Broadwell-based platforms, however, Skylake is even more reliant on this technology, which sometimes makes understanding the connectivity options of each chipset more confusing.

Nearly every connection between the PCH and another device uses HSIO lanes. The only major connections that don’t are the USB 2.0 ports and the link between DMI link between the CPU and PCH. All USB 3.0 ports, SATA interfaces and PCIe slots consume at least one HSIO lane.

For example, Z170 exposes a total of 26 HSIO lanes, six of which are consumed by six permanently-enabled USB 3.0 ports. So, the chipset ends up with 20 configurable HSIO lanes that can be assigned to other devices. Each SATA port uses an HSIO lane as well, unless it's connected through a third-party controller (though that controller would need at least one lane to communicate with the PCH). As you can see in the diagram, GbE controllers and PCIe-based SSDs also consume available HSIO lanes.

The confusion happens when you hear what the chipset can support. Yes, you can do up to 10 USB 3.0 ports, eight SATA 6Gb/s ports, 20 PCIe 3.0 lanes and gigabit Ethernet. But the platform can only handle some of those I/O options simultaneously.

| Skylake Chipsets (Real) PCIe Connectivity | |||

|---|---|---|---|

| Row 0 - Cell 0 | Max PCIe 3.0 Lanes | Max PCIe 3.0 Lanes If All USB, SATA & Single GbE In Use | DMI |

| Z170 | 20 | 9 | 3.0 |

| H170 | 16 | 7 | 3.0 |

| H110 | 6 (PCIe 2.0) | 6 (PCIe 2.0) | 2.0 |

| Q170 | 20 | 9 | 3.0 |

| Q150 | 10 | 5 | 3.0 |

| B150 | 8 | 5 | 3.0 |

| C236 | 20 | 7 | 3.0 |

| C232 | 8 | 5 | 3.0 |

The biggest issue is that the maximum number of PCIe 3.0 lanes on each chipset will likely never be exposed. In order to have 20 lanes configured, which is technically possible on Z170, Q170 and C236, you would have to give up all SATA-based storage, native GbE and USB 3.0 ports beyond the six hard-wired ones.

Motherboard manufacturers make the situation more difficult to explain by launched products with more physical connections than the PCH can support at any one time. Engineers make all of the I/O functional by tying multiple devices to a single HSIO lane. Devices that share a lane cannot function simultaneously. So, often, connecting one piece of hardware disables other ports or features elsewhere. And it doesn't help that board vendors don't make this well-known. Most of the spec sheets we've seen do spell out which connections share HSIO lanes, but it's sometimes hidden in fine print somewhere at the bottom. As a result, even enthusiasts get caught buying motherboards based on their connectivity options without realizing they can't all be used together.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: HSIO Lanes And Connectivity

Prev Page Skylake Workstation Chipsets Next Page Memory And Bandwidth-

Captainawzome Reply

Thanks! Sadly, this page does not explain the nuances of other factors such as overclocking potential, and the probability of getting a skylake CPU that overclocks to 4.6, 4.8, etc17734443 said:Intel's Skylake architecture and corresponding platform represent a huge evolution in connectivity, overclocking and, ultimately, system performance. This resource should help answer any questions you have about the company's current desktop PC design.

Everything We Know About Intel's Skylake Platform : Read more

Very informational though! :)

-

logainofhades I suspect that if Zen is in any way successful, Intel will back off a bit, on the non z overclock stance. If they price a chip that is competitive, say at least on the same single threaded performance level as Haswell, with a locked i3 or i5, AMD will get a much needed boost in sales. I honestly hope something like this happens. This one side dominating completely, is bad for consumers.Reply -

IInuyasha74 Reply17734455 said:

Thanks! Sadly, this page does not explain the nuances of other factors such as overclocking potential, and the probability of getting a skylake CPU that overclocks to 4.6, 4.8, etc17734443 said:Intel's Skylake architecture and corresponding platform represent a huge evolution in connectivity, overclocking and, ultimately, system performance. This resource should help answer any questions you have about the company's current desktop PC design.

Everything We Know About Intel's Skylake Platform : Read more

Very informational though! :)

Well you see, it is hard to put a number on that which would hold up reliably. Overclocking chips could land just about anywhere, and without testing dozens of samples we couldn't come up with an average overclock that Skylake seems to be able to hit that would hold up well enough. -

kunstderfugue Hopefully the competition later this year makes Intel reconsider the way they're treating their consumers.Reply -

logainofhades Yea, I have not been very happy with Intel, since Skylake released. The Xeon chipset part, in particular, irked me. The whole launch has been a disaster of confusion. Glad this article was made to clear some things up.Reply -

TJ Hooker ASUS, MSI, and Gigabyte all ventured into non-k overclocking on their Z170 boards as well. The BIOSs that enabled it may have been labelled as betas, and I'm not sure if they're available through official channels anymore. But if Biostar gets a mention for releasing and then retracting non-k OC, I don't know why these other manufacturers aren't brought up.Reply

Another drawback of non-k BCLK OC is that CPU core temperature can no longer be read.

Lastly, another potential topic to add is the subject of DDR4 at speeds greater than 2133 MHz. I've seen many forum questions about what CPU/mobo support for running 2400+ MHz DDR4. I'm under the impression that you need a Z170 mobo (I could be wrong), I've seen people say you need an unlocked CPU (from personal experience I know this is wrong), could be handy to add a section to clear this up. -

josejones I am far more interested in articles about the soon to come Z270 motherboardsReply

200-Series Union Point Motherboards

http://www.tomshardware.com/forum/id-2983311/200-series-union-point-motherboards.html -

Jaran Gaarder Heggen Interresting article, but can you please add chipset for dual cpu xeon also in the Workstation area?Reply

-

hixbot ReplyI am far more interested in articles about the soon to come Z270 motherboards

You will be lucky to see Kaby Lake mobile before the end of 2016. It will be mid 2017 at the earliest before consumers can get their hands on desktop motherboards with Union Point.

200-Series Union Point Motherboards

http://www.tomshardware.com/forum/id-2983311/200-series-union-point-motherboards.html

Very hard to expect a detailed breakdown of that platform at this time.