Intel's 18A and TSMC's N2 process nodes compared: Intel is faster, but TSMC is denser

There are a few catches, though.

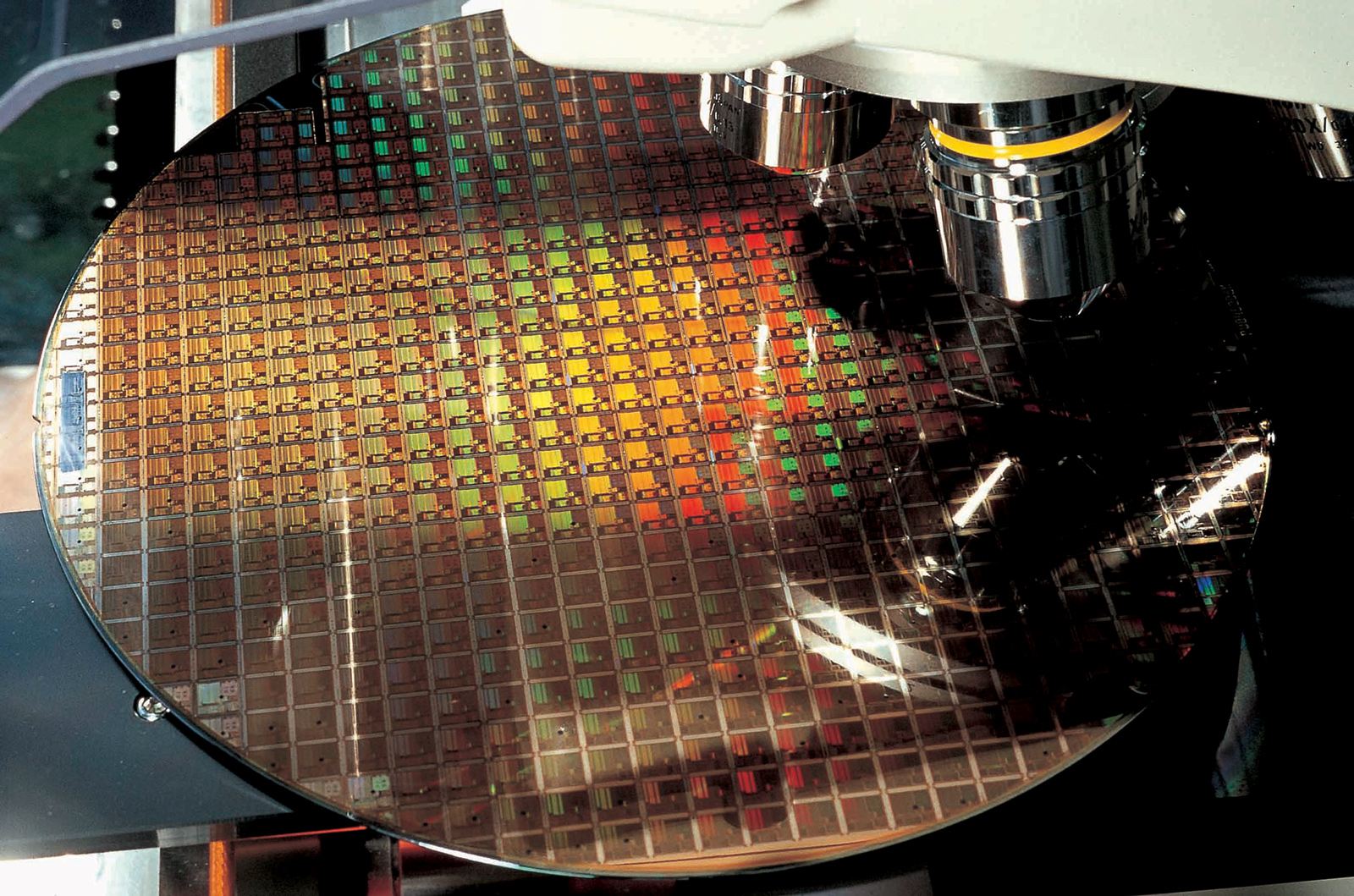

TechInsights and SemiWiki have published key details that Intel and TSMC disclosed about their upcoming 18A (1.8nm-class) and N2 (2nm-class) process technologies at the International Electronic Devices Meeting (IEDM). According to TechInsights, Intel's 18A could offer higher performance, whereas TSMC's N2 may provide higher transistor density.

Analysts at TechInsights believe that TSMC's N2 offers a high-density (HD) standard-cell transistor density of 313 MTr/mm^2, which far exceeds the HD cell density of Intel's 18A (238 MTr/mm^2) and Samsung's SF2/SF3P (231 MTr/mm^2). While the information more or less aligns with SRAM cell sizes for 18A, N2, and N3, as well as with TSMC's expectations for N2 and N3, there are some things to note.

First, this only concerns HD standard cells. Virtually all modern high-performance processors that rely on leading-edge nodes use a mix of high-density (HD), high-performance (HP), and low-power (LP) standard cells, not to mention capabilities like TSMC's FinFlex and NanoFlex.

Article continues belowSecondly, it is unclear how Intel's and TSMC's HP and LP standard cells compare. While it is logical to assume that N2 has a transistor density lead, it may not be as massive as the lead in HD standard cells. Third, in their papers presented at the IEDM event, both Intel and TSMC disclosed performance, power, and transistor density advantages of their next-generation 18A and N2 manufacturing processes over their predecessors. Still, there is currently no way to compare these two fabrication technologies head-to-head.

When it comes to performance, TechInsights believes that Intel's 18A will have a lead over TSMC's N2 and Samsung's SF2 (formerly known as SF3P). However, TechInsights uses a debatable method to compare the performance of the upcoming nodes, as it uses TSMC's N16FF and Samsung's 14nm process technologies as baselines and then adds announced node-to-node performance improvements from both companies to make its prediction. While this might serve as an estimate, it may not be entirely accurate.

On the other hand, Intel specializes in making high-performance processors, so 18A could be tailored for performance and power efficiency rather than HD transistor density. At the end of the day, 18A supports PowerVia, a backside power delivery network, and chips that use it might have performance and transistor density advantages over TSMC's N2, which does not support this capability. However, this does not mean that every 18A chip will use PowerVia.

When it comes to power, TechInsights analysts presume that an N2-based chip will consume less power than a similar SF2-based IC, as TSMC has typically led in power efficiency in recent years. As for Intel, this remains to be seen, but at least 18A will provide an advantage in this area.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

There are a couple of other things to note. Intel's 18A is set to enter mass production in mid-2025 when Intel begins production of its Core Ultra 3-series ‘Panther Lake' processors, which will be available later this year. By contrast, TSMC's N2 is slated for high-volume manufacturing in late 2025, and the first products produced on this node will not be available until mid-2026 at the earliest, with mass-market products expected in Fall 2026. Samsung does not disclose when exactly its SF2 enters HVM, only stating '2025,' which could mean any time from Q1 to Q4 this year.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Kindaian Again Apples and Oranges.Reply

Comparing 2 chip design technologies is not as simple as which is better.

You need to compare same density against power use and termal generation. On the TSMC specs for each of the production densities that they sport, they show a graph that indicates that chips can be tailored for more performance or less power consumption.

So without knowing exactly how each chip is designed with each technology, the only thing that you can do is measure the outcomes (performance vs power consumption).

Smaller transistors tend to reduce the power consumption by itself (less material = less electrons needed to flip states = less power consumption), but as the chips are also designed with higher and higher frequencies, that economy just vanishes, and you get an higher thermal output.

So i will wait for the chips comparisons by themselves, as that is a more robust way to ascertain which is which. And is the only way that matters because those chips are the ones in the market for people to buy (not a webpage with a PR announcement).

This year is shaping to be great for product comparisons with so many new tech hitting the shelves. -

bit_user Reply

Intel already delayed Clearwater Forest until "1H 2026", which suggests they're facing challenges in meeting their schedule. It might turn out that TSMC's N2 isn't too far behind in ramping, compared to Intel. Between the two, I have more faith in TSMC for fulfilling their promises and holding to their schedule.The article said:Intel's 18A is set to enter mass production in mid-2025 when Intel begins production of its Core Ultra 3-series ‘Panther Lake' processors, which will be available later this year. By contrast, TSMC's N2 is slated for high-volume manufacturing in late 2025, and the first products produced on this node will not be available until mid-2026 at the earliest, with mass-market products expected in Fall 2026. Samsung does not disclose when exactly its SF2 enters HVM, only stating '2025,' which could mean any time from Q1 to Q4 this year.

As for the nodes, Intel 18A might be technically more advanced, but TSMC has been so good at executing that I fully expect it to be competitive. It will be interesting to watch.

Also, I'm hoping that "3 nm"-class nodes ceasing to be the cutting edge will enable their use in more GPUs and client CPUs. -

Gururu I am so excited to see these advancements across the industry. High hopes for some super processing.Reply -

kwohlt Reply

Delays to CWF's advanced packaging. Not the node itselfbit_user said:Intel already delayed Clearwater Forest until "1H 2026", which suggests they're facing challenges in meeting their schedule. -

bit_user Reply

I'm excited, but within limits. Let's not forget how underwhelming Arrow Lake was, in spite of advancing by 2 major nodes! Yet, it clocked lower than Raptor Lake and sometimes performed worse, while using almost as much power. I get that some of its performance problems were due to the chiplet architecture, but it was still a real head scratcher!Gururu said:I am so excited to see these advancements across the industry. High hopes for some super processing.

Zen 5 was a little less surprising, given that it stayed on pretty much the same node as Zen 4, but still a little surprising, given the move from a bleeding edge 5 nm node to a mature, optimized one.

So, I'm a little concerned that these smaller nodes just aren't going to support the kind of clock speeds we've become accustomed to, and IPC gains aren't the easiest way to increase performance. -

P.Amini Reply

What do you mean? Are these smaller nodes slower (clock wise)? Why would they?bit_user said:I'm excited, but within limits. Let's not forget how underwhelming Arrow Lake was, in spite of advancing by 2 major nodes! Yet, it clocked lower than Raptor Lake and sometimes performed worse, while using almost as much power. I get that some of its performance problems were due to the chiplet architecture, but it was still a real head scratcher!

Zen 5 was a little less surprising, given that it stayed on pretty much the same node as Zen 4, but still a little surprising, given the move from a bleeding edge 5 nm node to a mature, optimized one.

So, I'm a little concerned that these smaller nodes just aren't going to support the kind of clock speeds we've become accustomed to, and IPC gains aren't the easiest way to increase performance. -

bit_user Reply

I shouldn't speculate about this, since it's well outside my area of expertise and I don't have a good source on it. It was just an observation that's hopefully not bad news for even smaller nodes.P.Amini said:What do you mean? Are these smaller nodes slower (clock wise)? Why would they? -

Pierce2623 Reply

It’s so crazy that Apple is the only company that sells consumers leading edge chips now.bit_user said:Intel already delayed Clearwater Forest until "1H 2026", which suggests they're facing challenges in meeting their schedule. It might turn out that TSMC's N2 isn't too far behind in ramping, compared to Intel. Between the two, I have more faith in TSMC for fulfilling their promises and holding to their schedule.

As for the nodes, Intel 18A might be technically more advanced, but TSMC has been so good at executing that I fully expect it to be competitive. It will be interesting to watch.

Also, I'm hoping that "3 nm"-class nodes ceasing to be the cutting edge will enable their use in more GPUs and client CPUs. -

Pierce2623 Reply

Realistically they can’t say until they’re making production chips. Zen4 turned out to be able clock a fair bit better than originally expected because n5 just clocked MUCH higher than n7. That’s a large part of the reason that while AMD played down Zen4 and built up Zen5, Zen4 ended up being a much larger performance jump even though zen5 was a MUCH larger change in architecture.P.Amini said:What do you mean? Are these smaller nodes slower (clock wise)? Why would they?