AMD's Upcoming EPYC Servers Could Have up to 162 PCIe 4.0 Lanes

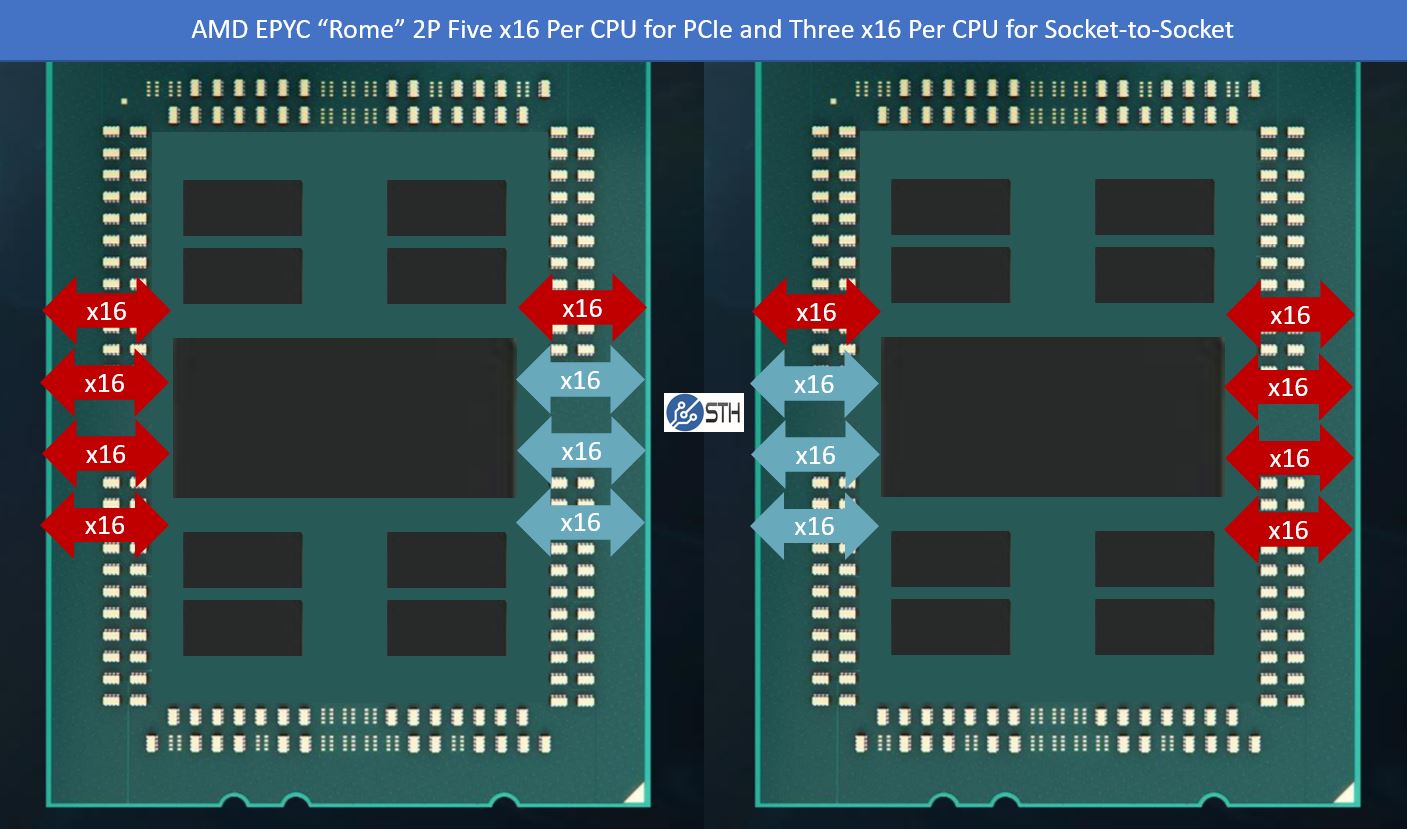

Though AMD has kept rather silent about its upcoming Zen 2-based EPYC Rome server processors, that hasn't prevented speculation about their capabilities. For example, while AMD has said that a single EPYC Rome processor could deliver up to 128 PCIe lanes, the company hasn't stated how many lanes two processors could deliver in a dual-socket server.

According to ServeTheHome.com, there's a distinct possibility EPYC could feature up to 162 PCIe 4.0 lanes in a dual-socket configuration, which is 82 more lanes than Intel's dual-socket Cascade Lake Xeon servers. That even beats Intel's latest 56-core 112-thread Platinum 9200-series processors, which expose 80 PCIe lanes per dual-socket server.

Patrick Kennedy at ServeTheHome, a publication focused on high-performance computing, and RetiredEngineer on Twitter have both concluded that two Rome CPUs could support 160 PCIe 4.0 lanes. Kennedy even expects there will be an additional PCIe lane per CPU (meaning 129 in a single socket), bringing the total number of lanes in a dual-socket server up to 162, but with the caveat that this additional lane per socket could only be used for the baseboard management controller (or BMC), a vital component of server motherboards.

RetiredEngineer also theorizes that Rome could even deliver up to 190 lanes (plus two BMC lanes), though ServeTheHome states it is not aware of plans to expose that many lanes. ServeTheHome speculates these additional PCIe lanes could also help AMD's GPU business because GPUs consume 16 PCIe lanes apiece.

AMD has not commented on the veracity of these theories, but a representative speaking to ServeTheHome was apparently "not overly excited" about the publication's article.

If @RetiredEngineer and ServeTheHome did their math correctly, then Intel has even more serious competition than AMD has let on. Intel's latest flagship Cascade Lake architecture, despite having up to 56 cores thanks to a dual-die design like AMD's Multi-Chip Module approach, will face significant challenges against Rome. The new Rome processors have eight more cores, a newer 7nm node from TSMC, likely a lower price tag and power consumption, and perhaps significantly more PCIe lanes. Though AMD faces an uphill battle for the server market, Rome's hardware advantages against Xeon will surely entice some data centers, especially those eager for more PCIe lanes.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Matthew Connatser is a freelancing writer for Tom's Hardware US. He writes articles about CPUs, GPUs, SSDs, and computers in general.