TSMC Extends 7nm Lineage With EUV-based 6nm Process

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

TSMC has announced its new 6nm node. The process will leverage EUV for a small density boost, and by being design-rule compatible with its 7nm node, all TSMC 7nm IP can be reused, making for a fast transition to this improved process technology.

Developing refinements of a process technology is not something new, especially for foundries. A prime example would be 28nm, which launched in 2012 without the important HKMG transistor technology. TSMC over the years has greatly expanded its 28nm-class offerings such as 28HP, 28HPM, 28LP, and so on.

What has changed in recent years, however, is that the marketing behind these intra-node improvements has become more and more aggressive, alienating the name even more from any physical transistors features (which hasn’t been the case for about two decades now).

Article continues belowThe last addition to TSMC's 28nm process class was 22nm. Similarly, NVIDIA's Volta V100 is based on 12FFN despite being the same density as 16N. Samsung is no less shy in this regard, for instance, every process from 4nm to 7nm belonging to its 7nm family. The most infamous example of this happened when the foundries transitioned to FinFET at 16/14nm, basically skipping the 20nm name, which still causes the mismatch between Intel's 10nm and 7nm naming from its competitors.

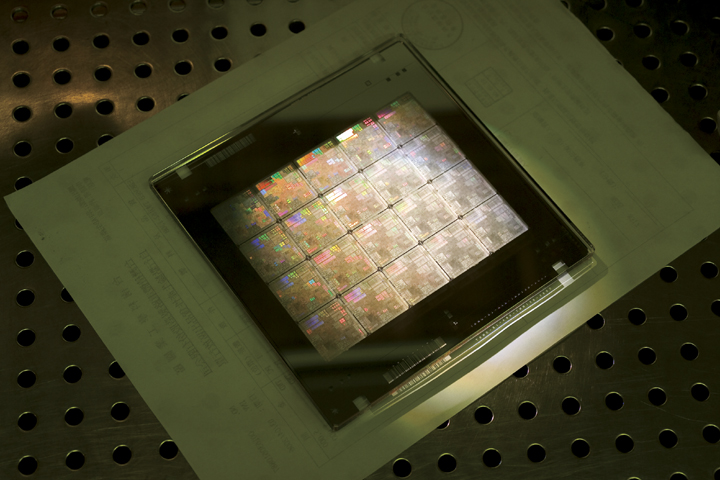

This brings us to TSMC’s 7nm portfolio. The process went into production last year with Apple’s A12 chip, followed by AMD’s Radeon Instinct MI60. TSMC so far has 7FF and a 7HPC as 7nm offerings, but had also announced a 7nm+ node, leveraging EUV in a few process layers before more widely deploying EUV at 5nm. Last quarter, TSMC revealed that there would be the second generation of 7nm. No specific name was given, but a recent rumor from Digitimes cited 7nm Pro for Apple’s A13 chip.

Today’s announcement adds 6nm as a third 7nm enhancement (besides 7nm Pro and 7nm+). TSMC’s aims to provide a compelling performance-to-price ratio as well as a fast time to market. This is done by being design-rule-compatible with 7nm, hence providing a seamless migration path from 7nm with a short design cycle time. TSMC says 6nm will have higher performance than 7nm and will deliver an 18% improvement in transistor density compared to 7nm. This is very similar to its 7nm+ that is already in risk production, but TSMC did not disclose how 7nm+ and 6nm differ.

Samsung yesterday also unveiled a 6nm node, providing no further details. However, it looks like the most direct equivalent to TSMC's 6nm from Samsung is its 5nm process, for which they completed development, as part of their announcement yesterday. (This will cause even more divergence with respect to node naming in the industry, as Samsung and TSMC's nodes with the same name will no longer be similar in density at 5nm, as it looks like it won't be until Samsung's 3nm that it provides a full node shrink from 7nm.)

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

TSMC announced that 6nm would go into risk production in the first quarter of 2020, which is probably later than Samsung's 5nm. Volume production usually follows about a year later, so this will not be a leading edge node, given that TSMC’s own 5nm process is already in risk production since earlier this month. TSMC has said that 5nm will deliver a 1.8x increase in density, being a full node shrink.

Last year, TSMC took the transistor density leadership in the semiconductor logic industry from Samsung with 7nm. Samsung had taken that position by being a bit faster than TSMC to 10nm in early 2017, which was about 30% denser than Intel’s 14nm. Intel has struggled for years with getting 10nm yield production ready.