PCI Express Scaling Analysis

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

PCI Express Basics

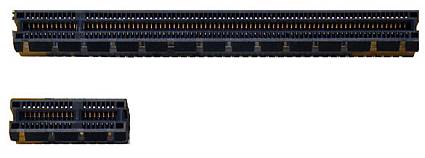

These are the most common PCI Express slots: the large one incorporates 16 lanes, while the small one is a single lane connector for simple expansion cards.

Unlike PCI and PCI-X, PCI Express is based on a serial protocol. This means that the interface can get by with a very limited number of wires. In exchange, these are clocked much faster than the parallel busses in order to obtain a high bandwidth. Additionally, that bandwidth can be easily multiplied by merging several PCI Express lanes. The specification provides for five different slot types: x16, x8, x4, x2 and x1, where the "x" is pronounced as "by"; for example, the widest PCIe variant is called "by sixteen".

PCI Express is a bi-directional point-to-point link, meaning that it offers the same bandwidth in both directions, and does not need to share its bandwidth with other devices, as is the case with parallel PCI. Due to its modular architecture, motherboard makers are able to distribute the available PCI Express resources to their preferred slot configuration. A total of 20 PCI Express lanes can be arranged as one x16 PCIe slot and four x1 PCIe slots, which is also common practice with many chipsets. Alternately, five x4 PCIe ports can be implemented for mid-range server systems. Whatever is mathematically doable can be implemented with PCI Express. Also, PCI Express could make it possible to mix chipset components from different manufacturers.

PCI Express has one disadvantage, though: the more PCIe lanes, the higher the power consumption. This is the main reason why chipsets with 40 and more PCI Express lanes require considerably more power than simpler products. As a rule of thumb, 16 additional PCI Express lanes will boost the power requirements by approximately 10 W with the current chipset generations.

| PCI Express Lines | Bandwidth per Stream | Bandwidth, duplex |

|---|---|---|

| 1 | 256 MB/s | 512 MB/s |

| 2 | 512 MB/s | 1 GB/s |

| 4 | 1 GB/s | 2 GB/s |

| 8 | 2 GB/s | 4 GB/s |

| 16 | 4 GB/s | 8 GB/s |

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: PCI Express Basics

Prev Page How Much Bandwidth Does PCI Express Graphics Really Need? Next Page PCI Express: X1, X4, X8, X16

Patrick Schmid was the editor-in-chief for Tom's Hardware from 2005 to 2006. He wrote numerous articles on a wide range of hardware topics, including storage, CPUs, and system builds.