Soft Machines Startup Promises 'Virtual Cores' Twice As Fast As Physical Cores

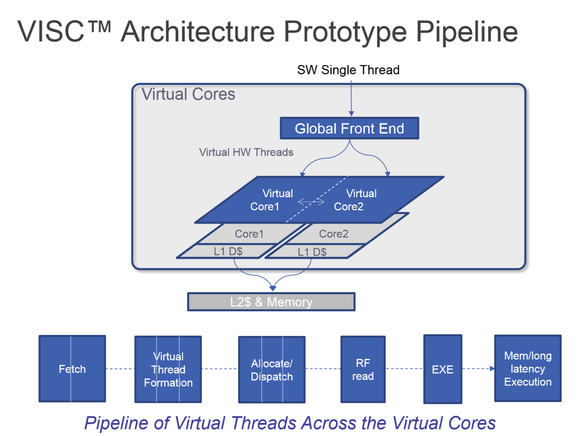

A new well-funded startup called "Soft Machines," created by chip veterans, is working on a new type of processor based on the "Virtual Instruction Set Computing" (or VISC, as opposed to RISC or CISC) architecture. The firm is essentially creating "virtual cores" that it says are 1.7-2.2 times faster for a given single-threaded task (scoring 2.1 instructions per core in SPEC 2006 benchmark) compared to Intel Haswell's 1.39 instructions per clock.

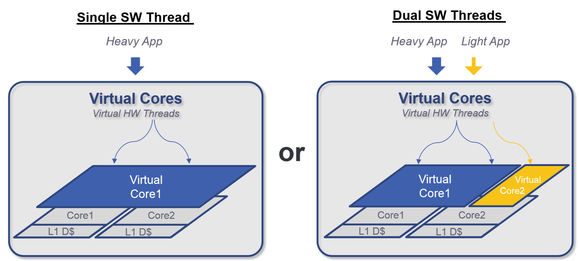

Most apps or programs aren't usually optimized for multi-core processors or multiple threads, so they end up using a single core, even if the processor has more. That's wasted performance, and wasted time, as the processing could happen much faster if it used all or most of the cores.

The way VISC works is that it takes multiple physical cores to create a single "virtual core," which now has higher single-threaded performance than a single physical core. The main benefit here is that the apps would only use a single thread in the first place. These apps can continue to use one thread, but performance-wise they will perform as if they were using multiple threads or cores for processing, or a significantly faster physical core.

Soft Machines claimed that if its virtual cores maintained comparable performance to regular processor cores, its chips' power consumption could be reduced by one quarter to one third. The power consumption could drop by half if the app would be using two virtual threads. The virtual chip can apparently split into multiple virtual cores, as well.

The technology prototype is already able to boot Linux and Android 4.0 (Ice Cream Sandwich). The company said it eventually wants to build a complete System on a Chip with a GPU, video accelerator and DRAM controller.

What Soft Machines is doing sounds a little similar to what Nvidia did with its Denver core. Nvidia scrapped hardware-based out-of-order execution in favor of an in-order hardware design with software-based out-of-order-execution.

Thanks to this new design, Denver achieves the highest single-threaded performance in the mobile chip market right now, going by Geekbench benchmarks. It's also important to note that Geekbench only supports 32-bit Android right now (so a further 10-20 percent performance increase is expected for the 64-bit mode), and that Denver is still a 28nm chip, while some of its competition (Apple, Samsung) has already moved to 20nm. Denver on the same 20nm could have seen even higher performance.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

It's usually close to impossible for a chip start-up to succeed in a world of chip giants such as Intel, AMD, Qualcomm and Nvidia, but if Soft Machines can't make it on its own, it might find a good home at Nvidia, which has just begun experimenting with software-based CPU designs.

Follow us @tomshardware, on Facebook and on Google+.

Lucian Armasu is a Contributing Writer for Tom's Hardware US. He covers software news and the issues surrounding privacy and security.

-

TechyInAZ This type of CPU is exactly what I've always thought of since I was a child. What I thought of is an octo core CPU that could virtually turn into one single core when necessary and separate into dual, triple, 5, hexa, 7 and octo core environments when needed.Reply

Basically, their doing exactly what I thought of years ago. So cool that we can actually start making cpus that can do this! -

qlum If this tech was used on amd it could seriously help them get back into business with their multicore cpu's being quite good at multithreaded performance but sucking at single threaded.Reply -

InvalidError With the extra complexity and latency of making out-of-order decisions in software, I would be skeptical about the conditions under which performance scaling can actually be achieved and how power-efficient the overall process would be. I find it ironic that putting OoE in the Atom is how Intel drastically improved Atom's performance per watt. Putting HT back in did not hurt either.Reply

At least seeing the industry fork in three different paths should make things entertaining for a while. -

yumri will it still be able to run windows 7, 8, 8.1, and 10? also will it be able to run all the programs made with the mind set of a x86 instruction set?Reply -

TechyInAZ Reply14444341 said:will it still be able to run windows 7, 8, 8.1, and 10? also will it be able to run all the programs made with the mind set of a x86 instruction set?

We won't know until soft machines makes a x86 version. -

InvalidError Reply

Since Intel has not granted any other company a license for the x86 instruction set and AMD only has a non-transferable license, Soft Machine's CPU is almost certainly non-x86.14444341 said:will it still be able to run windows 7, 8, 8.1, and 10? also will it be able to run all the programs made with the mind set of a x86 instruction set?

That thing probably runs the ARM instruction set on their proprietary non-ARM back-end, much like what Transmeta used to do with x86. -

shafe88 I've been waiting for something like this. I've had a similar idea, but never thought it was possible.Reply

https://3dwarehouse.sketchup.com/model.html?id=6fd603d6eca6ea958f217d4aca5abdac -

Mike Friesen Reply14444477 said:

Since Intel has not granted any other company a license for the x86 instruction set and AMD only has a non-transferable license, Soft Machine's CPU is almost certainly non-x86.14444341 said:will it still be able to run windows 7, 8, 8.1, and 10? also will it be able to run all the programs made with the mind set of a x86 instruction set?

That thing probably runs the ARM instruction set on their proprietary non-ARM back-end, much like what Transmeta used to do with x86.

Doesn't VIA still have an x86 licence? I doubt it's transferable, but I would't be too surprised for a band of chip veterans joining with VIA to make a new low-powered SoC. More likely though, it'll be very different from x86 or arm, because I think x86 is CISC and arm is RISC. Very different from VISC, I would assume, and if based on either, they would really just "become VISC" because if the thing that describes VISC is that it uses virtual cores. -

Shin-san It should work with any architecture. If it won't work on the x64 instruction itself, it may work on the micro-opsReply -

Ori25 ounds a little like backward progress. Software should use more cores not make one again. We will live and see how it goes...Reply