Researchers Create Transistors for 'Ultimate Scaling' Beyond 10 nm

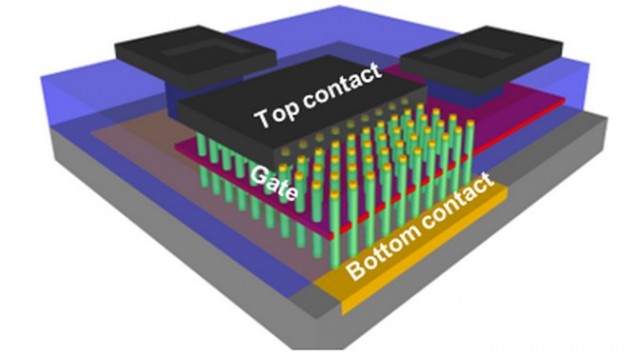

This “all-gate approach” utilizes a “forest of nanowires all under control of the same gate.”

It has been well established that as transistor sizes continue to decrease, planar technologies are reaching their limit. Thus far, we’ve seen technologies such as FinFET be introduced to partially alleviate this problem.

A team of researchers from the Laboratory for Analysis and Architecture of Systems in France is focusing on a new approach that utilizes a “forest of nanowires all under control of the same gate.” According to IEEE Spectrum, this design is composed of an array of 225 doped-silicon nanowires where each wire has a 14 nm chromium layer surrounding its midsection that serves as the gate.

Promisingly, the design’s manufacturing process doesn’t involve any complicated lithography. The researchers plan to eventually develop IGA nanowires because of their better electron mobility. Though the nanowire forest design is certainly more complex than the aforementioned FinFET transistor design, it could potentially be simplified by reducing the total number of nanowires needed to develop the transistor.

Article continues belowGet Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Tarun Iyer was a contributor for Tom's Hardware who wrote news covering a wide range of technology topics, including processors, graphics cards, cooling systems, and computer peripherals. He also covered tech trends such as the development of adaptive all-in-one PCs.

-

cats_Paw with transistors so small, how is it that the electricity does not jump from one transistor to another randomly? (i mean, they have to be preaty close to each other, right?Reply -

tomfreak This may sound silly, but I am sticking to the mature technolgy that is just above the 10nm limit then wait a few years for my next upgrade cycle. 2011 socket 14nm/16nm broadwell-E should last 5-10yrs till next upgrade, by then this 'Ultimate Scaling' Beyond 10 nm should be matured enough.Reply -

JAYDEEJOHN Depending on design/useage, it will be interesting to see how they keep this design cooled.Reply

It would definitely make for huge redesigns -

ddpruitt Reply10872382 said:with transistors so small, how is it that the electricity does not jump from one transistor to another randomly? (i mean, they have to be preaty close to each other, right?

Actually this is occurring. We're really close to the limit of what can be done. Quantum tunneling is driving up the voltages required to run transistors and driving up heat. Along with a couple of other problems we're close to the point where currently technology can't be scaled down much more. Another 5 or 6 years and we'll something new to keep scaling down, or another technology all together. -

gsxrme Dont forget people. As we make things smaller the voltage required is lower. 14nm i7 will be some where around .6v!Reply -

ddpruitt Reply10873497 said:Dont forget people. As we make things smaller the voltage required is lower. 14nm i7 will be some where around .6v!

Actually there's an inflection point that we've just about reached were the voltages will have to climb again, unless the design radically changes. -

warezme FinFET not to be confused with the weight loss drug FenPhen that caused fat people to die of heart attacks.Reply -

iam2thecrowe Reply10873438 said:10872382 said:with transistors so small, how is it that the electricity does not jump from one transistor to another randomly? (i mean, they have to be preaty close to each other, right?

Actually this is occurring. We're really close to the limit of what can be done. Quantum tunneling is driving up the voltages required to run transistors and driving up heat. Along with a couple of other problems we're close to the point where currently technology can't be scaled down much more. Another 5 or 6 years and we'll something new to keep scaling down, or another technology all together.

like optical circuits