Alder Lake-S Compiler Update Points to big.LITTLE Desktop Chips

New GNU compiler updates released today (as reported by Phoronix) serve as yet another sign that Intel will release its hybrid architecture, which combines big cores with smaller cores, for desktop PCs when the Alder Lake-S CPUs land.

Intel's Alder Lake-S CPUs will follow the company's Rocket Lake chips, and while Intel hasn't confirmed, information has surfaced that the new chips could be the first Intel desktop chips to support it's Hybrid Architecture. The Alder Lake chips are rumored to come with eight large cores and eight small cores to combine the high-end performance of the big compute cores with the power efficiency of smaller Atom cores.

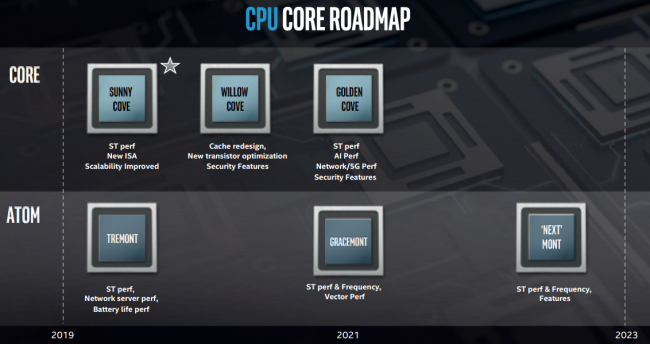

This design builds upon the big.LITTLE (Big.BIGGER in Intel parlance) design that debuted in the company's 3D Lakefield chips. These designs incorporate one large Sunny Cove core combined with four Atom Tremont smaller cores in an ARM-like design. With the architecture proven and already working its way through the ecosystem, it's rational to expect Intel to scale it up to tackle desktop PCs, too.

The GNU compiler updates include a list of compatible instructions for both Intel's upcoming data center Sapphire Ridge chips and Alder Lake desktop chips, with the latter noticeably missing support for AVX-512, a SIMD instruction that Intel recently introduced to its desktop chips. These instructions are disabled in Intel's hybrid Lakefield chips to keep the instruction set consistent between cores (Atom doesn't support AVX instructions), therefore easing operating system scheduling routines that target different workloads at the cores best suited for the task. Therefore, the lack of AVX-512 support for Alder Lake could serve as further evidence that Intel will bring its hybrid architecture to desktop PCs.

However, while the lack of AVX-512 support seems to point to a hybrid architecture, the Alder Lake support matrix does list standard AVX instructions that aren't supported by the current-gen Atom Tremont cores. That means the next-gen Atom Gracemont cores, largely thought to be the 'little' cores used in Alder Lake, could bring AVX support, albeit in limited fashion, to the Atom line. Intel's previously disclosed Atom roadmap does point to increased vector performance with Gracemont, making those Atom cores extremely likely to appear in Alder Lake.

Meanwhile, the Sapphire Rapids chips come with many of the AVX trimmings we'd expect, like AVX512F, CLWB, AVX512VL, AVX512BW, AVX512DQ, AVX512CD, AVX512VNNI, and the new AVX512BF16 that enables support for bfloat 16, a compact numerical format that provides similar performance to FP32, but with half the bits.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.