Intel prepares for Nova Lake CPUs with new Linux support — retiring 20-year-old 'Family 6' designation in favor of 'Family 18'

Nova Lake seems to be on track.

For the first time in more than two decades, Intel is moving past its long-standing CPU classification system in favor of a new one. With Nova Lake, the company’s next generation of processors, Intel is signaling the end of the Family 6 era that has defined x86 processors since the late ’90s. This change was unearthed as part of the Linux enablement Intel is doing for Nova Lake as we speak.

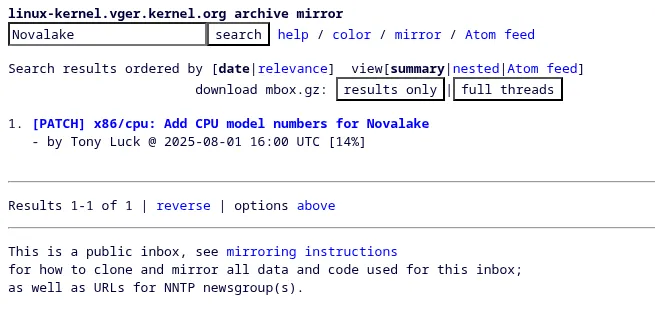

The initial patch, spotted in the Linux kernel mailing list by Phoronix, introduces Nova Lake under a brand-new identifier: Family 18. This marks a clean break from the legacy Family 6 framework, which has carried everything from Pentium Pro to Arrow Lake. The move required significant refactoring in previous kernel releases, ensuring Linux code could adapt to architectures beyond Family 6.

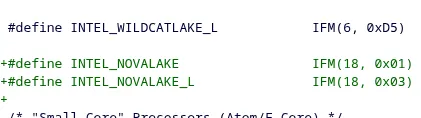

The update also adds definitions for two models: Nova Lake (Family 18, Model 1) and Nova Lake L (Family 18, Model 3), the latter likely denoting low-power mobile variants. These early hooks allow future driver-level patches—covering graphics, power management, and scheduling—to integrate seamlessly once Nova Lake hardware lands in late 2026.

This isn’t just a naming exercise like the company dropping the "i" branding for its CPUs two years ago, rather Intel’s segmentation strategy is becoming clearer: Family 18 for client CPUs, while Family 19 will house next-gen Xeon processors like Diamond Rapids. By splitting desktop and server under distinct families, Intel aims to simplify feature tracking and driver enablement across platforms.

Although these kernel patches don’t reveal any hardware specs—they just add simple identifiers to the Linux kernel—the roadmap hints at aggressive performance targets. Nova Lake is expected to double core counts over Arrow Lake, with rumored configurations scaling up to 16 Performance cores, 32 Efficiency cores, and 4 LPE cores, along with a new iGPU based on the Xe4 “Druid” architecture. There’s also speculation that Nova Lake will span everything from desktops and laptops to emerging categories like gaming handhelds with Nova Lake-AX, suggesting Intel wants its Linux groundwork to cover a broad range of use cases.

With Panther Lake expected to launch first and bring Intel 18A to the market, likely under the Core Ultra 300 branding, Nova Lake’s debut is still a year away. But Intel’s early enablement ensures that by the time Ubuntu 26.04 LTS arrives, Linux users will have full support baked in—something that’s become an essential part of Intel’s playbook.

Follow Tom's Hardware on Google News to get our up-to-date news, analysis, and reviews in your feeds. Make sure to click the Follow button.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Hassam Nasir is a die-hard hardware enthusiast with years of experience as a tech editor and writer, focusing on detailed CPU comparisons and general hardware news. When he’s not working, you’ll find him bending tubes for his ever-evolving custom water-loop gaming rig or benchmarking the latest CPUs and GPUs just for fun.

-

usertests I'm eager to see Wildcat Lake and Panther Lake in action.Reply

Nova Lake will mark the first time that Intel has tried multiple CPU chiplets for client desktop, looking a lot like AMD designs since Zen 2/3. For example, L3 cache will be split into two pools. Maybe you get 36-48 MiB in each one as the maximum available to a single core (Arrow Lake is 36 MiB), but the marketing department calls it 72-96 MiB.

Each compute tile will have up to 8P + 16E that we've grown accustomed to. Arrow Lake altered the Alder/Raptor design to intersperse the P- and E-cores for better latency when switching threads between them. There may be weird scheduling issues arising from a second tile, but it shouldn't be completely new to Intel since there have been Xeons with multiple tiles. These tiles being heterogeneous is a twist though. Then we'll apparently get 4 LPE-cores on the SoC tile. While there's deep skepticism about the benefits of lowering idle power consumption on desktop, you should be able to disable these, as others have already done in Meteor Lake.

For the leaked X3D competitors, they will only use one compute tile (all you need for gaming), but include the extra cache. Avoiding the complexity of 7950X3D/9950X3D or cost of a second cache chiplet is a good idea. -

Li Ken-un Reply

I’m hoping this release finally crosses out all the disadvantages suffered by the 7950X3D, 9950X3D, and all current Intel client computing CPUs.usertests said:or the leaked X3D competitors, they will only use one compute tile (all you need for gaming), but include the extra cache. Avoiding the complexity of 7950X3D/9950X3D or cost of a second cache chiplet is a good idea.

A CPU that supplies extra cache to all cores equally

A CPU that supports the same instruction set extensions across all cores without gimping particular ones―say AVX-512Intel needs to nail both. AMD’s got the latter already. (ECC support has been about the same with both lately.)

Or better yet, offer P-core-only CPUs with all of their native features enabled. It’s not like Intel has never done it―just much later in the lifecycle and with instruction set extensions still gimped as with the heterogeneous-cored predecessors. -

usertests Reply

Intel announced their "solution" to the AVX-512 problem: AVX10 back in 2023. I don't think they've ever said when it would arrive. Someone claimed Panther Cove, but I believe "x86S" was still alive at the time that was said. AVX10.2 can indeed work on both P-cores and E-cores.Li Ken-un said:A CPU that supports the same instruction set extensions across all cores without gimping particular ones―say AVX-512

The Intel Core 5 120(F) could be based on the old 6P+0E Alder Lake silicon or the new 12P+0E "Bartlett Lake". I wouldn't expect much P-core-only action from Intel, or full AVX-512 outside of enterprise chips. AMD did deliver full-width AVX-512 in Zen 5 non-mobile, but Intel can probably cope with having a disadvantage since there are relatively few consumer workloads that can use AVX-512. The big one I know about is emulation, particularly RPCS3.

We can expect that AMD will keep the unequal cache flaw alive for high-end Zen 6 X3D, but with a twist: the 12-core model will be using a single CCD. So there will be a greater than 50% multi-threaded improvement when sticking with the 9800X3D replacement, alongside an increase in cache, likely to 144 MiB. Zen 6 desktop chips may also have 2 additional "LP" cores in the I/O chiplet, that are technically unequal but unlikely to cause any scheduling problems since they'll never be prioritized. -

HardwiredWireless All the amd fan boys thought Intel wasn't still making better products because they misinterpreted the first iteration of the new design. They will learnReply -

Mr Majestyk Reply

Same here. I feel if Panther Lake executes without issues it will be a superb mobile offering and I'm looking forward to the top tier 4P+8E+4LPE+ 13Xe in the 45W range with LPDDR5x 8533 would be quite a beast.usertests said:I'm eager to see Wildcat Lake and Panther Lake in action.

Nova Lake will mark the first time that Intel has tried multiple CPU chiplets for client desktop, looking a lot like AMD designs since Zen 2/3. For example, L3 cache will be split into two pools. Maybe you get 36-48 MiB in each one as the maximum available to a single core (Arrow Lake is 36 MiB), but the marketing department calls it 72-96 MiB.

Each compute tile will have up to 8P + 16E that we've grown accustomed to. Arrow Lake altered the Alder/Raptor design to intersperse the P- and E-cores for better latency when switching threads between them. There may be weird scheduling issues arising from a second tile, but it shouldn't be completely new to Intel since there have been Xeons with multiple tiles. These tiles being heterogeneous is a twist though. Then we'll apparently get 4 LPE-cores on the SoC tile. While there's deep skepticism about the benefits of lowering idle power consumption on desktop, you should be able to disable these, as others have already done in Meteor Lake.

For the leaked X3D competitors, they will only use one compute tile (all you need for gaming), but include the extra cache. Avoiding the complexity of 7950X3D/9950X3D or cost of a second cache chiplet is a good idea.

I'm also prepared to hold off on Zen6 until I see Nova Lake. Nova Lake Ultra 7 with 14+24+4 would be a productivity beast and with the changes to memory controller should be a good gaming cpu too. Even Ultra 5 with 8+16+4 matches Alder Lake i9 in cores (excluding LPE) and would be a great cpu. -

George³ Only interesting for me from Intel Nova Lake is... faster connection with South Bridge or motherboard chipset and fact(?) that i tel will add 16 lanes PCIe 5.0 on it. That will increase significantly number of PCIe 5.0 on Intel mainstream platform.Reply

Otherwise, the last 2-3 generations of the main lines from both Intel and AMD are fully modern and productive enough for the home entertainment needs of 95%+ of the planet's population. -

usertests Reply

That's why the ultra low end like Wildcat Lake is fun. The Atom floor is rising up from low power Skylake-like performance to Alder Lake-like, presumably. But it will unavoidably get more expensive if it's using Intel 18A.George³ said:Otherwise, the last 2-3 generations of the main lines from both Intel and AMD are fully modern and productive enough for the home entertainment needs of 95%+ of the planet's population.