Support for AMD's Zen 2 Added in Linux, Optimizing For 7nm EPYC Rome Architecture

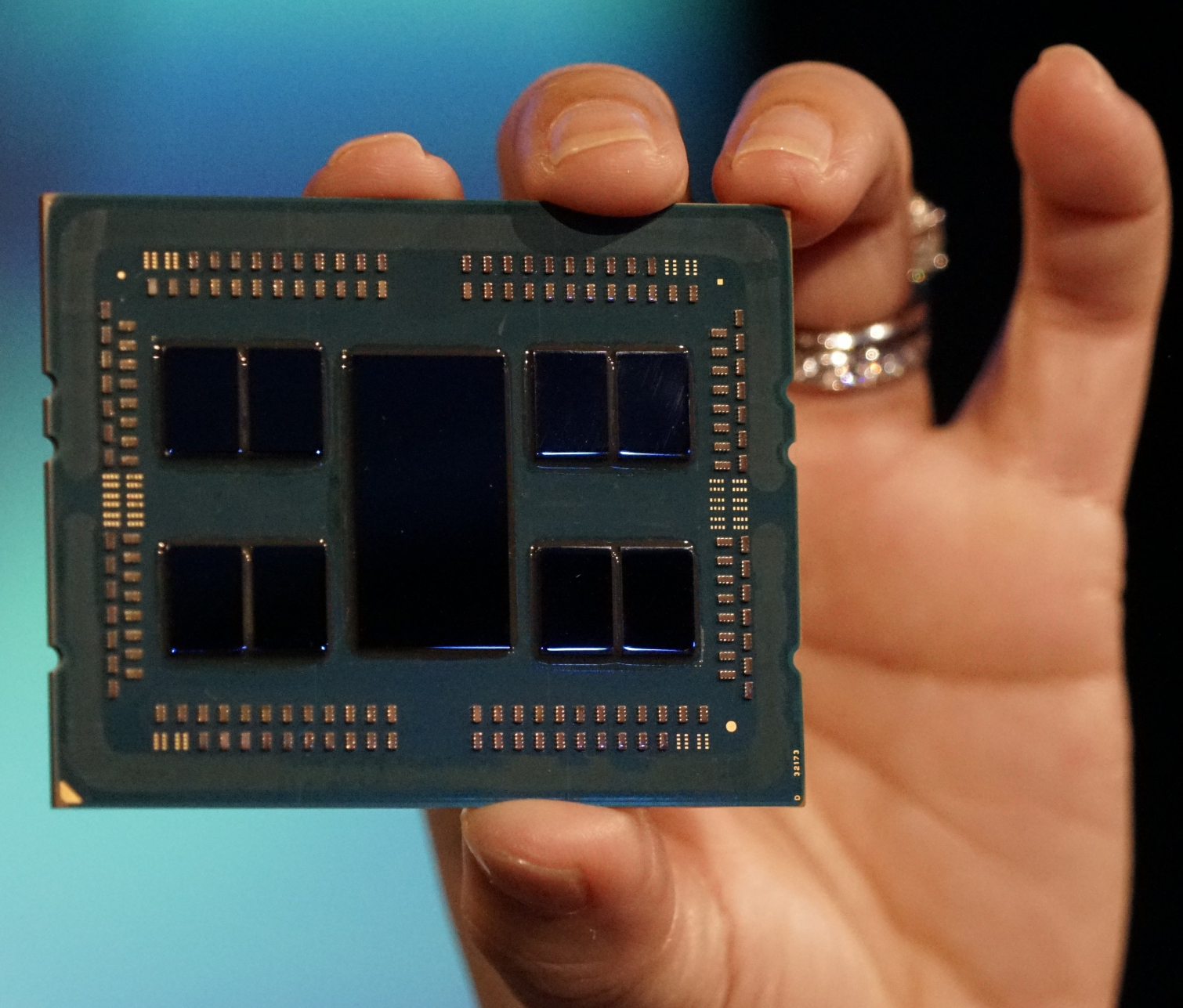

The Linux-lovers over at Phoronix reported that Linux 4.21 includes important new optimizations for the new Zen 2 architecture found in AMD's Rome processors. AMD's new 7nm EPYC Rome chips bring a new unique architecture to the table that should enable unprecedented low price points paired with up to 64 cores and 128 threads, but new architectures require optimization, particularly in light of AMD's unique design.

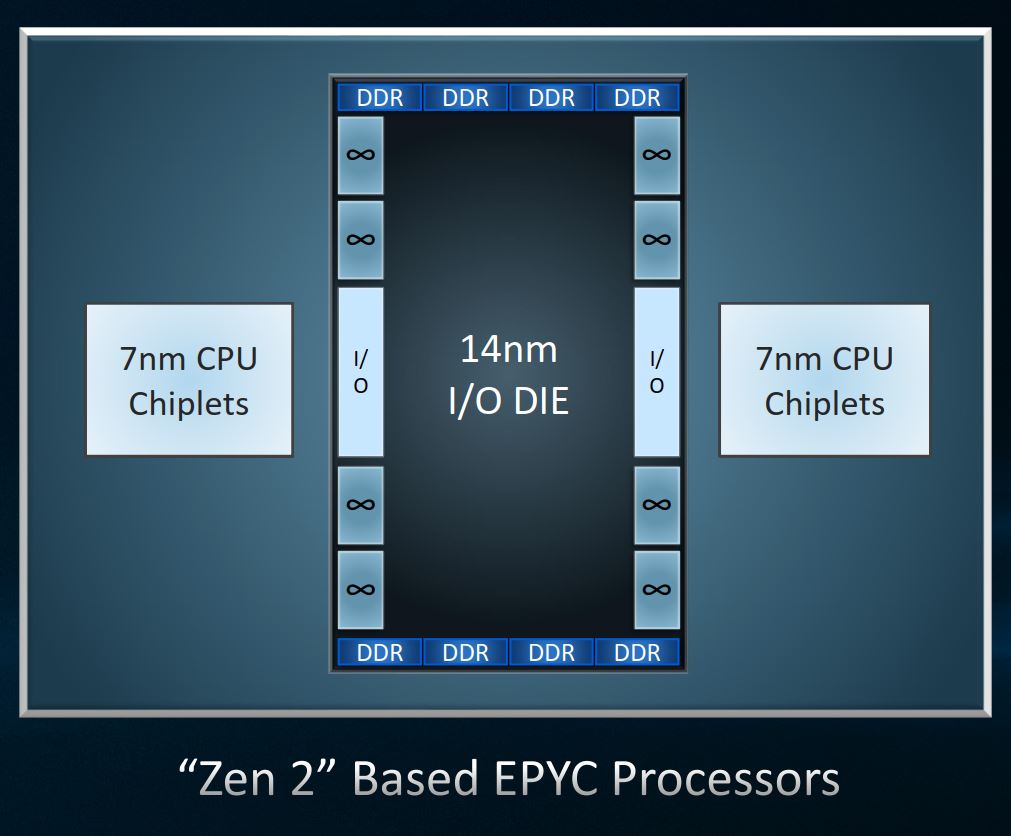

AMD's next-gen EPYC Rome processors come to market next year, and they bring an entirely new design that is even more disruptive than the first-gen EPYC Naples chips. AMD is now using the second-gen Infinity Fabric, which we expect to come with latency and bandwidth improvements, to connect a multi-chip design with a 14nm I/O die that serves as the linchpin of the design. That central chip ties together eight 7nm CPU chiplets, creating a massively scalable architecture.

Rome's DDR4 controllers are all attached to the central I/O chip. That will result in higher memory latency to all connected chips, but memory latency will be consistent for all compute chiplets (assuming perfectly linear data delivery across the fabric). That should be a major step forward for AMD to address concerns about performance variability.

But the 7nm CPU chiplets are all also tied to the central I/O chip, meaning that access between the caches on each chiplet could be even more challenging due to the extra hop between chips.

The new Linux kernel includes Zen 2 QoS (Quality of Service) extensions that monitor and govern the use of certain resources, such as L3 cache. That includes QoS domains that dictate L3 cache limiting, prioritization, and memory bandwidth enforcement. That should help prepare the broader software ecosystem for the new architecture and potentially sidestep some of the eccentricities of the new design.

This latest round of preparation comes on the heels of AMD's recent introduction of the new Zen 2 'znver2' compiler. The new compiler supports several new commands, such as Write Back and Do Not Invalidate Cache (WBNOINVD), Read Processor ID (RDPID) and Cache Line Write Back (CLWB), with the latter enabling support for NVDIMMs (Non-Volatile DIMMs). Surprisingly the new compiler doesn't support AVX512, but support for that, and more, can be added later.

In November, AMD also released a new temperature driver patch for Zen 2 processors, further setting the stage for its early silicon to land in the hands of its leading customers.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.