Arm Neoverse N1, E1 High-Performance CPUs Target Servers, 5G Networks

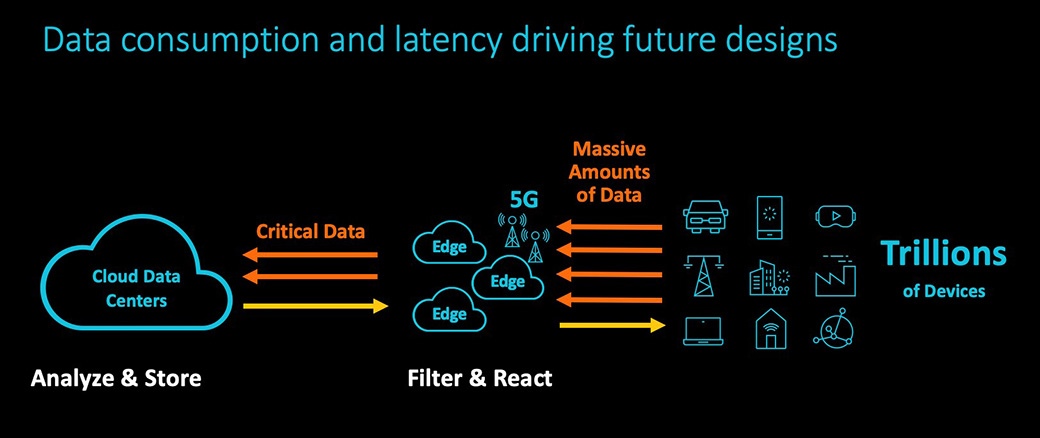

Arm announced today the first two chips for its Neoverse “cloud-to-edge” platform, the Neoverse N1 and Neoverse E1. The N1 is a high-performance processor meant to be used in the data center, while the E1 processor is focused on serving devices and equipment powering 5G networks. Through the Neoverse ecosystem, Arm is attempting to cover all of its customers’ data center and Internet of Things (IoT) needs, and the N1 and E1 CPUs are core to these solutions.

Neoverse N1, Arm’s Champion for the Server Market

Arm isn’t trying to shy away from the fact that the N1 is meant to steal market share from incumbent server chip leader Intel. It said that N1 will have competitive performance in the server chip market, while also delivering higher efficiency and a lower total cost of ownership (TCO). The TCO includes both the upfront cost of the chips and the cost to run and maintain said chips over their entire lifetime.

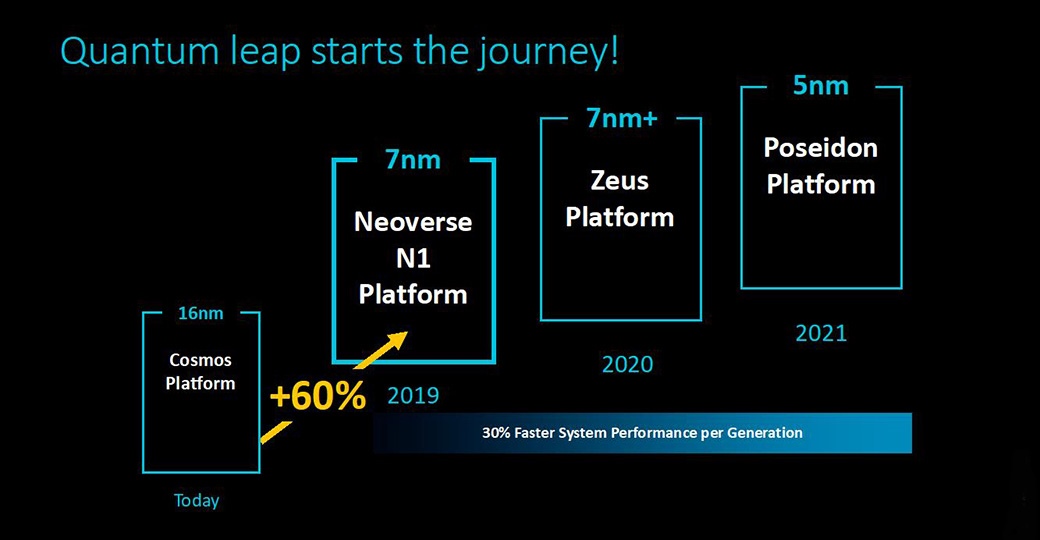

Arm claimed the Neoverse N1 is the first Arm platform to be designed from the ground-up for server infrastructure, while also committing to a roadmap that includes achieving more than 30 percent increase in performance each generation (every two years).

The company seems to have achieved that goal already with the N1, which shows over 60 percent improvement over the Arm Cortex-A72 architecture. Cortex-A72 started shipping in the beginning of 2016, and N1 chips or its variations should ship by the end of this year. Arm promised up to 2.5x server workload improvements compared to server chips based on the Cortex-A72 design. This large increase in performance is aided by a 30 percent increase in efficiency on the same process node, as well as from the switch to a 7nm process for N1-based silicon, versus the preceding 16nm.

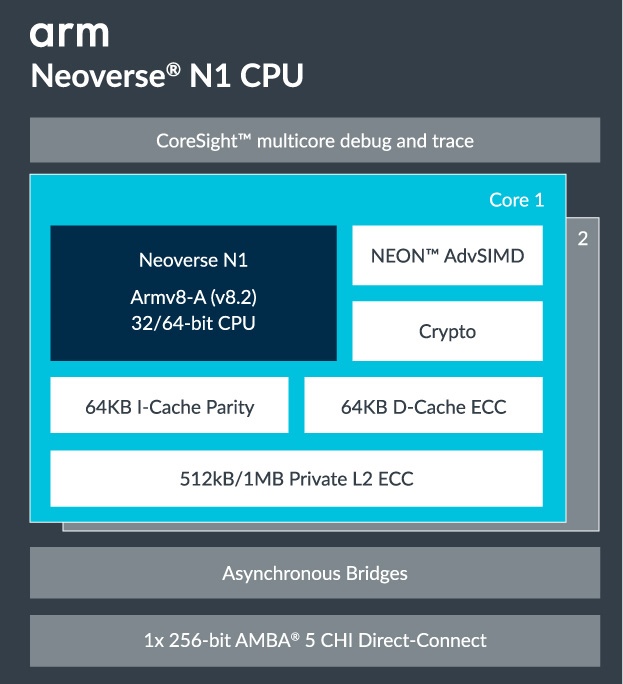

The N1 CPU has an 11-stage accordion pipeline that shortens in the presence of branch misses and lengthens in normal operation, thus acting like an accordion.

The processor comes with a 4-wide front-end, 8-wide dispatch/issue, three full 64-bit integer ALUs and a dedicated branch unit. The NEON Advanced SIMD pipeline is now substantially wider, too, enabling dual 128-bit load / store operations.

N1 was designed for 64+ core systems but can still be scaled down to 8 cores in edge designs. The company expects most system designs to have 64-96 cores at the high-end with 8-channel DDR4 RAM or 96-128 cores with 8-channel DDR5 RAM, with the latter still fitting into less than a 200W power envelope.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Neoverse E1 Targets the 5G Data-Heavy Infrastructure

Arm believes that the the global rollout of 5G wireless networks will require new infrastructure and a new class of compute capability to keep up with the rising data throughput demands.

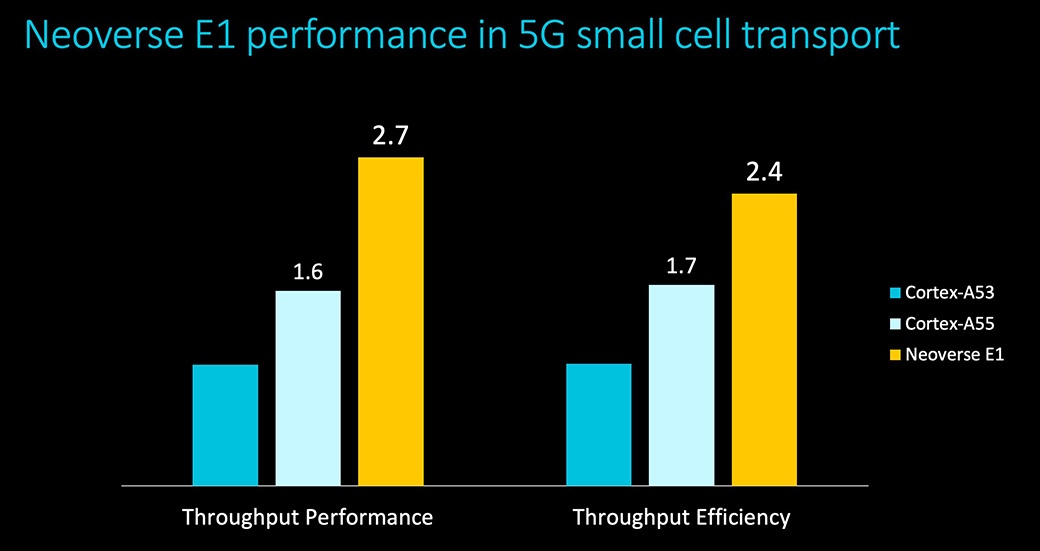

The Neoverse E1 chip is designed first and foremost to handle high throughput workloads, but high efficiency and performance were also big priorities for this design. According to the company, the E1 achieves a 2.7x throughput performance with 2.4x throughput-to-power efficiency and 2.1x compute performance over the consumer-focused Cortex-A53 CPU.

Arm noted that the ideal use-cases for the Neoverse E1 chip would be its use in 8-core Power-over-Ethernet (PoE) driven wireless access device or low-power 5G edge transport node. The systems could also scale up to multi-port 100Gbps devices, such as firewall appliances.

The company revealed that 70-80 percent of the processor cycles on a Cortex-A53 or Cortex-A55 are wasted on cache misses. This means the core is stalled waiting for data to become available. To fix this, Arm made the E1 CPU an out-of-order design and also added simultaneous multithreading capability to it. Both of these features led to a decrease in cache misses to just 30 percent.

With the N1 and E1, Arm seems poised to both launch a serious assault against Intel in the server chip market, as well as serve the global 5G ecosystem of the next decade.

Lucian Armasu is a Contributing Writer for Tom's Hardware US. He covers software news and the issues surrounding privacy and security.