ASML Predicts Processors with 300 Billion Transistor by 2030

The maker of semiconductor-making machines predicts wonderful innovations

ASML Holdings is responsible for designing and building machines that manufacture silicon chips, and if someone knows what the future holds, it is ASML. In a document aimed at investors, the Dutch company laid out plans to create processors that will feature over 300 billion transistors of logic by 2030. The company has stated that Moore's Law, an observation that the transistor count doubles every 18-24 months, is alive and well, despite many predictions that it is coming to an end.

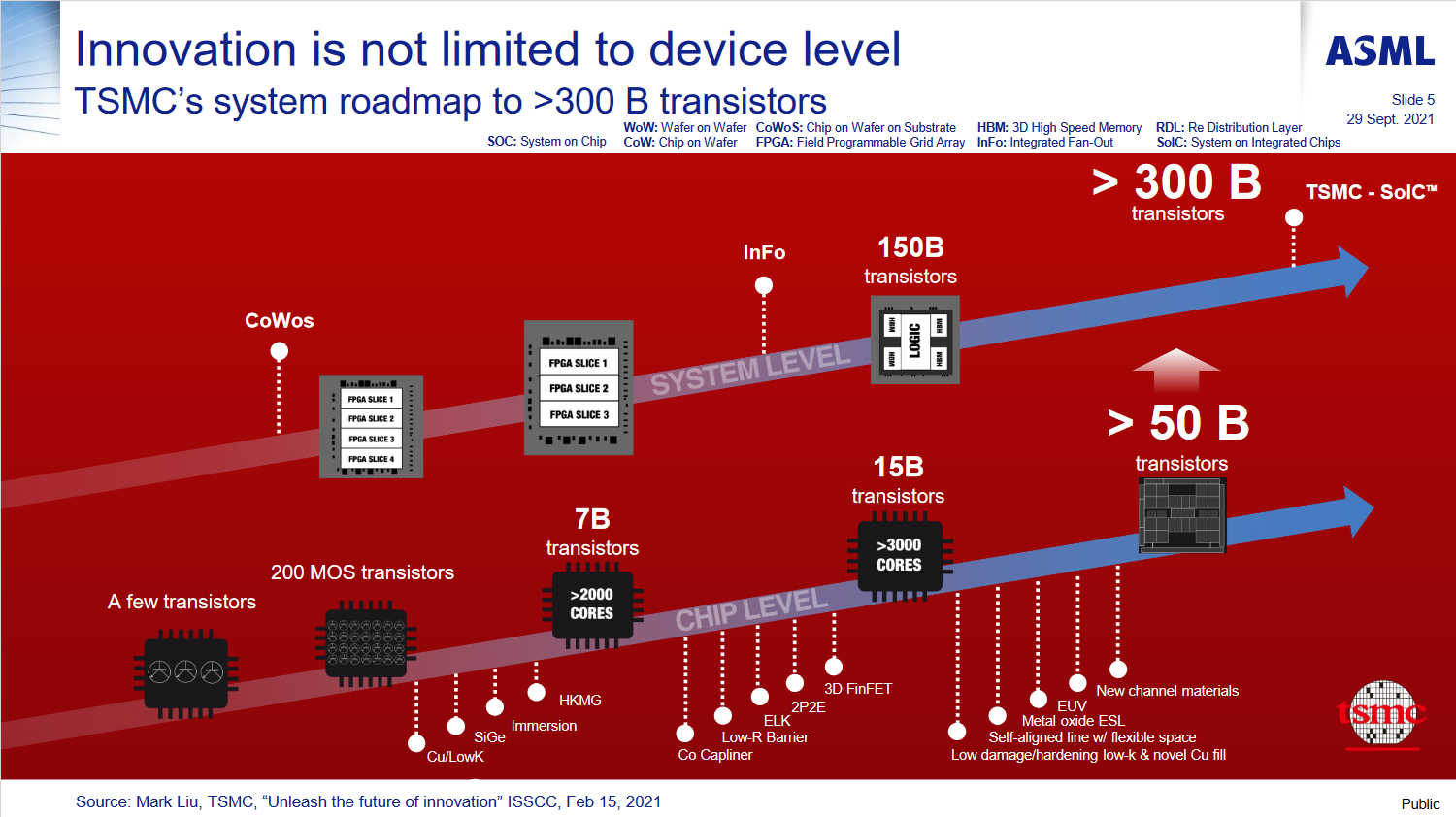

The company laid out plans to develop a chip that will incorporate over 300 billion transistors by 2030. Of course that is not an easy task since some chips like Nvidia's GA100 are massive and feature "only" 54 billion transistors. However, there is a solid foundation for the 300 billion goal. The company plans to achieve this by dividing the development process into two phases, the first for increased transistor density and the second is an improved packaging phase.

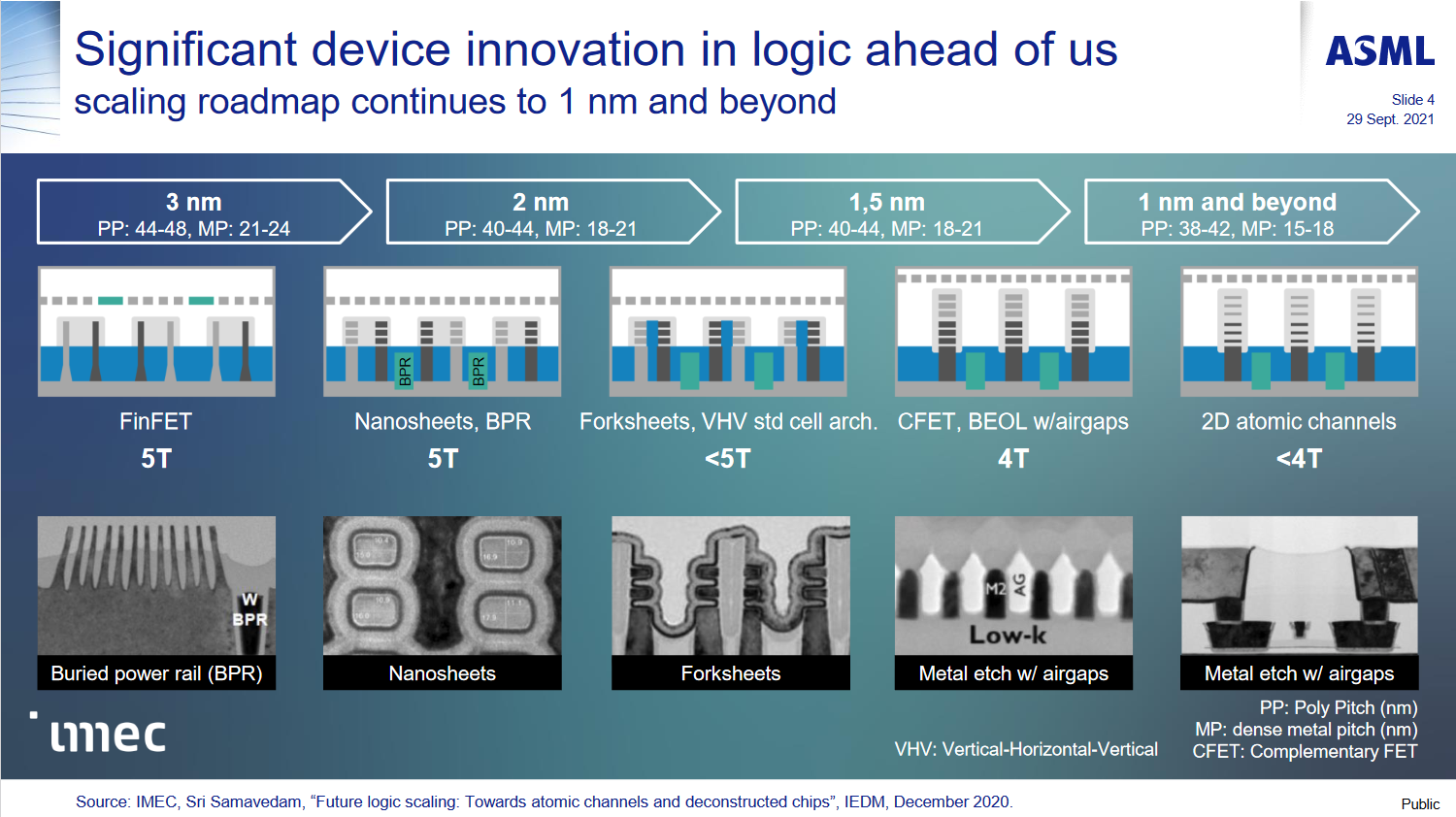

Each phase has its path, where the first one is transistor density. For nodes below the present 5 nm, like 3 nm and 2 nm nodes, the company wants to utilize nanosheet-FETs with the combination of extreme ultra-violet (EUV) lithography to manage to scale below the current point. After that, the road to the 1.5 nm node is challenging and requires forked nanosheets to work. And to achieve the 1 nm production, CFET is the technology of choice for new types of transistors. For sub 1 nm sizes, ASML will use 2D atomic channels.

With over 50 billion transistors becoming a standard for chips by 2030, ASML wants to deploy advanced packaging techniques to combine the chips and create multi-chip modules (MCM), resulting in a processor with over 300 billion transistors. 3D and logic stacking will play a significant role, alongside heterogeneous processor design and layered I/O systems.

When it comes to memory upgrades, the upcoming sets of techniques will enable memory makers to create NAND Flash modules with more than 500 layers by 2030. For reference, the current NAND Flash modules ship with 176 layers at the time of writing.

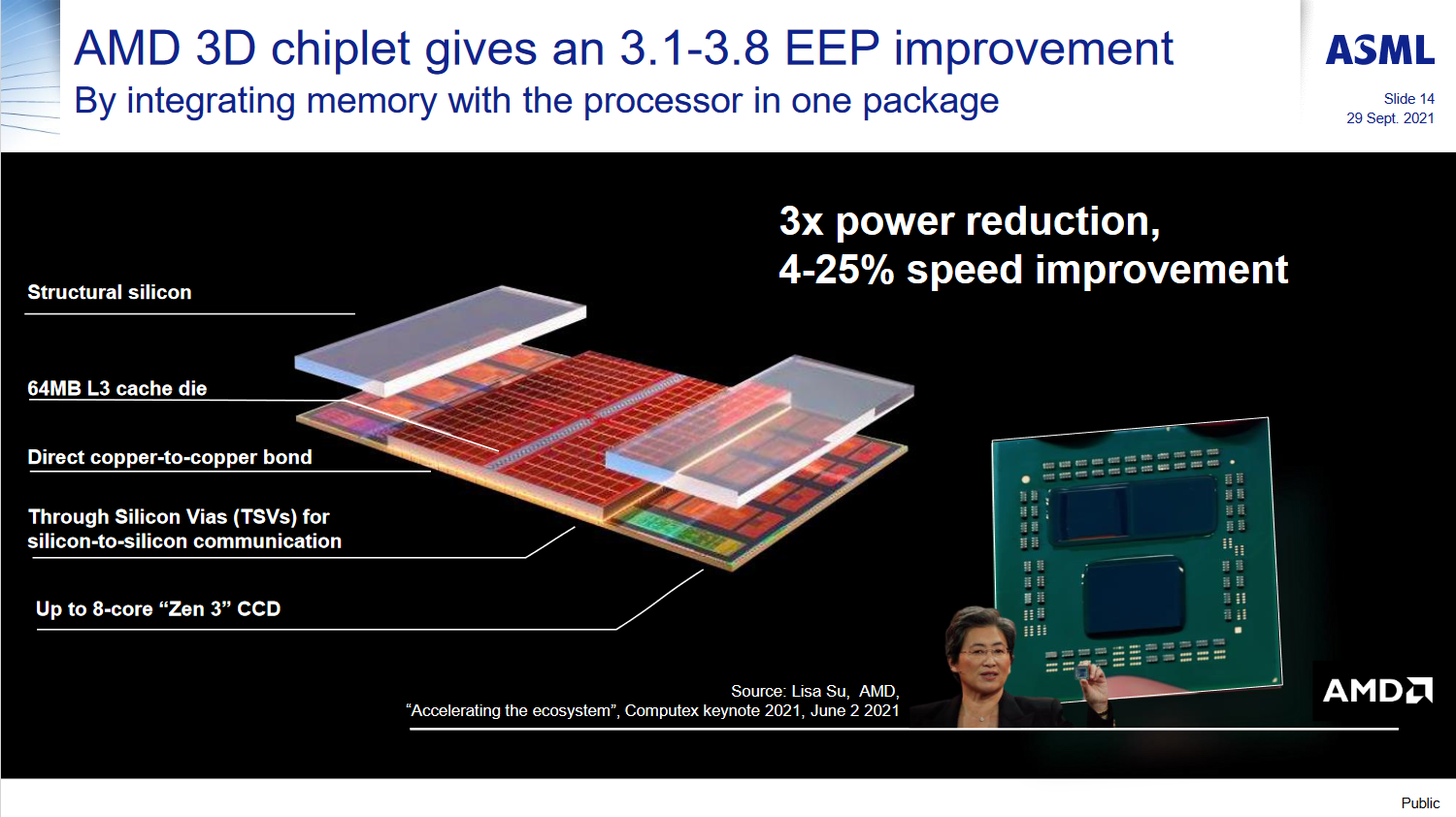

Every company working with silicon is included in the advancement of Moore's Law, as companies collaborate to design and manufacture the best possible silicon chips out there. TSMC and AMD are on the verge of utilizing advanced packaging and stacking technologies as the two have made structural silicon with extra memory stacked on top of the logic.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.