New 'Gen-Z Consortium' Announces Interconnect Technology Optimized For Next-Generation 'Storage Class Memory'

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

A group of technology companies that includes AMD, ARM, Dell EMC, IBM, HPE, Micron, Samsung, Seagate, SK hynix, Western Digital, and others, created the Gen-Z Consortium to develop and commercialize a new bus interconnect technology that’s optimized for next-generation fast storage technology. Intel doesn't appear to be part of the consortium as of right now.

Architects built today’s computer designs around the idea that storage is slow and persistent, while memory is fast and volatile. However, as we’ve already seen with Intel and Micron’s 3D XPoint technology, new storage technologies are starting to appear that can work as both high-performance storage and non-volatile memory. That means previous architectural assumptions that have worked in the past are no longer optimal for future use-cases.

"The increased computing demands of artificial intelligence, machine learning, advanced analytics and other Cognitive Era workloads requires greater hardware performance and innovation," said Brad McCredie, Fellow and Vice President of POWER Development at IBM."This increased demand, combined with the reduction in benefit from Moore's Law, calls for a new set of open standards. The combination of system-level acceleration via CAPI technology and now datacenter rack-level acceleration with Gen-Z can enable the industry to deliver much-desired breakthroughs in data center technology," he noted.

Article continues belowWhy A New Bus Is Needed

According to the Gen-Z consortium, per-core memory bandwidth is declining while per-core memory capacity is flat. The number of cores in data centers continues to grow at a fast pace, and memory and bandwidth can barely keep up.

Data is also on an explosive growth path due to the rise of the “Internet of Things,” and the hardware resources limit how fast and accurately the data can be analyzed if they can't keep up.

"As the industry moves toward the 3rd platform new open innovations are required to enable infrastructure support of massive data, billions of IoT devices, and cloud native applications," said John Roese, CTO of the Infrastructure Solutions Group at Dell EMC. "Taking advantage of new storage class memories and enabling composability in a memory-centric way will be critical as the control plane shifts toward in-memory computing. Gen-Z is an open industry standard that enables these innovations. Dell EMC is excited to be part of the Consortium that is developing this groundbreaking open industry standard," he added.

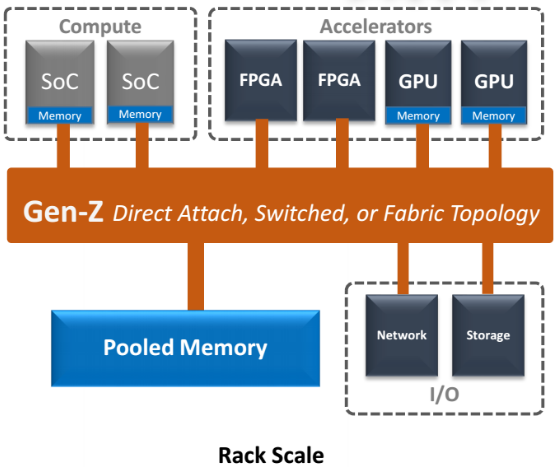

The consortium believes that an open architecture for a next-generation interconnect technology is necessary as memory tiers become increasingly more important. Rack-scale composability also requires a high-bandwidth, low-latency memory fabric. The Gen-Z protocol also promises to work with existing operating systems without changes, which should help increase adoption.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Memory/Storage Evolution In Systems

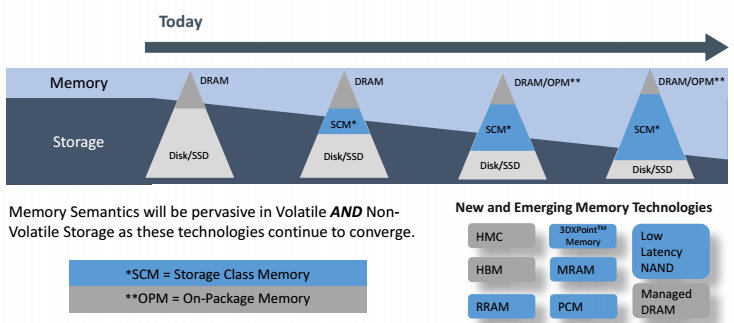

The consortium sees memory tiers evolving from being represented mainly by just a reasonable amount of RAM and a high amount of SSD/HDD storage to using little RAM in combination with faster on-package memory (OPM) and a small amount of SSD/HDD storage. “Storage class memory” (SCM) would represent the bulk of storage/memory.

Memory-Speed Communication

The Gen-Z fabric protocol will be “memory-semantic,” which means it will handle all communications as memory operations, such as the load/store, put/get, and atomic operations normally used by the CPU.

Memory semantics are optimal at sub-microsecond latencies from CPU load command to register store, unlike storage access that is block-based, uses interrupts, and is managed by complex software stacks.

Gen-Z Fabric Benefits

The Gen-Z consortium designed the fabric protocol to offer three main benefits.

1. High-Performance/Low-Latency

The Gen-Z protocol has high-performance with support for hundreds of GB/s bandwidth and low sub-100ns latency. It also supports simple read/write memory-semantic operations.

2. Advanced Workloads And Technologies

The new fabric protocol allows real-time analytics, enables data centric and hybrid computing, supports scalable memory pools for in-memory applications, and it can abstract the media interface from the SoC to unlock new media innovation.

3. Compatibility/Security

The new protocol promises secure end-to-end connectivity from one node to another, even at rack scale. The protocol has high software compatibility as it won’t require OS changes, and users can implement the technology economically.

The Gen-Z protocol doesn’t have a release date yet, but the consortium said it would be available free of charge for everyone.

Lucian Armasu is a Contributing Writer for Tom's Hardware US. He covers software news and the issues surrounding privacy and security.

-

jasonf2 I applaud this development. Intel with it's xpoint and chip-set marriage was setting the stage for a high margin nightmare. Remember RIMMs. This will set the stage for a universal standard that will allow for reasonably low cost access to nv memory. This will probably be the death blow for PCI though.Reply -

Xajel So They're creating a standardized version of NVLink, I think Intel might enter later... and maybe NV later, much later...Reply -

Xajel So They're working on a standardized competitor to NVLink, expect Intel to join later... and NVIDIA might join much, much later...Reply -

josejones "Intel doesn't appear to be part of the consortium as of right now"Reply

Will Intel join at some point or is that a definite no? We need to know. And when will this be available on motherboards and which ones? I hope this doesn't take 10 years to be released. -

IndignantSkeptic Why Is there there no mention of Nantero? They are making hard disks, solid state drives, and RAM obsolete with one device.Reply -

memadmax Intel and microsoft have teamed up to corral us into a closed system.Reply

Microsoft says Win10 will only support kaby lake...

That means intel has to be the one that puts in the hardware to close it...

Total BS.

Gen-Z is the savior of the PC industry. -

bit_user Reply

CAPI, perhaps. But I don't see PCIe going away, anytime soon. I expect to see v4.0 devices, next year. CAPI is only about 50% faster than that, from what they've said. I actually like PCIe, except that v4.0 seems to have gotten slow-walked.18717222 said:This will probably be the death blow for PCI though.

OMG. You have it completely backwards. They said they'd only add Kabylake support to Win 10. Win 10 supports lots of older CPUs, and even ARM-based Raspberry Pi!18731663 said:Microsoft says Win10 will only support kaby lake...

That means intel has to be the one that puts in the hardware to close it...

Total BS.

Gen-Z is the savior of the PC industry.

As for Gen-Z, this is aimed mostly at the datacenter. Perhaps it'll trickle down to the PC, but that's not where they're aiming.

If you read the article, it talks about rack-level aggregation of storage-class memory. What they're after is the ability to pool nonvolatile memory and have various chips in all the boxes within the rack gain access to it as if it were local.

And even though they say the software can treat it naively, I think 1 microsecond is a long time to wait for a cache miss. I could see the OS swapping to non-nonvolatile memory, or snapshotting application/VM state, for instant recovery in the event of hardware failure.