IBM Files Patent For Power Delivery via Heat Sink

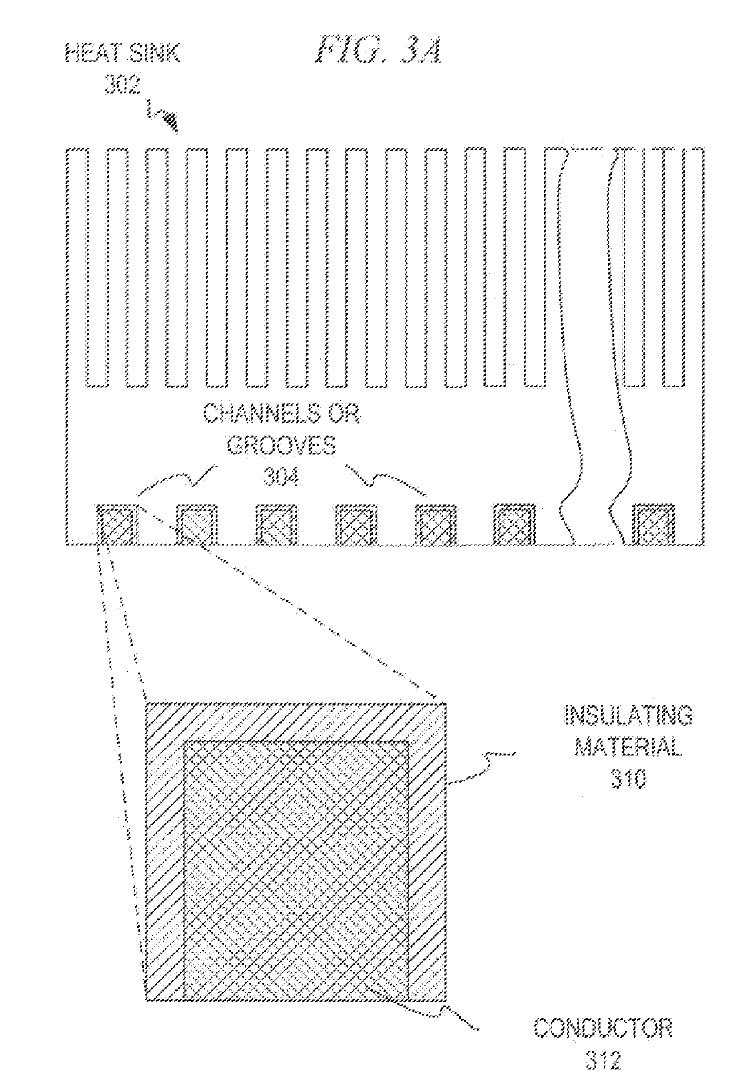

IBM envisions that future processors will be powered not only through single-surface power connectors, but through multiple interfaces, especially via grooves etched into the heat sink that sits on top of a CPU.

The motivation of this move is based on the fact that an increased number of CMOS transistors in 3D stacking will create an environment in which there will not be enough C4s even for single-die processors with single-surface power delivery.

IBM submitted a patent application that describes an integrated power architecture and distribution between a processor layer that is "coupled to a signaling and input/output (I/O) layer via a first set of coupling devices and a heat sink coupled to the processor layer via a second set of coupling devices."

The company stressed that this specific application only relates to power delivery, but there was the notion that this approach could also be used as a future data path as the described C4 layer "provides power to high-speed signaling" and the "I/O layer provides connectivity for signaling between [the] high-performance high-power processor layer [and] I/O layer in a reverse fashion similar to the […] description for power delivery from one layer to another layer."

Article continues belowGet Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Douglas Perry was a freelance writer for Tom's Hardware covering semiconductors, storage technology, quantum computing, and processor power delivery. He has authored several books and is currently an editor for The Oregonian/OregonLive.

-

illfindu So clearly IBM is so much smarter then me its crazy but does any one else think its kinda a silly idea i mean electricity running through metal makes head and heat sinks are suppose to expel heat from the cpu heat. Im sure they can make it work but seems like a odd ideaReply -

tongouch Don't aim for success if you want it; just do what you love andReply

believe in, and it will come naturally.

-

syrious1 ReplySo clearly IBM is so much smarter then me its crazy but does any one else think its kinda a silly idea i mean electricity running through metal makes head and heat sinks are suppose to expel heat from the cpu heat. Im sure they can make it work but seems like a odd idea

I was thinking the same thing. doesn't this go against the purpose of a heatsink, which is to expell heat not conduct it into channels

-

InvalidError illfinduSo clearly IBM is so much smarter then me its crazy but does any one else think its kinda a silly idea i mean electricity running through metal makes head and heat sinks are suppose to expel heat from the cpu heat. Im sure they can make it work but seems like a odd ideaUsing the heatsink to provide DC ground makes perfect sense since the heatsink has a whole lot more metal and hence lower electrical resistivity and I2R losses than fine traces on the CPU die, solder balls, substrate, socket pins and PCB traces which could significantly reduce DC power losses there. This would make it possible to eliminate ground pins used mainly to provide DC ground but some ground pins would still be required for AC components that still require a low-impedance path with minimal loop surface area with power/IO traces to keep EMI and AC ripple on supply rails within tolerances.Reply

Going beyond that to squeeze IO interfaces between heatsink fins/CPU however seems a little extreme and very inconvenient since it would require the use of complex heat-spreaders or sticking the CPU between a top and bottom substrate which would be problematic for heat flow. Integrating signal traces in grooves under the heatsink would require precision alignment with the CPU, which may be a little too much for DIY, it would also make usage of thermal paste a lot trickier.

So, I doubt using the heatsink as a signal carrier beyond complementary DC ground would be practical. -

digiex This will be good for embedded processors where the heat sink is permanently in place.Reply

For removable heat sinks, a precise aligner is needed. -

Netherscourge Not very practical in a typical DESKTOP environment.Reply

In a MOBILE/TABLET/LAPTOP/SMARTPHONE environment, where circuit board real estate is scarce, it's VERY practical.

Using a Heatsink as a conduit for the purpose of space-saving is quite genius to be honest. In fact, I'd go ahead and patent it's use as a data pathway also - because the smaller these devices get, the more creative/alternate routes become important. -

madooo12 a heatsink is hot, it has a much higher resistance, so it would conduct electricity worse and generate less heat, maybe I'm missing something hereReply -

They should harness the energy from the heat output of today's CPUs and GPUs and power the rest of the system with it.Reply