Intel Powers On Sapphire Rapids Processors, Scheduled for 2021

DDR5 and PCIe 5.0 come in 2021

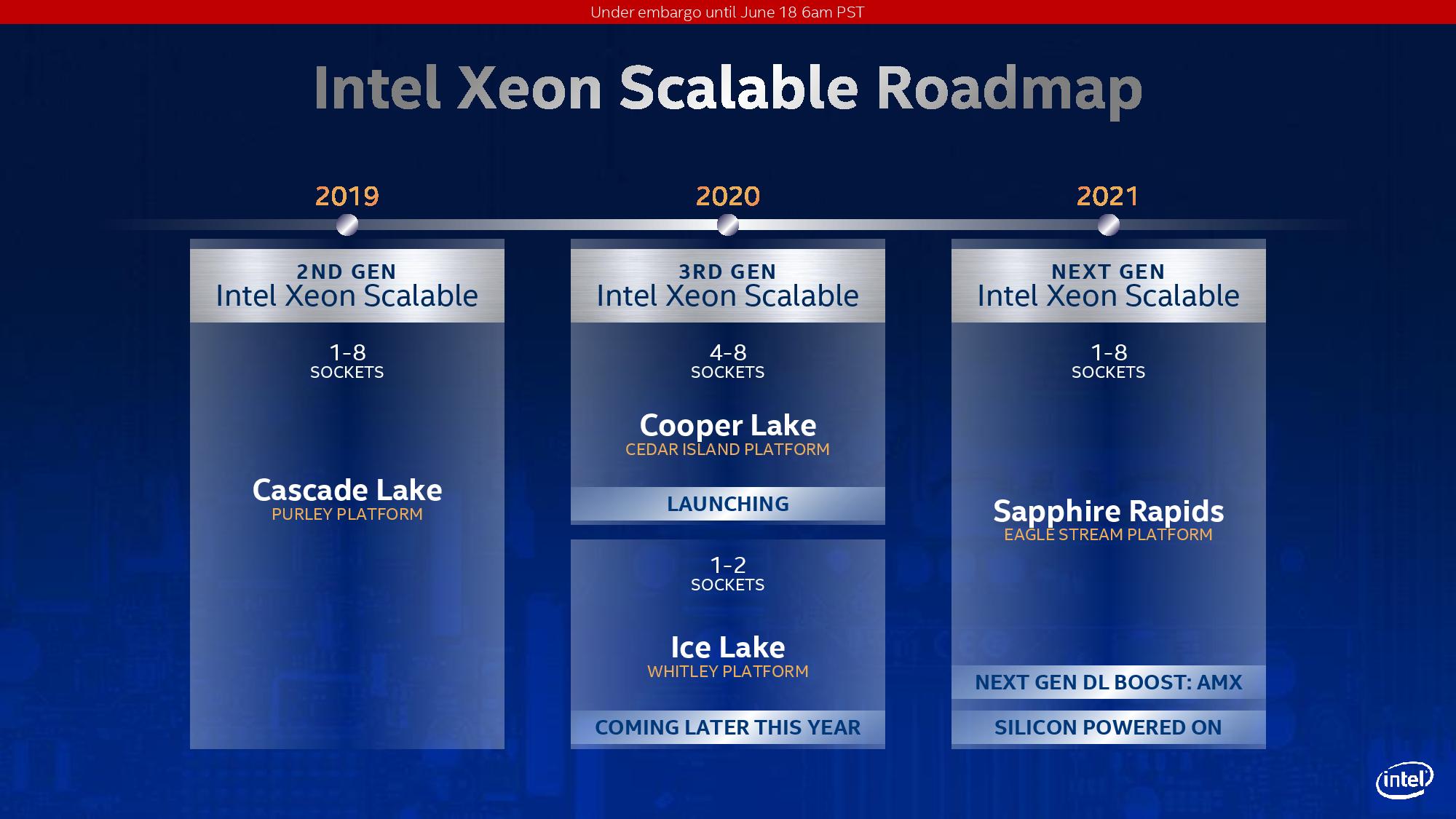

As part of Intel's Cooper Lake launch, the company shared a few details surrounding its upcoming Sapphire Rapids data center processors and also teased its new AMX technology.

Lisa Spelman, Intel's Vice President and General Manager of Intel's Xeon products, announced that the company has finished its first power-on of the company's forthcoming Sapphire Rapids processors. These processors are slated to arrive in 2021 and will re-unify Intel's Xeon stack into one family that addresses servers that span from one to eight sockets. In the interim, Intel will split its Xeon lineup between Cooper Lake processors that address four- to eight-socket systems, and Ice Lake processors for one- and two-socket servers.

Intel also disclosed that the Sapphire Rapids processors support Intel Advanced Matrix eXtensions (AMX) that are targeted at improving performance in training and inference workloads. Intel hasn't shared the details surrounding AMX yet, but says the specification will be published later this month.

Huawei inadvertently posted a presentation outlining a few key Sapphire Rapids specifications last year, including that the processors will support eight-channel DDR5 memory and PCIe 5.0 support. It's important to remember that early specifications can change as the product works its way to market.

Intel's Sapphire Rapids processors will join Intel's forthcoming Ponte Vecchio Xe graphics cards to power the Aurora Supercomputer that is slated to come online in 2021 at the Argonne National Laboratory.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

Deicidium369 "It does appear, though, that the Sapphire Rapids chips will be the first general-purpose data center processors from Intel that will propel the company beyond its support for the PCIe 3.0 interface"Reply

Really? So Sapphire Rapids coming out BEFORE Ice Lake SP? Ice Lake SP has 64 PCIe4 channels in a single socket config, and 128 PCIe4 channels in dual socket - the same # as Epyc.

"That will address a weakness that Intel faces against AMD's PCIe 4.0 EPYC Rome processors that are already on the market"

Niche market at best - Intel Whitley will be mass market and will usher in mainstream PCIe4 usage. -

vinay2070 I finish reading the article and scroll down to the comments section, just when I start reading the comments, they move down because of some other links start popping up in place. Then you have to start scrolling down with uncertainity not knowing how long you have to scroll down. If there are no comments or a single liner comment, you might miss when scrolling down and then you keep wondering where the heck are the comments. What a mess! Whoever designed this site, didnt make it user friendly. They just want users to go elsewhere and read.Reply -

JayNor AMD's proposal for every solution has been more hammers. Perhaps in zen4 we'll see avx512, but now we learn Intel will implement matrix operations on the CPU in the same timeframe ... It appears AMD is willing to let Intel lead the way on the new features.Reply

Conversely, Intel hasn't countered with a 64 core server chip of their own. They seem to be content with providing 4 and 8 socket solutions, and can bundle that with Optane DIMMS for huge memory solutions. Lisa Spelman's video today had a slide showing over 270 design wins advancing to production for Optane ... which also implies Intel Server chips. AMD has no answer. -

Deicidium369 Reply

Well, AMD has been destroying Intel for going on 30 years now - and while x64 was great - how long ago was that? Intel leads, AMD tries to follow.JayNor said:AMD's proposal for every solution has been more hammers. Perhaps in zen4 we'll see avx512, but now we learn Intel will implement matrix operations on the CPU in the same timeframe ... It appears AMD is willing to let Intel lead the way on the new features.

Conversely, Intel hasn't countered with a 64 core server chip of their own. They seem to be content with providing 4 and 8 socket solutions, and can bundle that with Optane DIMMS for huge memory solutions. Lisa Spelman's video today had a slide showing over 270 design wins advancing to production for Optane ... which also implies Intel Server chips. AMD has no answer.

Well the shipping non existent 10nm has been available for purchase in premium devices for going on 9 months now - and Intel will deliver Tiger Lake premium designs around October - just like Ice Lake did a year before. and the non existent 10nm+ will give us 38C Ice Lake SP with upto 128 PCIe4 lanes in a dual socket system... at some point this year the nonexistent 10nm+ will also deliver a desktop GPU and a compute focused GPU for data centers - and that's just Xe HP - not even a pale shadow to Xe HPC. Amazing how much revenue will be made by selling all those nonexistent 10nm products.

The 900# Gorilla has woken up and doesn't like seeing a Capuchin monkey in it's cage. The window for AMD to capitalize on the 900# Gorilla being docile is over.

I can hear them now - I am too optimistic about Intel - that AMD something something profit... -

bit_user Reply

To paraphrase the saying: "don't count your chips before they've launched."Deicidium369 said:Intel will deliver Tiger Lake premium designs around October - just like Ice Lake did a year before. and the non existent 10nm+ will give us 38C Ice Lake SP with upto 128 PCIe4 lanes in a dual socket system... at some point this year the nonexistent 10nm+ will also deliver a desktop GPU and a compute focused GPU for data centers - and that's just Xe HP - not even a pale shadow to Xe HPC. Amazing how much revenue will be made by selling all those nonexistent 10nm products.

Ice Lake SP is how many years late? And still not out?

It might've woken up, but hasn't even gotten out of bed, yet.Deicidium369 said:The 900# Gorilla has woken up and doesn't like seeing a Capuchin monkey in it's cage. -

bit_user Reply

Um, "more hammers" would be an apt description of how Intel keeps trying to pack its CPUs with features to compete with GPUs. I was moved to groan, at the mention of AMX.JayNor said:AMD's proposal for every solution has been more hammers. Perhaps in zen4 we'll see avx512, but now we learn Intel will implement matrix operations on the CPU in the same timeframe ... It appears AMD is willing to let Intel lead the way on the new features.

They never learn, it seems. ...even after buying three different AI chip makers (Movidius, Nervana, and Habana Labs) and launching an indigenous dGPU effort! -

jeremyj_83 Reply

The "up to" is the most important part in that entire statement. That means there will be varieties that will not support 64 lanes/CPU. If you need more lanes you have to spend a lot more on the CPUs or get more cores that you need. I wouldn't be surprised if Intel goes and keeps the 64 lane variants for the Platinum only, Gold 48, Silver 36, and Bronze 24. Would be a great way for them to force people to buy more CPU if they need more IO.Deicidium369 said:and the non existent 10nm+ will give us 38C Ice Lake SP with upto 128 PCIe4 lanes in a dual socket system -

bit_user Reply

Or, how about the part where Intel is putting a <= 38-core/64-lane part against a 64-core/130-lane CPU?jeremyj_83 said:The "up to" is the most important part in that entire statement.

Good luck with that, Intel. If Ice Lake SP were half as good as @Deicidium369 makes them sound, Nvidia would've surely used them in the DGX A100. -

TerryLaze Reply

Nobody design CPUs for you, or me, or any one of us.bit_user said:I was moved to groan, at the mention of AMX.

They never learn, it seems. ...even after buying three different AI chip makers (Movidius, Nervana, and Habana Labs) and launching an indigenous dGPU effort!

For intel to put this in they had enough demand for it from their customers.

This is how intel sells everything they can produce. -

bit_user Reply

I'm not even talking about me. I'm talking about AVX-512 being a bad move for them, and they're just continuing the trend with AMX.TerryLaze said:Nobody design CPUs for you, or me, or any one of us.

How do you even know that? Do you work there?TerryLaze said:For intel to put this in they had enough demand for it from their customers.

I don't think it came out of nowhere, but it's one thing to see a market need for matrix arithmetic acceleration, and another thing to decide it belongs in a CPU.

Oh, you mean like Xeon Phi? No, Intel is not perfect. Sorry to show you the hard truth.TerryLaze said:This is how intel sells everything they can produce.

Intel is still acting like x86 CPU is the best solution to all problems, in spite of what the Phi showed them.

You're confusing strong financial results with sound strategy. Back in 2000, there were a lot of tech companies that did phenomenally well, just by being in the right market at the right time. Good fortune can cover for a lot of strategic and tactical missteps.