Intel Process Roadmap Shows 1.4nm in 2029, Two-Year Cadence (Updated)

In Moore we trust

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Update 12/11/2010 7:40am PT: Intel tells us that the roadmap ASML presented at the IEDM conference (cited in our coverage below) was altered by ASML and doesn't accurately reflect Intel's public roadmap. Intel's version of the roadmap, which we're presenting below, does not have node naming conventions listed beyond 10nm+ and is "meant to be read more generally." We've included Intel's public roadmap immediately below, and ASML's version of the roadmap follows.

Original Article:

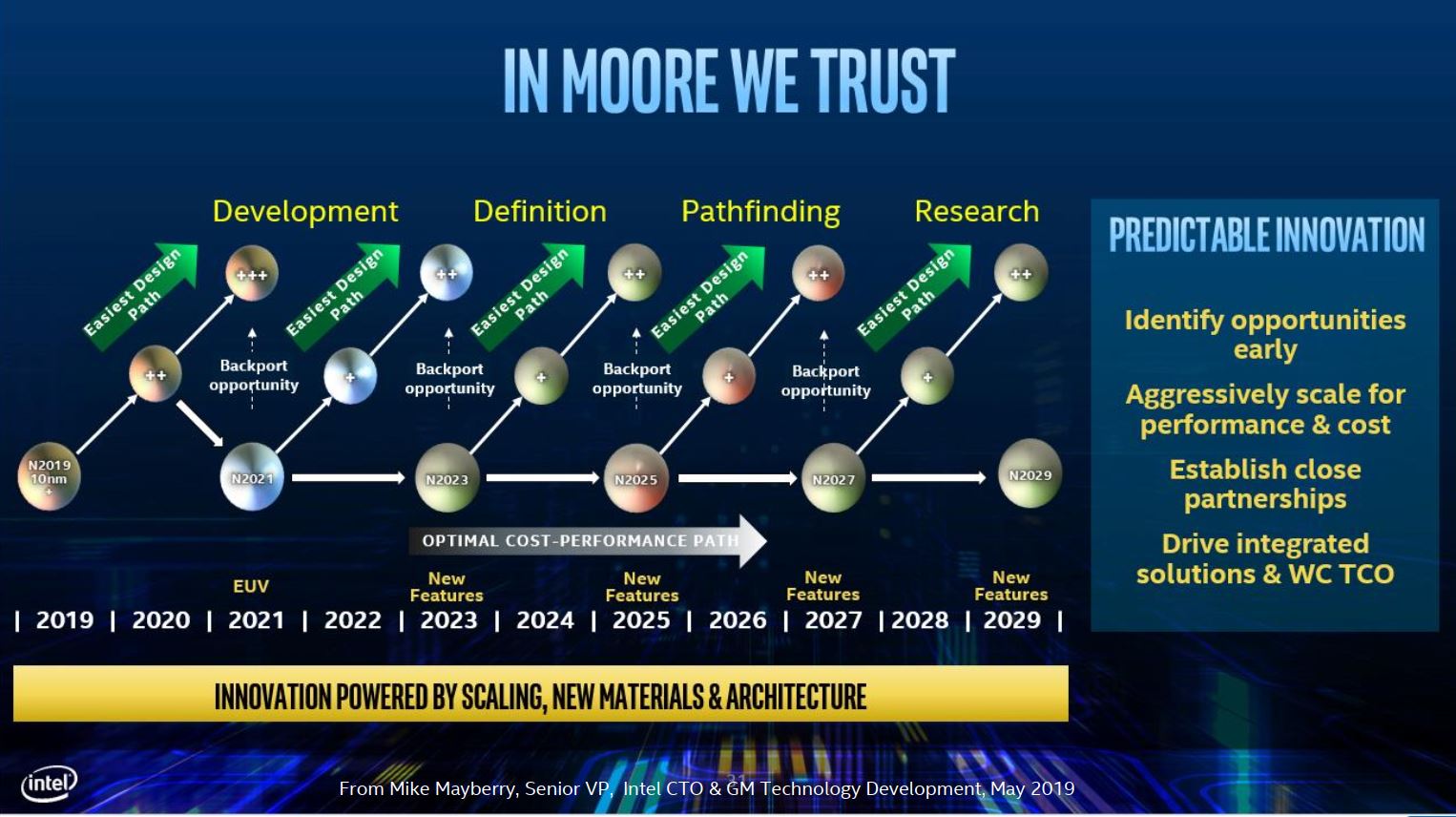

An Intel process technology roadmap has surfaced (reported by WikiChip) that sees Intel introducing a new process every two years for the next decade, resulting in the 1.4nm node in 2029. There will also be two additional intra-node optimizations per node, with a 10nm+++ in 2021.

The roadmap was shown in an ASML presentation at the ongoing IEDM 2019 conference and it dates back to a September Intel presentation. It shows 10nm in 2019, 7nm in 2021 and 5nm in 2023, respectively in development and in definition. In October, Intel announced its intention to move back to a two to two and a half year cadence and stated its confidence in 5nm.

The roadmap then reveals that Intel has 3nm and 2nm in pathfinding and 1.4nm in research. It is the first time Intel has disclosed that it is working on those nodes. The timespan between all nodes is roughly two years, placing 3nm in 2029. However, since 7nm is slated to launch in the fourth quarter of 2021, any small delay in the next decade would let 3nm slip into 2030 or beyond.

The roadmap does not reveal any details about Intel’s process technology plans, other than saying that each node would be the optimal cost-performance path and introduce new features. For 7nm, that means the insertion of EUV. For 5nm, it is expected that Intel will move from tri-gate FinFETs to gate-all-around nanowires, possibly followed by stacked nanowires at later nodes. Intel is likely also aiming to use next-generation high-NA EUV lithography at 5nm: Intel's lithography director recently held "a call to action to keep high-NA EUV on track" for its 2023 schedule, according to SemiEngineering.

As Intel announced at its investor meeting this year, the company will continue the practice it started at 14nm to introduce intra-node process optimizations (denoted as '+' revision), which are described as the easiest design path. (Except for 10nm, where 10nm++ leads to 7nm in the slide instead of 10nm.)

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

10nm+++

Interestingly, at the 10nm node, the roadmap shows a path towards a ++ and a +++ version, instead of the expected 10nm+ and 10nm++. It is unclear if Intel has renamed the nodes that were previously announced as 10nm+ and 10nm++, or if Intel has developed a fourth variant of 10nm. The EUV sign above 2021 could indicate that 10nm+++ leverages EUV.

Back Porting

Lastly, every node shows a back port opportunity to the previous node’s ++ version. This could either refer to the back porting of new processes' features to old processes, or alternatively, back porting full chips to the previous node. Intel disclosed a year ago that it would be more flexible with what nodes its IP could be manufactured on, as it admitted that its 10nm IP was bottlenecked by the process' delay.

The roadmap does not show if 10nm too has the option for a backport.

Closing Thoughts

If Intel’s process roadmap holds true, then Moore’s Law will live on for at least another decade, rendering the increasing reports of its ending false for at least another decade. A 1.4nm node might have a density of 1.6 billion transistors per square millimeter. Although end products often have a density lower than theoretically possible, such a density would have let Intel fit as many transistors in a single square millimeter as there were in 2014's Broadwell 14nm lead product.

More realistically, though, the roadmap presents an optimistic schedule after the hiccups Intel had at 14nm and 10nm. A similar long term roadmap early this decade had shown 7nm as being scheduled for 2017. On the other hand, a full decade roadmap presents a bold sign that Intel is still serious about leading edge process technology and has confidence in Moore's Law.

This sentiment was echoed a few months ago by Intel's Jim Keller, who proposed a 50x scaling path that included feature size reduction, the introduction of stacked nanowires and 3D stacking.

Separately, at an investor conference today, Intel chief engineering officer Murthy reiterated that 5nm is well into development and on track for 2023. He also said that Intel intends to introduce a “full portfolio” of 7nm products within a year of its lead product. More closely, he stated that Tiger Lake would launch "in the early part" of next year.

-

Darkbreeze Assuming they can ever get to, or past, 10nm, while actually providing a SUPPLY. Oh, who are we kidding. They can't even hit the supply margins on the much easier 14nm process, how do we expect them to reach 1.4nm in the next 10 years when they've been trying to get past 14nm for 5 years already.Reply -

bit_user I'll believe this when it happens.Reply

I guess this was probably a leak, rather than an officially-released announcement, but Intel is currently at zero credibility on any manufacturing process improvements.

nterestingly, at the 10nm node, the roadmap shows a path towards a ++ and a +++ version, instead of the expected 10nm+ and 10nm++. It is unclear if Intel has renamed the nodes that were previously announced as 10nm+ and 10nm++, or if Intel has developed a fourth variant of 10nm.

Probably because the first-gen 10 nm was DoA. The 10 nm they're using for Ice Lake is already +. -

AnimeMania Intel forgot to mention that with each node change there is also a CPU socket change.Reply -

InvalidError Reply

There are fundamentally two reasons why Intel is behind on 14nm shipments, the first being sales of 14nm parts still growing faster than Intel can increase capacity, the other being 10nm being so many years overdue. If Intel ever manages to get its desperately needed 10nm breakthrough, it'll increase yield per migrated production line by 50+% and solve Intel's supply issues.Darkbreeze said:Assuming they can ever get to, or past, 10nm, while actually providing a SUPPLY. Oh, who are we kidding. They can't even hit the supply margins on the much easier 14nm process

We'll see how good 10nm is turning out when the promised desktop Ice Lake finally launches (or fails to) next year. Going to be quite the embarrassment should desktop Ice Lake either show similar clock frequency regressions as mobile parts have or gets delayed into 2021. My bet is on desktop Broadwell-II: technically exists but nearly unobtainable beyond select OEMs. -

Gillerer ReplyDarkbreeze said:Assuming they can ever get to, or past, 10nm, while actually providing a SUPPLY. Oh, who are we kidding. They can't even hit the supply margins on the much easier 14nm process, how do we expect them to reach 1.4nm in the next 10 years when they've been trying to get past 14nm for 5 years already.

You're stating them as if the 14nm shortage and troubles with 10nm development are two separate failures Intel has had, when in fact they're both one and the same.

Since they haven't been able to introduce new performance products on the 10nm node, their entire modern portfolio (down to chipsets - apart from a couple of variants reheated from the 200 to the 300 series, using 22nm) have been clogging the 14nm production lines.

There was no way for them to know to prepare for the multiple years' delay on the 10nm node, so building double the 14nm capacity from the start would have been seen as a bad investment; Had 10nm been on or almost on time, most of that capacity would have had too short a time to recuperate the investment costs (from use as a leading edge node for high-margin parts).

It seems even Intel sometimes fails to execute, but there is no reason to believe these troubles are anything but a fluke - they have billions to throw at R&D. If their original 10nm plans were - as some have postulated - too ambitious, I'm sure they've learned their lesson. -

InvalidError Reply

We'll see in due time. It is still perplexing how Intel has allowed itself to slip two years behind everybody else by focusing on 10nm DUV while nearly everyone else is switching to 7nm EUV. All of that research into extending DUV had better pay dividends going into EUV or 10nm++++ is going to turn into an unmitigated waste of time and money.Gillerer said:It seems even Intel sometimes fails to execute, but there is no reason to believe these troubles are anything but a fluke -

Bernardo Ortiz ReplyDarkbreeze said:Assuming they can ever get to, or past, 10nm, while actually providing a SUPPLY. Oh, who are we kidding. They can't even hit the supply margins on the much easier 14nm process, how do we expect them to reach 1.4nm in the next 10 years when they've been trying to get past 14nm for 5 years already.

Wrong question. Silicon crystalline spacing is ~0.5nm. This means 1.4nm is approximately 3 atoms wide. +/- 1 atom at least for over/under exposure. Does one have enough control of the process to do this? No longer dealing with bulk property equations, must treat atoms as point charges rather than uniform parallel plates. Much more complicated to properly define a transistor (computationally intensive). Even if you can build a transistor at this size, can you economically characterize the process and take this to high volume manufacturing?? You really need to be changing something other than drawn size to get more density! -

ingtar33 ReplyInvalidError said:There are fundamentally two reasons why Intel is behind on 14nm shipments, the first being sales of 14nm parts still growing faster than Intel can increase capacity,

and water is wet? isn't this the definition for lack of supply? The reality is intel has been super binning it's chips to produce those high clocks on 14nm, in fact they've been super binning since skylake, which means 14nm has always been short of supply because yield has been poor from the very beginning due to the extreme binning they're doing. Now that has improved as the revisions have come, but this shortage is due to the high clock speed demands corperate put on the company, not due to some increased demand for intel processors. call it an artificial shortage caused by 14nm binning. (source? friend who work in the intel fab here in arizona, they also have other information about upcoming nodes too)

InvalidError said:the other being 10nm being so many years overdue. If Intel ever manages to get its desperately needed 10nm breakthrough, it'll increase yield per migrated production line by 50+% and solve Intel's supply issues.

unlikely, 10nm was meant to compete with ARM, and when initially conceived was meant to be a low power low clock node with a nice IPC improvement, intel didn't expect AMD Ryzen to actually challenge them so they planned to launch on 10nm with roughly the same performance as skylake, just lower clocks. Ryzen blew up intel's plans for 10nm. It's not that the yields are poor on the node (they're not good mind you) it's that they're unable to clock the chips up much beyond 3ghz without dumping power into the chips, and due to the 3d design, the heat gets impossible to deal with long term. basically it's a node good for making mobile parts not HEDT chips.

InvalidError said:We'll see how good 10nm is turning out when the promised desktop Ice Lake finally launches (or fails to) next year. Going to be quite the embarrassment should desktop Ice Lake either show similar clock frequency regressions as mobile parts have or gets delayed into 2021. My bet is on desktop Broadwell-II: technically exists but nearly unobtainable beyond select OEMs.

intel already canceled 10nm icelake desktop chips. it will be a mobile chip only, their next two desktop chips will be yet more 14nm revisions (comet and rocket lake). The plan is for the Golden Cove revision to be on 7nm, and the first desktop node improvement since broadwell and 14nm. Now the plan for 7nm desktop is to release late 2021 to early 2022. the problem is 7nm is a hasty redesigned process, remember how intel was planning on 10nm being an ARM competitive process? well so was original 7nm. They've been redesigning 7nm from the ground up to compete again in HEDT and are on a rushed schedule, so no one knows how 7nm will work, but while certain segments of intel are really hopeful for the process the guys I know here are really skeptical as it's really being rushed right now as intel mostly has given up on 10nm and their original designs for 7nm. They don't think intel will completely right the ship until 5nm.

of course this is full speculation, but when you consider in 2021 AMD will be close to releasing on 5nm, and their 7nm will have been on the market for a year, intel will be really running hard to catch up even if 7nm works. -

InvalidError Reply

A lack of supply literally means the supply and the ability to increase it do not exist. Intel's supply does exist and it is being increased to offset delays. This is just a regular supply shortage from demand exceeding supply and likely continuing to do so until Intel catches up on process tech.ingtar33 said:isn't this the definition for lack of supply?

Intel is on-and-off about desktop Ice Lake. At first there was no announcement, then there were rumors, then Intel denied the rumors, then the rumors came on again with a possible launch in early 2020 and last I heard a month ago, Intel has confirmed desktop Ice Lake but no ETA nor specifics.ingtar33 said:intel already canceled 10nm icelake desktop chips.