Loongson Technology Develops Its Own CPU Instruction Set Architecture

The end of Arm, MIPS, x86, RISC-V in China?

Chinese processor developer Loongson Technology this week announced that it had developed its own CPU instruction set architecture (ISA), Loongson Architecture (LoongArch) that has nothing to do with architectures designed outside of China. Surprisingly, the first processors based on the new architecture have already been taped out and will be released commercially this year.

For many years Loongson's processors relied on different versions of the company's LoongISA architecture, which were subsets of the MIPS64 architecture. This approach allowed the company to maintain compatibility with software developed for MIPS64 (which includes software for supercomputers) and also introduce its own extensions to boost performance in modern applications.

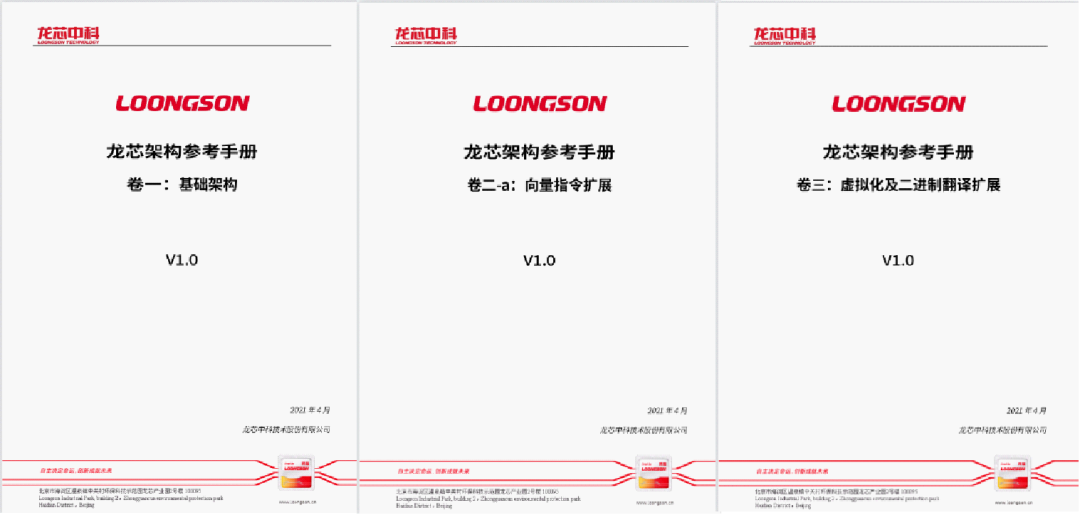

By contrast, LoongArch is said to feature almost 2,000 of proprietary instructions. Meanwhile, the company said that it had removed outdated instructions not suitable for modern hardware designs to ensure low power consumption and simpler designs. In addition to the base instruction set, LoongArch features binary conversion extension instructions (LBT), vector processing extension instructions (LSX), advanced vector processing extension instructions (LASX), and virtualization extension instructions (LVZ), reports PC Watch.

Apparently, the first CPUs to use the LoongArch are Loongson's quad-core 3A5000 for client PCs and 16-core 3C5000 for multiprocessor servers. Previously Loongson called these processors 'MIPS64-compatible', so they can execute programs originally developed for previous-generation Loongson processors that relied on a superset of the MIPS64 architecture. The Loongson 3A5000 is set to ship in the first half of 2021, whereas the 3C5000 is projected to be available towards the end of the year, according to a previous report.

Loongson Technology has released its LoongArch infrastructure instruction system manual to some interested parties for evaluation, but is yet to publish it for a broader audience of software developers. Also, the LoongArch is currently evaluated by the Chinese IP agency.

China has been striving for semiconductor self-sufficiency for years now and even created its Made in China 2025 program that set the time-frame by which this self-sufficiency is set to be achieved. Analysts are skeptical that China will be self-sufficient by 2025 as far as semiconductors are concerned, but the country is moving towards its goal.

A proprietary CPU ISA is certainly a step towards self-sufficiency as Loongson no longer has to rely on Arm, MIPS, x86, RISC-V or other Western processor architectures. However, only time will tell whether the company can actually develop a competitive ecosystem for its LoongArch.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

It is noteworthy that Loongson Technology has once announced plans to transit to open-source RISC-V, so if LoongArch fails, the company will have a plan B.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

setx Using RISC-V would be a nice move.Reply

Inventing their own ISA is only going to waste software development efforts. -

Pyrostemplar ReplyHowever, only time will tell whether the company can actually develop a competitive ecosystem for its LoongArch.

As if it mattered in China. The Party just needs to make it mandatory. -

hotaru.hino Reply

It's probably based on some existing ISA anyway and claiming it's some "brand new tech that will put the West to shame"setx said:Using RISC-V would be a nice move.

Inventing their own ISA is only going to waste software development efforts.

Also it's China. They're willing to go through the trouble of shifting map coordinates around so satellite imagery doesn't match up with road maps for "national security" -

shady28 "...it had developed its own CPU instruction set architecture (ISA), Loongson Architecture (LoongArch) that has nothing to do with architectures designed outside of China. "Reply

And we're supposed to believe that, why? -

InvalidError Reply

Putting together your own ISA is easy enough, the really tedious part is figuring out what instructions are most useful and performance-critical, most of which achievable by profiling software on existing architectures. The rest is mainly a matter of coming up with your own names, an efficient operation encoding scheme and operand packing formats, then plugging all of that into a cross-compiler such as a customized GCC to spit out native binaries.shady28 said:And we're supposed to believe that, why?

An ISA is just the instruction set with supporting architectural features such as the registers and flags instructions can access, it isn't tied to any particular implementation in software emulators, re-compilers, FPGA implementations, silicon, etc. Anyone can write a minimalist one on a napkin if they wanted to, that isn't the hard part. -

shady28 ReplyInvalidError said:Putting together your own ISA is easy enough, the really tedious part is figuring out what instructions are most useful and performance-critical, most of which achievable by profiling software on existing architectures. The rest is mainly a matter of coming up with your own names, an efficient operation encoding scheme and operand packing formats, then plugging all of that into a cross-compiler such as a customized GCC to spit out native binaries.

An ISA is just the instruction set with supporting architectural features such as the registers and flags instructions can access, it isn't tied to any particular implementation in software emulators, re-compilers, FPGA implementations, silicon, etc. Anyone can write a minimalist one on a napkin if they wanted to, that isn't the hard part.

You just spewed a bunch of garbage, you clearly don't know what an ISA is in this context.

Meanwhile "LoongArch" is turning out to be a modified MIPS64 ISA where they've merely renamed some of the instructions.

https://www.realworldtech.com/forum/?threadid=201588&curpostid=201593

By: Ariadne Conill (ariadne.delete@this.dereferenced.org), April 16, 2021 10:53 pm

"

I did some digging into this, as I maintain the MIPS64 port in Alpine, and was planning to target Loongson at some point.

From what I can tell, LoongArch is just a fork of the MIPS ISA, in a similar way to how MIPS32r5 and MIPS64r6 are backward-incompatible forks of the MIPS ISA. I conclude this based on the fact that LoongArch offers the same extensions that MIPS CPUs do, just with slightly different names, as can be seen in this translated press release. For example, what MIPS CPUs call the Virtualization Extension (VZ), LoongArch calls the LoongArch Virtualization Extension (LVZ). Another example is that the MIPS SIMD instructions (MSA) are renamed to LoongArch Vector Extension (LSX).

Specifically, I believe LoongArch to be a fork of MIPS64r6. " -

InvalidError Reply

There is no 'in this context' here, an ISA is just a set of definitions by definition. If China wants to rip off the open-source MIPS ISA and spare itself the trouble of writing their own together from scratch, more power to them.shady28 said:You just spewed a bunch of garbage, you clearly don't know what an ISA is in this context. -

ginthegit Reply

From what I am reading, i think Titan's understanding of the ISA is actually accurate. Considering that the x86 and x64 along with the RISC achitectures are essentally the same thing just with different register access and optimised coding for the CISC.shady28 said:You just spewed a bunch of garbage, you clearly don't know what an ISA is in this context.

Meanwhile "LoongArch" is turning out to be a modified MIPS64 ISA where they've merely renamed some of the instructions.

https://www.realworldtech.com/forum/?threadid=201588&curpostid=201593

By: Ariadne Conill (ariadne.delete@this.dereferenced.org), April 16, 2021 10:53 pm

"

I did some digging into this, as I maintain the MIPS64 port in Alpine, and was planning to target Loongson at some point.

From what I can tell, LoongArch is just a fork of the MIPS ISA, in a similar way to how MIPS32r5 and MIPS64r6 are backward-incompatible forks of the MIPS ISA. I conclude this based on the fact that LoongArch offers the same extensions that MIPS CPUs do, just with slightly different names, as can be seen in this translated press release. For example, what MIPS CPUs call the Virtualization Extension (VZ), LoongArch calls the LoongArch Virtualization Extension (LVZ). Another example is that the MIPS SIMD instructions (MSA) are renamed to LoongArch Vector Extension (LSX).

Specifically, I believe LoongArch to be a fork of MIPS64r6. "

As an engineer who can write in Assember code directly (albeit simple code), I find that the old ISA is weak and slow and needed optimisations. For example using the MOV instruction is lagely pointless as it is just a simple instruction to load a register or offload a register to some other entry, and largely is for structural and internal coding. Because Mov is requred and written so many times within each instruction (for any high level language like C and Java), it can be incorporated (as is done with CISC instructions) to be written out of the coding as it is implied when any other function like ADD or IF statement is used, and it can always be assumed that the working register is Ax. It means that a New ISA can completely disregard it as a call and each instruction is hardwired.

I have for a long time thought that there are many changes to the ISA which have been long awaited to make computers quicker and more efficient (in the same way that direct x 12 did to all its predecessors. -

setx InvalidError's position on the ISA is correct: it's trivial to create new ISA. But why almost no one does that? Because ISA without software for it is completely useless.Reply

It looks like they want to maintain some compatibility with MIPS with more extensibility:

Instruction encoding is totally different than MIPS (more instruction formats) but (almost) all MIPS instructions can be translated to exactly one LoongArch instruction.

So nothing outstanding from technical standpoint: not a breakthrough but also not a reinventing the wheel. -

ginthegit Replysetx said:InvalidError's position on the ISA is correct: it's trivial to create new ISA. But why almost no one does that? Because ISA without software for it is completely useless.

It looks like they want to maintain some compatibility with MIPS with more extensibility:

So nothing outstanding from technical standpoint: not a breakthrough but also not a reinventing the wheel.

It is a shame really, Making a new ISA would be an excellent idea to reduce the ability of hackers, and also reduce calls and latency. If an new internal registry system were to be built, an optimised ISA could be a game changer for Speed and process. It is the Whole idea of the advantages of CISC over RISC so why not.

Compatibility with other ISA is not really necessasy if you create a compiler that can optimise the new code to be translated from the old code.

Its something I dont understand. To get old programs to work on different platforms, you just force the source code through a compiler dedicated to the Chip and the ISA it understands. So getting Windows 10 to work on ARM is as simple as optimising the code through an ARM compiler. The only drawback is the speed at wheich it runs.