PCI SIG Preps CopprLink Cables for PCIe 5.0 and PCIe 6.0, Reveals Specs

CopprLink to replace OCuLink.

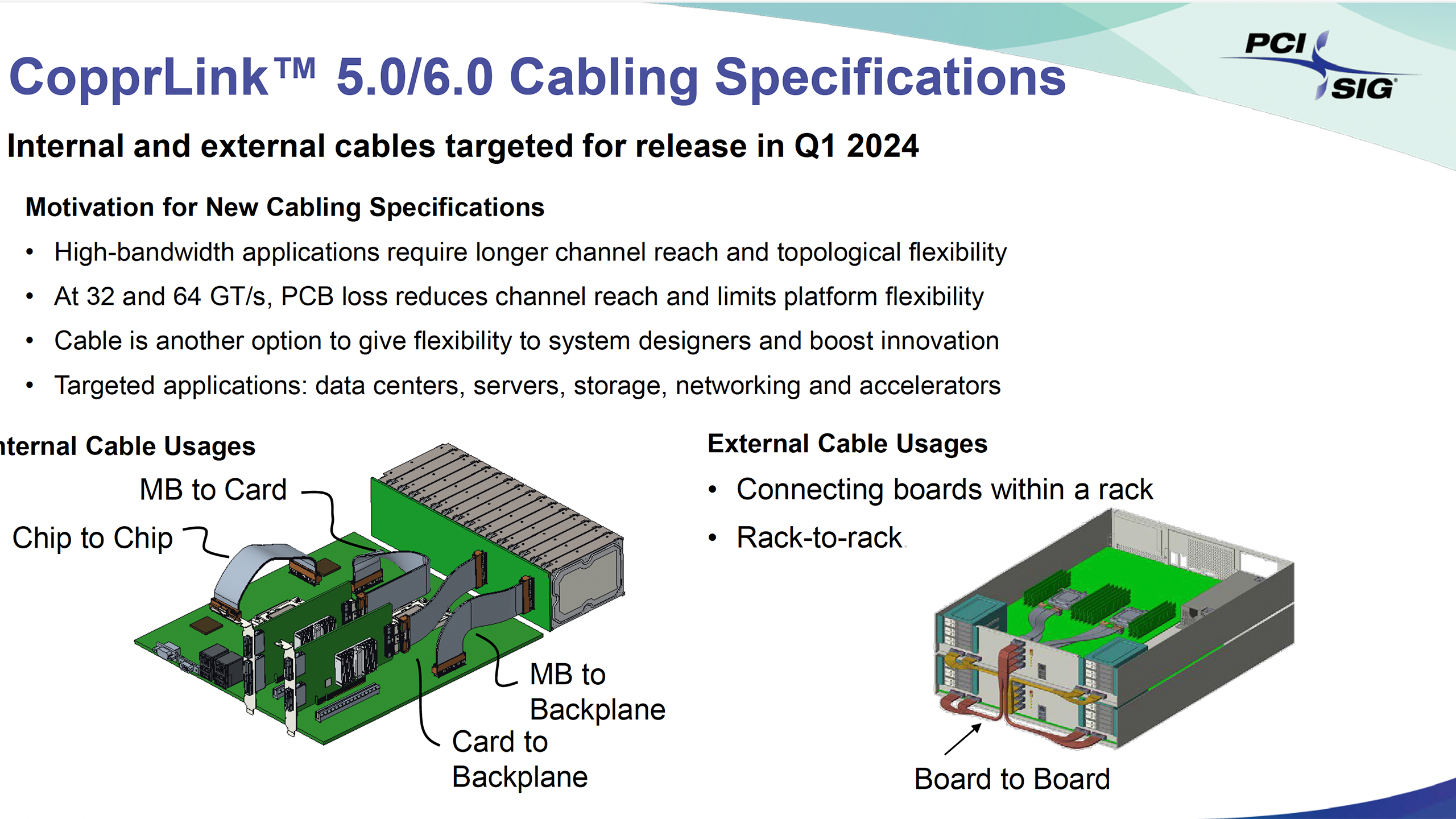

PCI SIG said this week that that it is developing cabling specifications for PCIe 5.0 and PCIe 6.0 interfaces at 32 GT/s and 64 GT/s data transfer rates. The new cable specifications will be release in Q1 2024 and will be branded CopprLink, possibly to avoid any confusion with existing OCuLink cables and also to emphasize their copper nature.

The CopprLink 5.0 and 6.0 specifications are designed for datacenters and servers. They are meant to connect motherboards to backplanes, cards to backplanes, motherboards to expansion cards (e.g., accelerators), racks to racks, boards to boards within a rack, and even chips to chips at PCIe 5.0 (32 GT/s) and PCIe 6.0 (64 GT/s) speeds. The aim is to provide some additional flexibility to cases where typical PCIe links over printed circuit boards are inefficient or cannot be established for some reason. The mentioned cases do not include long-range connections, so we are probably talking about tens of centimeters here.

Running data at 32 GT/s or 64 GT/s over cables is a difficult endeavor due to noise and signal loss, but in many cases cable usage is inevitable, which is why the industry is developing CopprLink. It is noteworthy that PCI SIG only mentions datacenter-grade applications, and not client PCs or automotive applications. Perhaps, CopprLink will eventually be adopted for these applications as well (because why not?), but for now PCI SIG does not mention them.

Another thing to note about CopprLink is that the name implies copper cables, not optical interconnections, which is another specification that PCI SIG is developing. That said, we can't exclude the possibility that at some point someone will build CopprLink with optical interconnections for longer-range connections if there is need and optical PCIe specification is not ready.

Ubiquity of PCIe interface requires constant evolution, not only for the standard itself, but also for its cabling specs. There are PCIe protocol-based Thunderbolt and USB4 technologies for consumer applications and there's OCuLink for internal and external PCIe 3.0 and PCIe 4.0 cabled connections for servers and workstations. CopprLink is a natural addition to the established family of PCIe-based interconnects.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

Amdlova Will have small traces... pcie 4.0 and pcie 5.0 it's a nightmare for board design.Reply

Pcie 6 will be next level of challenge. -

Li Ken-un Reply

PCIe 6.0 won’t be any more challenging than PCIe 5.0 with regards to wiring. They have the same reach. PCIe 7.0 on the other hand…Amdlova said:Will have small traces... pcie 4.0 and pcie 5.0 it's a nightmare for board design.

Pcie 6 will be next level of challenge. -

bit_user Reply

PCIe 6.0 does require a higher signal-to-noise ratio, however. I wouldn't be so dismissive of the challenges, nor the costs of addressing them.Li Ken-un said:PCIe 6.0 won’t be any more challenging than PCIe 5.0 with regards to wiring. They have the same reach. PCIe 7.0 on the other hand…